Untersuchungen zu schnelleren Berechnungsverfahren innerhalb von ARTM mithilfe von Parallelisierung

Untersuchungen zu schnelleren Berechnungsverfahren innerhalb von ARTM mithilfe von Parallelisierung

**Abschlussbericht**

Karsten Spieker Robert Hanfland

Oktober 2025

#### **Anmerkung:**

Das diesem Bericht zugrunde liegende Eigenforschungsvorhaben wurde mit Mitteln des Bundesministeriums für Umwelt, Klimaschutz, Naturschutz und nukleare Sicherheit (BMUKN) unter dem Förderkennzeichen 3624S72523 durchgeführt.

Die Verantwortung für den Inhalt dieser Veröffentlichung liegt bei der GRS.

Der Bericht gibt die Auffassung und Meinung der GRS wieder und muss nicht mit der Meinung des BMUKN übereinstimmen.

GRS - 820 ISBN 978-3-911727-13-6

# Kurzfassung

Dieses Eigenforschungsvorhaben hatte den Kompetenzaufbau der GRS bezüglich der nachträglichen Parallelisierung komplexer Simulations- und Modellierungsprogramme zum Ziel. Der Kompetenzaufbau erfolgte beispielhaft am Simulationsprogramm ARTM, da dafür bereits eine breite Expertise des Programmablaufs bei der GRS besteht. Nach einer Diskussion über die grundlegenden parallelen Hardware-Architekturen, den in anderen Atmosphärischen Ausbreitungsmodellen verwendeten Parallelisierungsstrategien und einigen gängigen parallelen Programmiermodellen wurde der Quellcode analysiert, um geeignete Stellen für eine Parallelisierung in ARTM und TALdia zu identifizieren. Aus den gewonnenen Erkenntnissen wurde ein Konzept zur Parallelisierung der Simulationsprogrammbestandteile erarbeitet und umgesetzt. Aufgetretene Probleme und Besonderheiten, die bei der Umarbeitung eines sequenziellen in ein paralleles Programm auftraten, wurden diskutiert. Aus den Ergebnissen der Umarbeitung ließ sich der prognostizierte Anpassungsbedarf für komplexe Simulations- und Modellierungsprogramme im Allgemeinen und der für ARTM und TALdia im Speziellen ableiten. Hauptaugenmerk ist demnach auf die Verwendung von für den parallelen Programmablauf geeignete Speicherstrukturen und die Einhaltung des EVA-Prinzips zu legen. Die erfolgte Parallelisierung von ARTM und TALdia ergab eine reale Verkürzung der Rechenzeit um einen Faktor 3 – 4 auf einem handelsüblichen Laptop.

## **Abstract**

This research project aimed to systematically enhance the expertise of the GRS in the parallelization of complex simulation and modeling software. The ARTM simulation program was selected as a representative case study, given GRS's extensive prior knowledge of its internal structure and computational workflow. The project commenced with a comprehensive review of fundamental parallel hardware architectures, parallelization strategies employed in other atmospheric dispersion models, and widely used parallel programming paradigms. Subsequently, the source code of ARTM and TALdia was analyzed to identify code segments amenable to parallel execution. Based on the insights gained, a structured concept for the parallelization of key components within the simulation programs was developed and implemented. Challenges and specific issues encountered during the transformation from a sequential to a parallel program were systematically examined and documented.

The outcomes of this transformation enabled the derivation of general adaptation requirements for complex simulation and modeling software, as well as specific recommendations for ARTM and TALdia. Particular emphasis was placed on the use of memory structures suitable for parallel execution and strict adherence to the input–processing–output (IPO) principle. The implemented parallelization of ARTM and TALdia resulted in a reduction in computation time by a factor of 3 to 4 on a standard consumer-grade laptop.

# Inhaltsverzeichnis

|       | Kurzfassung                                                      | I   |

|-------|------------------------------------------------------------------|-----|

|       | Abstract                                                         | III |

| 1     | Einleitung                                                       | 1   |

| 2     | Begriffserklärung                                                | 3   |

| 3     | Arbeitspaket 1: Recherche zu hardwarenahen Parallelisierungs-    | 9   |

| 3.1   | Grundlegende Rechnerarchitektur                                  | 9   |

| 3.2   | CPU-Parallelisierung                                             | 10  |

| 3.3   | GPU-Beschleunigung                                               | 13  |

| 3.4   | Verteiltes Rechnen                                               | 15  |

| 3.5   | Parallelisierung in ARTM und ähnlichen Lagrange-Partikelmodellen | 18  |

| 3.5.1 | ARTM                                                             | 18  |

| 3.5.2 | MPTRAC                                                           | 19  |

| 3.5.3 | FLEXPART                                                         | 22  |

| 3.5.4 | PALM                                                             | 24  |

| 3.5.5 | HYSPLIT                                                          | 24  |

| 3.5.6 | Parallel Micro-SWIFT-SPRAY (PMSS)                                | 26  |

| 3.5.7 | Zusammenfassung                                                  | 28  |

| 3.6   | Zusammenfassung                                                  | 30  |

| 4     | Arbeitspaket 2: Recherchen zu möglichen Bibliotheken, Compi-     |     |

|       | lern, Grafikkarten und deren Anwendbarkeit für ARTM              | 33  |

| 4.1   | OpenMP (Open Multi Processing)                                   | 33  |

| 4.2   | MPI (Message Passing Interface)                                  | 34  |

| 4.3   | OpenCL (Open Computing Language)                                 | 36  |

| 4.4   | OpenACC (Open Accelerators)                                      | 37  |

| 4.5   | Parallele Programmierungsmodelle der Grafikkartenhersteller      | 38  |

| 4.5.1 | CUDA von NVIDIA                                                                          | 39         |

|-------|------------------------------------------------------------------------------------------|------------|

| 4.5.2 | ROCm/HIP von AMD                                                                         | 39         |

| 4.6   | Kokkos                                                                                   | 40         |

| 4.7   | Zusammenfassung                                                                          | 41         |

| 5     | Arbeitspaket 3: Identifikation möglicher Stellen innerhalb des                           |            |

|       | Quellcodes von ARTM für eine Parallelisierung                                            | 43         |

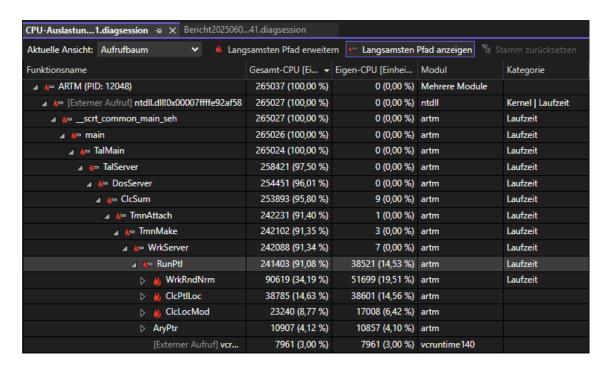

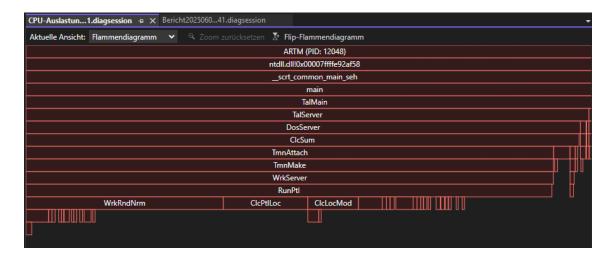

| 5.1   | Laufzeitmessung von Funktionen im Transportmodell von ARTM                               | 43         |

| 5.2   | Analyse des Programmablaufs des Transportmodells von ARTM                                | 47         |

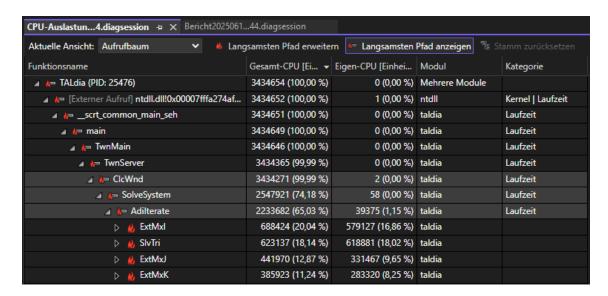

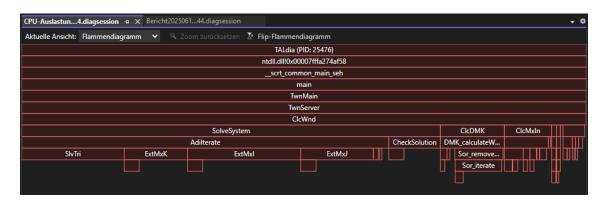

| 5.3   | Laufzeitmessung von Funktionen in TALdia                                                 | 48         |

| 5.4   | Analyse des Programmablaufs von TALdia                                                   | 52         |

| 5.5   | Konzept zur Parallelisierung von ARTM                                                    | 53         |

| 5.5.1 | Parallelisierungsansatz für das Transportmodell von ARTM                                 | 54         |

| 5.5.2 | Parallelisierungsansatz für das Windfeldmodell TALdia                                    | 55         |

| 5.6   | Zusammenfassung                                                                          | 56         |

| 6     | Arbeitspaket 4: Analyse von Implementierungsmethoden und dar-                            | •          |

|       | aus folgender Anpassungsbedarf in ARTM                                                   | 59         |

| 6.1   | Umsetzung der Parallelisierung in ARTM auf der Ebene der Teilchen-                       |            |

|       | propagation                                                                              | 59         |

| 6.1.1 | Allgemeine Anpassungen und Bereitstellung der parallelen Umgebung                        | 59         |

| 6.1.2 | Vermeidung von False-Sharing                                                             | 62         |

| 6.1.3 | Vermeidung von Race-Bedingungen                                                          | 65         |

| 6.2   | Umsetzung der Parallelisierung von TALdia                                                | 68         |

| 6.2.1 | Umwandlung von globalen Variablen in threadspezifische globale Vari-                     |            |

|       | ablen                                                                                    | 69         |

| 6.2.2 | Synchronisierung von Programmabläufen                                                    | 69         |

| 6.2.3 | Änderungen der allgemeinen Datenhaltung von ARTM für eine paral- lele Programmausführung | 71         |

| 0.0   |                                                                                          | / 1        |

| 6.3   | Vergleich der sequenziell und parallel berechneten Simulationsergebnisse                 | 72         |

| 6.3.1 | Vergleich der Ergebnisse der ARTM Simulationen                                           |            |

| 6.3.2 |                                                                                          |            |

| U.J.Z | Vergleich der Windfelder                                                                 | <i>i</i> 3 |

| 6.4   | nahmen                                                                  | 75 |

|-------|-------------------------------------------------------------------------|----|

| 6.4.1 | Laufzeitverkürzung durch Parallelisierung des Transportmodells von ARTM | 75 |

| 6.4.2 | Laufzeitverkürzung durch Parallelisierung von TALdia                    | 79 |

| 6.5   | Prognostizierter Anpassungsbedarf für das Beispielprogramm ARTM         | 80 |

| 6.6   | Zusammenfassung                                                         | 81 |

| 7     | Zusammenfassung                                                         | 83 |

|       | Literaturverzeichnis                                                    | 85 |

|       | Abbildungsverzeichnis                                                   | 93 |

|       | Tabellenverzeichnis                                                     | 95 |

|       | Abkürzungsverzeichnis                                                   | 97 |

# 1 Einleitung

Die steigende Komplexität von Simulation und Modellierung im Bereich der Forschung, z. B. in der numerische Strömungsmechanik oder auch der Dispersionsmodellierung, sowie das weitere Voranschreiten von maschinellem Lernen und künstlichen Intelligenzen geht stets mit einer erhöhten Programmlaufzeit einher. Aus diesem Grund ist es unabdingbar, schnellere Berechnungsverfahren zu verfolgen. In den letzten Jahren wurde auch das "General Purpose Computation on Graphics Processing Unit" (GPGPU) intensiv verfolgt. Weitere Berechnungsverfahren zum Beschleunigen der Laufzeit sind die Parallelisierungen über Mehrkernprozessoren, den heute üblichen zentralen Berechnungseinheiten (engl. "central processing units" (CPUs)), sowie das verteilte Rechnen.

Mit dem Ziel, die Kompetenz der GRS im Bereich der Parallelisierung von Simulationsund Modellcodes zu erweitern, sollen deshalb exemplarisch anhand des ARTM (Atmosphärisches Radionuklid Transport-Modell) die gängigsten Parallelisierungsmöglichkeiten untersucht werden. Die Untersuchung mittels ARTM eignet sich aufgrund dessen

Entwicklung als Open Source-Projekt. Ebenso wird ARTM vom Bundesamt für Strahlenschutz (BfS) verwendet und einem breiten Kreis von Anwenderinnen und Anwendern zur

Verfügung gestellt. Der Kompetenzaufbau der GRS in der Weiterentwicklung und Anwendung von ARTM ist somit von großem Interesse für die Allgemeinheit. Des Weiteren

basiert ARTM auf einem Lagrange-Partikelmodell und eignet sich insbesondere durch

den Transport von Simulationspartikeln sehr gut für die Untersuchung der unterschiedlichen Berechnungsverfahren. Zuletzt wird für den sehr komplexen Einbau der Parallelisierungsmöglichkeiten verlangt, dass ein sehr gutes Verständnis in die innere Struktur

des zu parallelisierenden Programms vorliegen muss.

Im Eigenforschungsvorhaben wird deshalb der internationale Stand von Wissenschaft und Technik zur Parallelisierung von Lagrange-Partikelmodellen oder ähnlichen Ausbreitungsmodellen recherchiert und bewertet. Des Weiteren wird eine Recherche zu hardwarenahen Parallelisierungsmöglichkeiten und dazu passenden Bibliotheken, Kompilierern und Grafikkarten (bei GPU-Parallelisierung) durchgeführt. Basierend auf diesen Erkenntnissen sowie der Sicherstellung der Übergabe aller notwendigen Informationen an weitere Prozesse, werden mögliche Stellen innerhalb des Quellcodes von ARTM für eine Parallelisierung identifiziert. In einem letzten Schritt werden mögliche Implementierungsmethoden und dafür notwendige Anpassungen in ARTM analysiert. Ziel ist, das Grundkonzept von ARTM so wenig wie möglich anzupassen, so dass die über die Jahre aufgebaute Kompetenz erhalten bleibt.

Dieser Abschlussbericht ist in folgende Teile unterteilt. In Kapitel 2 werden einige wichtige Fachbegriffe erläutert, die in diesem Bericht Verwendung finden. Anschließend werden in Kapitel 3 grundlegende Rechner- und Speicherarchitekturen diskutiert, die für die Konzepte der parallelen Programmierung von Bedeutung sind. In Kapitel 4 werden verschiedene parallele Programmiermodelle vorgestellt, die für die Parallelisierung von ARTM in Betracht kommen könnten. Kapitel 5 beschäftigt sich mit der Identifikation möglicher Stellen innerhalb des Quellcodes von ARTM/TALdia für eine Parallelisierung, während das Kapitel 6 in Detail mögliche Implementierungsmethoden und erste Ergebnisse einer parallelisierten Version von ARTM/TALdia präsentiert. Anschließend werden die Ergebnisse des Eigenforschungsvorhabens in Kapitel 7 zusammengefasst.

# 2 Begriffserklärung

Tab. 2.1

Überblick über relevante Begriffe innerhalb dieses Dokuments

| Begriff deutsch          | Begriff englisch          | Erklärung/Bedeutung                                                                                                                                                                   | Quelle   |

|--------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Teilaufgaben             |                           | Eine auszuführende Aufgabe (z. B. Matrixmultiplikation) wird in Teilaufgaben zerlegt.                                                                                                 | /RAU 07/ |

| Prozesse, Threads, Tasks | Processes, Threads, Tasks | Teilaufgaben werden als Prozesse, Threads oder Tasks bezeichnet, wobei sich die Bedeutungen für unterschiedliche Programmiermodelle und -umgebungen geringfügig unterscheiden können. | /RAU 07/ |

|                          |                           | Thread Meist als Bezeichnung für Teilaufgaben verwendet, die auf einen gemeinsamen Adressraum zugreifen.                                                                              |          |

|                          |                           | Prozess Meist als Bezeichnung für Teilaufgaben verwendet, die auf den <i>privaten</i> Bereich eines <i>verteilten Adressraums</i> zugreifen.                                          |          |

| Prozessor                | Processor                 | Eine unabhängige physikalische Berechnungseinheit.<br>Das können sowohl Prozessoren sein als auch Prozessorkerne bei Multi-Prozessoren.                                               | /RAU 07/ |

| Berechnungsstrom         |                           | Das ist eine Teilaufgabe.                                                                                                                                                             | /RAU 07/ |

| Mapping                  | Mapping                   | Mapping ist das Abbilden von Teilaufgaben auf physikalische Berechnungseinheiten.                                                                                                     | /RAU 07/ |

| Synchronisation          | Synchronisation           | Prozess zum Informationsaustauch zwischen Berechnungsströmen (Teilaufgaben).                                                                                                          | /RAU 07/ |

| Kostenmaß                |                           | Maß zur Bewertung der Ausführungszeit eines paral-<br>lelen Programms                                                                                                                 | /RAU 07/ |

| Begriff deutsch                         | Begriff englisch                             | Erklärung/Bedeutung                                                                                                                                                                                                                                                                                                                      | Quelle               |

|-----------------------------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Parallele Laufzeit                      | Parallel run time                            | Die parallele Laufzeit setzt sich aus der Zeit, während der Berechnungsströme parallel ablaufen, und der Zeit für Informationsaustauch/Synchronisation zusammen.                                                                                                                                                                         | /RAU 07/             |

| Lastgleichgewicht                       | Load balancing                               | Verteilung der Rechenlast auf die beteiligten Prozessoren                                                                                                                                                                                                                                                                                | /RAU 07/             |

| Granularität                            | Granularity                                  | Durchschnittliche Größe der Teilaufgaben, in die eine Aufgabe zerlegt wird (z. B. gemessen als Anzahl der Instruktionen)                                                                                                                                                                                                                 | /RAU 07/             |

| Scheduling                              | Scheduling                                   | Entscheidungsvorgang, in welcher Reihenfolge die Teilaufgaben, unter Berücksichtigung von Abhängigkeiten, abgearbeitet werden                                                                                                                                                                                                            | /RAU 07/             |

| UMA-System (Uniform Memory Access)      | UMA-System (Uniform Memory Access)           | Einheitliche Speicherzugriffszeit für alle Prozessoren<br>bei einer gemeinsamen Speicher-Architektur ("shared<br>memory"). Häufigster Vertreter ist der Symmetric Mul-<br>tiprocessor (SMP) Rechner.                                                                                                                                     | /RAU 07/<br>/BAR 17/ |

| NUMA-System (Non-Uniform Memory Access) | NUMA-System (Non-Uni-<br>form Memory Access) | Die Speicherzugriffszeit eines Prozessors hängt von der relativen Speicherstelle ab.                                                                                                                                                                                                                                                     | /RAU 07/<br>/BAR 17/ |

| Verschränktes Multithreading            | Interleaved Multithreading                   | Ein physikalischer Prozessor wird in eine feste Anzahl virtueller Prozessoren unterteilt. Nach jedem Maschinenbefehl findet ein expliziter Wechsel zum nächsten virtuellen Prozessor statt. Dadurch führt gleichzeitig zur Speicherzeit des ersten virtuellen Prozessors der zweite virtuelle Prozessor seinen Maschinenbefehl aus, usw. | /RAU 07/             |

| , | - |

|---|---|

| L |   |

| Begriff deutsch                 | Begriff englisch                  | Erklärung/Bedeutung                                                                                                                                                                                                                                                                                                                                                                                              | Quelle   |

|---------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Simultanes Multithreading (SMT) | Simultaneous Multithreading (SMT) | Ein physikalischer Prozessor ist hardwareseitig in logische Prozessoren unterteilt, d. h. bestimmte Steuerungseinheiten des Prozessors sind mehrfach vorhanden. Threads laufen auf einem logischen Prozessor. Fällt ein Thread/logischer Prozessor in einen Wartezustand, etwa wegen Kommunikation mit dem Speicher, übernimmt ein anderer Thread/logischer Prozessor (wird auch als Hyperthreading bezeichnet). | /RAU 07/ |

| Cache-Speicher                  | Cache                             | Kleine, schnelle Speicher, die zwischen Prozessor und Hauptspeicher geschaltet sind                                                                                                                                                                                                                                                                                                                              | /RAU 07/ |

| Cache-Kohärenz                  | Cache coherence                   | Speicher- bzw. Cache-Kohärenz liegt vor, wenn jeder Prozessor das <i>gleiche eindeutige</i> Bild des Speichers hat.                                                                                                                                                                                                                                                                                              | /RAU 07/ |

| Rechnersystem                   | Computer system                   | Gesamtheit der Hard- und Software, die dem Programmierer zur Verfügung steht und seine "Sicht" auf den Rechner bestimmt                                                                                                                                                                                                                                                                                          | /RAU 07/ |

| Zentraleinheit                  | Central Processing Unit (CPU)     | Die eigentliche Berechnungseinheit. Die CPU enthält zwei weitere Hauptkomponenten, nämlich die Kontrolleinheit (engl. "control unit") und die "arithmetic logic unit" (ALU).                                                                                                                                                                                                                                     | /RAU 07/ |

| Knoten                          | Node                              | Ein eigenständiger "Computer in der Box". Knoten sind miteinander vernetzt und bilden einen Supercomputer.                                                                                                                                                                                                                                                                                                       | /BAR 17/ |

| Kontrolleinheit                 | Control unit                      | Die Kontrolleinheit sorgt dafür, dass die Maschinen-<br>befehle und Daten aus dem Speicher geladen wer-<br>den und koordiniert deren sequenzielle Abarbeitung<br>in der ALU.                                                                                                                                                                                                                                     | /RAU 07/ |

| 5 | • |

|---|---|

| Begriff deutsch               | Begriff englisch            | Erklärung/Bedeutung                                                                                                                                                                                                                                                                                                                                   | Quelle            |

|-------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Arithmetisch-logische Einheit | Arithmetic logic unit (ALU) | Die ALU führt entsprechend den Maschinenbefehlen grundlegende arithmetische Operationen mit den geladenen Daten durch.                                                                                                                                                                                                                                | /RAU 07/          |

| Stream-Verarbeitung           | Stream processing           | Bei der Stream-Verarbeitung handelt es sich um die kontinuierliche Verarbeitung neuer Datenereignisse, sobald diese empfangen werden.                                                                                                                                                                                                                 | /NVI 24a/         |

| Prozessorkern                 | Processing core             | Eine unabhängige Berechnungseinheit, die die wesentlichen Elemente zur Abarbeitung von Maschinenbefehlen (Kontrolleinheit und Arithmetisch-logische Einheit) enthält. Bei einem Ein-Kern-Prozessor stellt im Wesentlichen die CPU den Kern dar. Bei Mehrkernprozessoren sind auf der CPU mehrere Kerne mit einer zugehörigen Steuereinheit enthalten. |                   |

| Adressraum                    | Address space               | Die Menge aller zulässigen Adressen im gesamten Speicher, die einer Anwendung zugeordnet sind                                                                                                                                                                                                                                                         |                   |

| Programmiermodell             | Programming model           | Die Gesamtheit aller Grundprinzipien und Schnittstellen, über die der Entwickler die Ressourcen der Maschine ansteuern kann. Sie definiert also die Sicht des Programmierers auf die Maschine und wie der Programmierer diese ansprechen kann.                                                                                                        |                   |

| Overhead                      | Overhead                    | Die Gesamtheit aller zusätzlichen Arbeiten, die da-<br>durch entstehen, dass ein Programm nicht mehr se-<br>quenziell, sondern parallel abläuft                                                                                                                                                                                                       | /UNI 20/          |

| Amdahlsches Gesetz            | Amdahls law                 | Das Amdahlsche Gesetz beschreibt den Zusammenhang zwischen den sequenziellen und parallelen Anteilen sowie der Anzahl der <i>Prozessorkerne</i> und der potenziellen Beschleunigung eines Programms.                                                                                                                                                  | /TRO 18/,/RAU 07/ |

| Begriff deutsch  | Begriff englisch | Erklärung/Bedeutung                                                                                                                                                                                                                                                                                                                                                             | Quelle    |

|------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Aufrufstapel     | Call stack       | Der Aufrufstapel, oft auch nur als "Stack" bezeichnet, ist ein Speicherbereich für Funktionen im Hauptspeicher. Hier werden nacheinander die Funktionen, ihre Variablen und Anweisungen abgelegt. Die Funktionen, die als letztes begonnen wurden, werden als erstes wieder beendet.                                                                                            | /WOL 19/  |

| Allokation       | allocation       | Dt.: Zuweisung. Bei einer Speicherallokation wird einer Variablen ein Speicherbereich dynamisch, d. h. zur Laufzeit, zugewiesen.                                                                                                                                                                                                                                                | /WOL 19/  |

| Struktur         | struct           | In einer Struktur können Variablen mit verschiedenen Datentypen zusammengefasst werden. Dies unterscheidet sie von Feldern (engl. "arrays"), bei denen nur Variablen desselben Datentyps verwendet werden.                                                                                                                                                                      | /WOL 19/  |

| Verkettete Liste | Linked list      | Eine verkettete Liste ist eine Datenstruktur, in der verschiedene Datentypen dynamisch, d. h. zur Laufzeit, gespeichert werden können. Dabei ist jeder Listeneintrag durch seine Nachbarn, also den Vorgänger und den Nachfolger, eindeutig in der Liste eingeordnet.                                                                                                           | /HAK 04/  |

| Stalls           | Stalls           | Moderne CPUs führen Befehle nicht strikt nacheinander, sondern in einer Pipeline und oft out-of-order aus. Im Idealfall ist die Pipeline voll, und jede Taktung erledigt nützliche Arbeit. Ein Stall tritt auf, wenn die Pipeline wartet, weil eine Ressource fehlt oder irgendeine Abhängigkeit nicht erfüllt ist. In solchen Fällen taktet der Kern, aber macht keine Arbeit. | /INT 25a/ |

| Retiring         | Retiring         | Das "Retiring" ist der prozentuale Anteil der Takte, in denen die CPU nützliche Instruktionen fertig ausgeführt hat.                                                                                                                                                                                                                                                            | /INT 25a/ |

# 3 Arbeitspaket 1: Recherche zu hardwarenahen Parallelisierungsmöglichkeiten

Parallelisierung kann auf verschiedenste Weisen klassifiziert werden, die auf unterschiedlichen Eigenschaften der Rechnersysteme, also der Kombination aus Hardwareund Softwarekomponenten, beruhen. Das können z. B. die Flynnsche Klassifizierung<sup>1</sup>, die auf einer Quantifizierung von Befehls- und Datenströmen basiert, die Speicherorganisation oder die Verbindungsnetzwerkklassifikation sein /RAU 07/. Im Folgenden wird keine bestimmte Klassifizierung zur Strukturierung verwendet. Stattdessen werden wichtigen Architektur- und Bauteileigenschaften berücksichtigt, die in der praktischen Anwendung der parallelen Programmierung von Bedeutung sind. Daher wird in den folgenden Abschnitten auf Systeme mit gemeinsamem Speicher (engl. "shared memory systems"), Systeme mit verteiltem Speicher (engl. "distributed systems") und Grafikprozessoreinheiten (engl. "graphic processor units" (GPU)) eingegangen /TRO 18/.

Darüber hinaus werden typische Aufgaben genannt, die für eine Parallelisierung auf den unterschiedlichen Systemen besonders geeignet sind. Es gibt allerdings auch Aufgaben, die gar nicht parallelisierbar sind. Dabei handelt es sich um Aufgaben, die von den Ergebnissen der vorherigen Berechnung abhängen, wie es z. B. bei manchen iterativen Algorithmen der Fall ist. Diese Probleme weisen eine Zeitabhängigkeit oder Kausalität auf und sind daher nicht parallelisierbar /NAV 14/.

## 3.1 Grundlegende Rechnerarchitektur

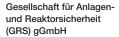

Heutzutage funktionieren die meisten Prozessoren nach der Von-Neumann Architektur /COO 12/, /BAR 17/. Dieser Aufbau besteht im Wesentlichen aus drei Teilen, dem Speicher, der eigentlichen Zentraleinheit oder zentralen Berechnungseinheit (engl. "central processing unit" (CPU)) und einer Schnittstelle für die Ein- und Ausgabe. Eine schematische Darstellung ist in Abb. 3.1 abgebildet. Die CPU enthält zwei weitere Hauptkomponenten, nämlich die Kontrolleinheit (engl. "control unit") und die arithmetisch-logische Einheit (engl. "arithmetic logic unit" (ALU)). Maschinenbefehle und Daten sind in einem elektronischen Speicher abgelegt. Die Kontrolleinheit sorgt dafür, dass die Maschinen-

\_

Theoretische Klassifizierung, die am Anfang der Parallelrechnungsentwicklung stand. Rechner werden in Single Instruction Single Data (SISD), Multiple Instructions Single Data (MISD), Single Instruction Multiple Data (SIMD) und Multiple Instructions Multiple Data (MIMD) unterteilt /RAU 07/.

befehle und Daten aus dem Speicher geladen werden und koordiniert deren sequenzielle Abarbeitung in der ALU. Die ALU führt entsprechend den Maschinenbefehlen grundlegende arithmetische Operationen mit den geladenen Daten durch. Die Ein- und Ausgabe stellt die Schnittstelle zum Menschen dar. Auch parallele Rechner folgen immer noch diesem grundlegenden Aufbau, allerdings mit einer Vielzahl von Berechnungseinheiten /BAR 17/.

**Abb. 3.1** Schematische Darstellung einer zentralen Berechnungseinheit nach der Von-Neumann Architektur

In der Abbildung ist die zentrale Berechnungseinheit (CPU) mit der enthaltenen Kontrolleinheit und der arithmetisch-logische Einheit (engl. "arithmetic logic unit" (ALU)) dargestellt. Der elektronische Speicher tauscht Informationen mit der Kontrolleinheit und der ALU aus. Die Ein- und Ausgabe stellt die Schnittstelle zum Menschen dar. In der Darstellung stellt die Einheit aus Kontrolleinheit und die ALU den Prozessorkern dar /BAR 17/.

#### 3.2 CPU-Parallelisierung

Unter CPU-Parallelisierung versteht man die Parallelisierung durch Multicore-Prozessoren. Dabei werden mehrere Prozessorkerne auf einem Prozessorchip platziert. Jeder Prozessorkern stellt einen logischen Prozessor dar, der separat z. B. vom Betriebssystem oder einem Programm angesteuert werden kann /RAU 07/.

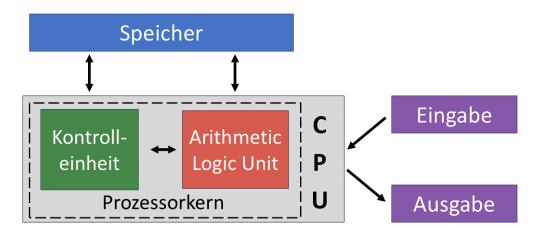

Solche Multicore-Prozessoren werden als "shared memory" Systeme bezeichnet /TRO 18/, sie besitzen also einen gemeinsamen Speicher, den sich alle Prozessorkerne teilen. In der Praxis wird allerdings häufig jedem Prozessorkern ein bestimmter Cache-Speicher (L1-Cache) privat, d. h. exklusiv, zugeordnet. Durch den gemeinsamen Speicher sind Änderungen an einer Speicheradresse automatisch für alle Prozessorkerne sichtbar. Dabei kann die genaue Speicherarchitektur bei unterschiedlichen Multicore-

Prozessoren variieren (hierarchisches, Pipeline- oder netzwerkbasiertes Design). Die häufigsten Multicore-Prozessoren gehören zur Familie der symmetrischen Multiprozessoren (SMPs) und sind nach dem "Uniform Memory Access" (UMA)-System entworfen. Eine schematische Darstellung dieser Speicherarchitektur ist in Abb. 3.2 gegeben /RAU 07/, /BAR 17/. Hierbei haben die Prozessorkerne einen physikalisch gemeinsamen Speicher. Das UMA-System wird manchmal auch als Cache Kohärentes UMA-System (engl. "Cache Coherent-UMA" (CC-UMA)) bezeichnet. Die Cache-Kohärenz wird hardwareseitig realisiert und bedeutet, dass jeder Prozessorkern zu jeder Zeit dasselbe Speicherabbild sieht, wie alle anderen Prozessorkerne. Das bezieht auch die privaten Cache-Speicher mit ein. Durch diese Speicherarchitektur ist sichergestellt, dass jeder Prozessorkern die gleichen Speicherzugriffszeiten aufweist /BAR 17/.

**Abb. 3.2** Schema eines UMA-Systems als Repräsentant der "shared memory" Architektur

Alle Prozessorkerne haben einen gemeinsamen Speicher /BAR 17/.

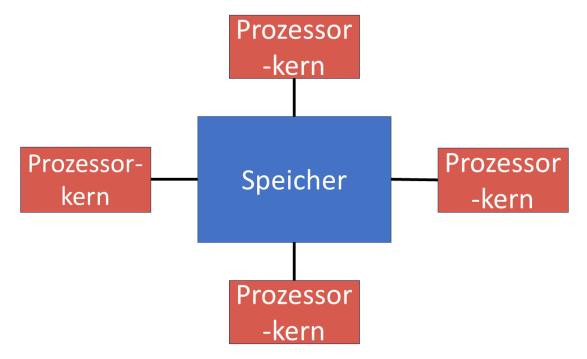

Eine weitere Speicherarchitektur von Multicore-Prozessoren stellt das "Non-Uniform Memory Access" (NUMA)-System dar. Hierbei wird der physikalisch gemeinsame Speicher durch Verbindungsleitungen zwischen Speicherbereichen realisiert /BAR 17/. Dabei befinden sich alle Prozessorkerne und Speicherbereiche immer noch auf demselben Chip /RAU 07/. Diese Speicherarchitektur ist in Abb. 3.3 dargestellt. Multicore-Prozessoren dieser Architektur werden oft durch die Kombination von zwei oder mehr SMPs realisiert. Ein Merkmal dieser Speicherarchitektur ist, dass nicht alle Prozessorkerne die gleichen

Speicherzugriffszeiten haben, je nachdem, wo die gewünschte Information gespeichert ist. Der Speicherzugriff über die Verbindungsleitung ist langsamer als der Speicherzugriff zum lokalen Speicher. Cache-Kohärenz ist nicht automatisch gegeben. Systeme, die diese bieten, werden als "Cache Coherent-NUMA" (CC-NUMA) -Systeme bezeichnet /BAR 17/.

**Abb. 3.3** Schema eines NUMA-Systems als Repräsentant der "shared memory" Architektur

Mehrere Prozessor-Speichereinheiten werden durch eine Verbindungsleitung auf einem Chip verbunden /BAR 17/.

Die parallele Programmierung mit Prozessoren bietet eine Reihe von Vorteilen. Durch den globalen, gemeinsamen Adressraum ergibt sich eine benutzerfreundliche Perspektive auf den Speicher. Zudem läuft das Teilen von Daten schnell und einheitlich ab. Speicherkonflikte, wie der schreibende Zugriff von zwei Prozessorkernen auf dieselbe Speicheradresse, werden auf der Ebene der Programmiermodelle (siehe Kapitel 4) verhindert. Außerdem wird der Speicherplatz effizient ausgenutzt, da das Duplizieren von Daten wegen des gemeinsamen Speichers kaum nötig ist /RAU 07/, /BAR 17/. Ein Nachteil dieser Speicherarchitektur ist, dass sie nicht beliebig skalierbar ist. Der Datenverkehr zwischen dem Prozessorkern und dem Speicher kann überproportional zur Anzahl der Prozessorkerne steigen. Zudem stellt die Cache-Kohärenz bei Systemen mit vielen Prozessorkernen eine Herausforderung dar /RAU 07/, /BAR 17/.

Zur Umsetzung der Parallelisierung mit Multicore-Prozessoren werden threadbasierte Programmiermodelle angewendet /TRO 18/. Außerdem sind für Multicore-Prozessoren besonders task-parallele Aufgaben geeignet. Bei Ihnen besteht die zu erfüllende Aufgabe aus Teilaufgaben, die unterschiedliche Funktionen darstellen. Um die Gesamtaufgabe zu erfüllen, müssen alle Teilaufgaben/Funktionen auf einen gemeinsamen Strom

von Daten angewendet werden, ohne dass es eine Zeitabhängigkeit gibt. Grund für die besondere Eignung solcher Probleme ist die Architektur von CPUs, die auf jedem Prozessor bzw. Prozessorkern die unabhängige Ausführung einer eigenen Teilaufgabe erlaubt /NAV 14/.

#### 3.3 GPU-Beschleunigung

Um die Laufzeit von rechenintensiven Anwendungen zu beschleunigen, können in vielen Fällen spezielle Bauteile verwendet werden. Ein Vertreter solcher Bauteile sind Grafikkarten. Diese haben zu Beginn des 21. Jahrhunderts den Sprung geschafft von auf Grafikanwendungen spezialisierten Bauteilen hin zu allgemein anwendbaren Grafikprozessoreinheiten /COO 12/.

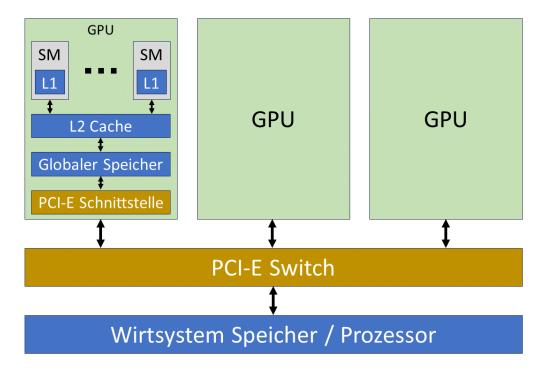

Die Architektur von modernen GPUs ähnelt im Kleinen sehr stark der Architektur von modernen Cluster-Systemen im Großen. Eine schematische Darstellung einer GPU, eingebettet in einem Wirtsystem, ist in Abb. 3.4 gezeigt. Bei GPUs werden die Berechnungseinheiten als "streaming multiprocessors" (SMs) bezeichnet, von denen typischerweise mehrere auf einer Grafikkarte platziert sind. Jeder SM verfügt über einen eigenen L1-Cache, allerdings teilen sich alle SMs einen gemeinsamen L2-Cache, der auch als Datenverbindung zwischen den verschiedenen SMs fungiert. Größere Datenmengen werden in einem nachgeordneten globalen Speicher gehalten. Dieser Speicher ist über eine "Peripheral Component Interconnect Express" (PCI-E) -Schnittstelle mit dem PCI-E Switch des Wirtsystems verbunden. Auf diese Weise erfolgt sowohl die Kommunikation zwischen GPU und Wirtsystem, als auch die Kommunikation zwischen mehreren GPUs /COO 12/. In einem SM sind mehrere "stream processors" (SP) zusammengefasst. Wenn ein SM seine Arbeit aufnimmt, dann wird die gleiche Maschinenbefehlssequenz synchron von allen enthaltenen SPs ausgeführt, wobei jeder SP auf einer/m an-Information/Datum Verhalten deren operiert. Das entspricht also einer Vektorverarbeitungseinheit (engl. "vector-processing unit") und ist analog zum SIMD-Prinzip der Flynnschen Klassifizierung /BAR 23/.

Abb. 3.4 GPU-Architektur eingebettet in ein Wirtsystem mit drei GPUs

Das Wirtsystem ist über ein Verbindungsnetzwerk (PCI-E) mit drei GPUs verbunden. Analog zur Hierarchie der GPUs im Wirtsystem sind auch die einzelnen GPUs aufgebaut. Ein globaler Speicher in der Grafikkarte ist mit einem L2 Cache verbunden. Dieser übernimmt neben der Funktion eines Speichers gleichzeitig auch noch die Funktion eines Verbindungsnetzwerks. Am oberen Ende der Hierarchie stehen mehrere streaming multiprocessors" (SMs), die jeweils über einen eigenen L1 Cache (L1) verfügen.

Der große Vorteil bei der Verwendung von GPUs ist die hohe Rechenleistung, die durch die massive parallele Architektur entsteht. Allerdings ist die Datenhaltung und Partitionierung<sup>2</sup> dem Programmierer überlassen. Zudem muss die Struktur des zu lösenden Problems bzw. der Algorithmus für die Berechnung durch eine GPU geeignet sein, was im Allgemeinen nicht der Fall ist /COO 12/, /PLL 17/.

Um GPUs zur parallelen Berechnung nutzen zu können, sind sogenannte Streaming basierte Programmiermodelle erforderlich. Besonders geeignet für GPUs sind Berechnungen, die sich natürlicherweise in viele unabhängige Teilberechnungen unterteilen lassen, wie z. B. Operationen auf Matrizen oder Probleme aus der Linearen Algebra. Viele solcher Probleme werden als datenparallel bezeichnet. Eine Teilaufgabe wird dabei auf viele unabhängige Daten angewendet. Man spricht bei solchen Aufgaben auch

-

<sup>&</sup>lt;sup>2</sup> Das zerteilen einer Aufgabe in sinnvolle Teilaufgaben.

von "embarrassingly parallel"<sup>3</sup> Aufgaben. Datenparallele Probleme sind ideale Kandidaten für GPUs. Der Grund dafür liegt in der Architektur einer GPU. Sie arbeitet am besten, wenn alle Threads dieselben Befehle abarbeiten, aber auf unterschiedliche Daten /NAV 14/.

#### 3.4 Verteiltes Rechnen

Unter verteiltes Rechnen (engl. "distributed computing") wird im Allgemeinen verstanden, dass Teilaufgaben einer zu lösenden Aufgabe auf verteilten Systemen (engl. "distributed systems") bearbeitet werden. Dieser Aufbau stellt den einfachsten Fall dar, um ein System für das parallele Rechnen bereitzustellen /RAU 07/, /TRO 18/.

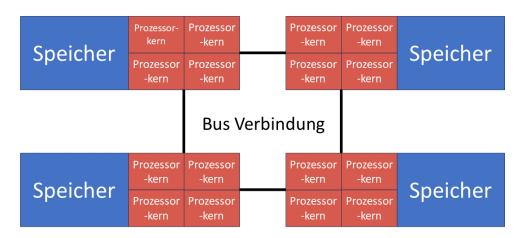

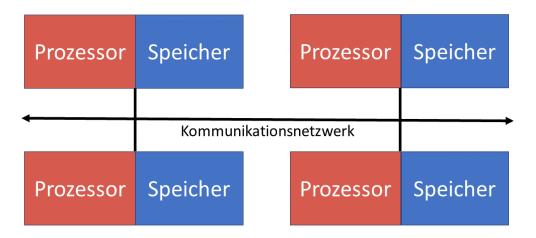

In der ursprünglichen Konfiguration wird bei verteilten Systemen die "distributed memory" Architektur verwendet /TRO 18/. Die genauen Ausprägungen dieser Architektur können variieren, es haben jedoch alle gemeinsam, dass für die Interprozessorkommunikation ein Kommunikationsnetzwerk verwendet wird, wie z. B. Ethernet. Die Abb. 3.5 zeigt eine schematische Darstellung der "distributed memory" Architektur. Jeder Prozessor verfügt über einen lokalen Speicher mit einem eigenen Adressraum. Ein globaler Adressraum, wie bei NUMA-Systemen (vgl. Abb. 3.3), existiert nicht. Da jede Einheit aus Prozessor und Speicher unabhängig von den anderen ist, gibt es keine Cache-Kohärenz. Die Kommunikation zwischen den verschiedenen Einheiten aus Prozessor und Speicher muss vom Programmierer übernommen werden /BAR 17/.

Praktisch lässt sich ein solches System bereits dadurch realisieren, dass mehrere herkömmliche Desktop PCs mit Ein-Kern-Prozessoren über ein Ethernet-Verbindungsnetz miteinander verbunden werden. Dies wurde auch in den Anfängen des parallelen Rechnens so praktiziert /COO 12/.

\_

Der Ausdruck "embarrassingly parallel" (dt. peinlich parallel) bedeutet, dass es peinlich wäre, wenn man die Vorteile der Parallelisierung nicht für eine Aufgabe oder Teilaufgabe nutzen würde /NAV 14/.

**Abb. 3.5** Schematische Darstellung der Architektur mit verteiltem Speicher (engl. "distributed memory")

Prozessor-Speichereinheiten sind über ein Kommunikationsnetzwerk miteinander verknüpft. Bei den Prozessoren handelt es sich um Ein-Kern-Prozessoren /BAR 17/.

Der größte Vorteil dieser Architektur besteht in der guten Skalierbarkeit. Prozessoren und Speicher wachsen proportional zueinander. Allerdings kann nachteilig ausgelegt werden, dass die Kommunikation zwischen den Prozessoren vom Programmierer zu erledigen ist. Zudem müssen Datenstrukturen, die auf einem globalen Adressraum beruhen, umorganisiert werden. Ein weiterer Nachteil sind die ungleichen Speicherzugriffszeiten, wenn Informationen auf einer anderen Prozessor-Speichereinheit liegen /BAR 17/. Um solche verteilten Speichersysteme zu verwenden, ist die Nutzung von "message passing" Programmiermodellen nötig /TRO 18/, wie z. B. MPI (siehe Abschnitt 4.2).

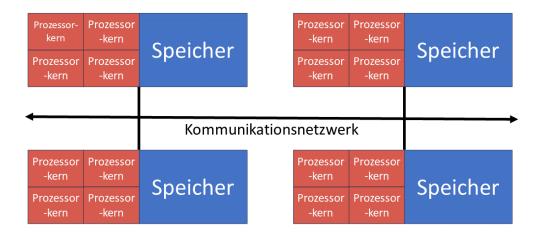

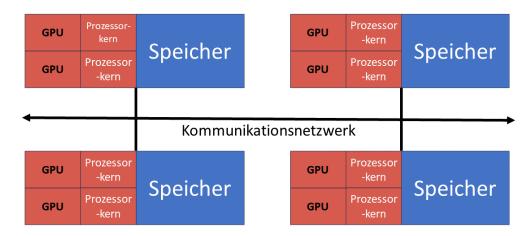

Parallel zu den Entwicklungen der Multicore-Prozessoren und den GPUs wurde auch das "distributed memory" System erweitert, so dass hybride Lösungen entstanden. Schematische Darstellungen solcher Systeme sind in der Abb. 3.6 und Abb. 3.7 dargestellt. Die hybride "distributed-shared memory" Architektur wird von den größten und schnellsten Computern der Welt (engl. "High Performance Computer" (HPC)) angewandt. Dabei können die "shared memory" Einheiten entweder "shared memory" Maschinen wie Multicore-Prozessoren oder GPUs sein (vgl. Abb. 3.6 und Abb. 3.7) /BAR 17/.

**Abb. 3.6** Schematische Darstellung der hybriden Architektur mit verteiltem Speicher ("distributed-shared memory") für Multicore-Prozessoren

Prozessor-Speichereinheiten sind über ein Kommunikationsnetzwerk miteinander verknüpft. Bei den Prozessoren (rot) handelt es sich in diesem Beispiel um Vier-Kern-Prozessoren /BAR 17/.

**Abb. 3.7** Schematische Darstellung der hybriden Architektur mit verteiltem Speicher ("distributed-shared memory") für Multicore-Prozessoren und GPUs

Prozessor-Speichereinheiten sind über ein Kommunikationsnetzwerk miteinander verknüpft. Bei den Prozessoren (rot) handelt es sich in diesem Beispiel sowohl um Zwei-Kern-Prozessoren als auch um angeschlossene GPUs. Nach /BAR 17/.

Der besondere Vorteil dieser hybriden Lösung liegt in der Skalierbarkeit der Prozessoren. Der Aurora HPC des Argonne National Laboratory in den USA, der als zweitschnellster HPC gelistet wird (Stand: 20. November 2024), verfügt über 9.264.128 CPU- und GPU-Prozessorkerne /TOP 24/. Ein Nachteil ist die hohe Programmierkomplexität solcher Systeme /BAR 17/.

Je nach genauer Architektur des hybriden Systems müssen "message passing", threadbasierte und/oder streambasierte Programmiermodelle eingesetzt werden /TRO 18/.

### 3.5 Parallelisierung in ARTM und ähnlichen Lagrange-Partikelmodellen

Im folgenden Abschnitt wurde recherchiert, inwieweit andere Lagrange-Partikelmodelle Parallelisierungsmöglichkeiten umsetzen. Die dabei verwendeten parallelen Programmiermodelle sind im Kapitel 4 im Rahmen des Arbeitspaket 2 erläutert.

#### 3.5.1 ARTM

In ARTM wird der Begriff des verteilten Rechnens in einem anderen Kontext als in Abschnitt 3.4 verwendet, indem Teilaufgaben generiert werden, die von mehreren aufgerufenen Instanzen<sup>4</sup> von ARTM unabhängig voneinander parallel abgearbeitet werden /GRS 20/. Die Parallelisierung erfolgt somit nicht auf Programmebene (ARTM), sondern auf Betriebssystemebene. Eine Kommunikation zwischen den einzelnen aufgerufen Instanzen ist somit nicht möglich, wodurch es sich von dem o. g. verteilten Rechnen klar abgrenzt.

Bei den Teilaufgaben handelt es sich um die Berechnung der Wind- und Turbulenzfelder sowie die Berechnung der Konzentrations-/Depositionsfelder und Felder der statistischen Unsicherheit. Die Methodik ist lediglich dann effektiv anwendbar, wenn die Teilaufgaben voneinander unabhängig sind. Die Erstellung der Windfeldbibliothek erfolgt für jede Ausbreitungsklasse unabhängig voneinander und kann somit auf mehrere Instanzen von ARTM verteilt werden. Die Ausbreitungsrechnung selbst wird in einzelne Sequenzen der meteorologischen Eingangsdaten aufgeteilt. Je nach Ausbreitungssituation und Größe des Rechengebietes können Partikel, die innerhalb einer Sequenz emittiert wurden, am Ende der Sequenz noch im Rechengebiet liegen. Da zwischen den einzelnen Sequenzen keine Kommunikation möglich ist, werden diese Partikel nicht weiter betrachtet und verfallen in weiteren Berechnungen. Das führt zu einer Unterschätzung der Luftaktivität, die sich bei einer Simulation von mehreren Tagen, Wochen oder Monaten aber innerhalb der Simulationsunsicherheiten befinden sollte. Falls am Ende einer Sequenz alle numerischen Partikel das Rechengebiet verlassen haben, dann sind die

\_

Eine Instanz (im o. g. Zusammenhang "Anwendungsinstanz") ist definiert als separater, abgeschlossener Programmablauf einer Anwendung mit einer eigenen, privaten Datengrundlage, die die strukturellen Voraussetzungen der Anwendung erfüllt /SHE 13/.

einzelnen Sequenzen voneinander unabhängig, und ein verteiltes Rechnen ergibt Ergebnisse, die sich nur durch statistische Variationen von der seriellen Abarbeitung der einzelnen meteorologischen Sequenzen unterscheiden.

#### 3.5.2 MPTRAC

MPTRAC (engl. "Massive-Parallel Trajectory Calculations") beinhaltet ein Lagrange-Partikelmodell für die Analyse der atmosphärischen Dispersion innerhalb der freien Troposphäre und der Stratosphäre /HOF 16/. MPTRAC ist genau wie ARTM in der Programmiersprache C geschrieben und eine relativ neue Entwicklung des Jülich Supercomputing Centre aus dem Jahr 2015. Das Programm ist OpenSource und unterliegt der GNU GPL Lizenz. Seit Beginn des Projekts durchlief das Programm mehrere Optimierungsphasen und umfasst aktuell 18 Versionen mit der aktuellen Programmversion 2.7. Ein Überblick über alle Versionen von MPTRAC ist auf der Webseite von Zenodo zu finden /ZEN 24/.

Die Parallelisierung innerhalb von MPTRAC basiert auf einen Hybridansatz aus CPU-Parallelisierung, verteilten Rechnen sowie GPU-Parallelisierung und ermöglicht somit abhängig von der Hardwarearchitektur einen effizienten Einsatz der unterschiedlichen Parallelisierungsmöglichkeiten. Auf einem Cluster kann z. B. Open Multi Processing (OpenMP) die CPU-Parallelisierung der einzelnen Prozesse auf einem Knoten umsetzen, während das verteilte Rechnen durch Message Passing Interface (MPI) die Kommunikation unter den unterschiedlichen Knoten sicherstellt (verteiltes Rechnen). In Kombination mit MPI können mit OpenACC seit Version 2.0 auch Multi-GPU-Simulationen durchgeführt werden /HOF 22/. Die Umsetzung im C Code erfolgt dabei über OpenMP und OpenACC Präprozessor Direktiven sowie entsprechenden Funktionen von MPI. Präprozessor Direktiven sind dabei im Quellcode eingefügte Anweisungen (Direktiven) für den Kompilierer.

Die Parallelisierung mittels OpenMP ist standardmäßig in allen Versionen von MPTRAC aktiv. Sie wird verwendet, um den advektiven Transport der Partikel auf die Prozessorkerne eines einzelnen Rechenknotens zu verteilen. Da OpenMP auf dem Prinzip des "shared memory" basiert, wird für die kompletten Berechnungen nur eine einzige Kopie der teils sehr großen meteorologischen Datensätze im Speicher gehalten. Typischerweise nehmen die Berechnungen der Trajektorien den größten Teil der Gesamtlaufzeit der Simulationen in Anspruch und können unabhängig voneinander durchgeführt werden. Aus diesem Grund lässt sich diese Parallelisierung sehr effektiv über einen großen

Bereich von Prozessorkernen skalieren. Bei der Parallelisierung mittels OpenMP in MPTRAC zeigte sich, dass die Performance grob linear mit der Anzahl der zur Verfügung stehenden CPUs skaliert /HOF 16/.

In MPTRAC Version 2.0 wurden OpenACC Präprozessor Direktiven verwendet, um die Berechnungen für die rechenintensiven Teile des advektiven Transports der Partikel auf die Rechenelemente der GPU zu verteilen. Weitere Präprozessor Direktiven sorgen für den relevanten Datentransfer zwischen dem Hauptspeicher und dem GPU-Speicher.

In Version 2.6 wurde eine weitere Optimierung der GPU-Parallelisierung des Kernels<sup>5</sup> für die Advektion der Partikel durchgeführt. Das betraf insbesondere den Speicherzugriff sowie die Datenstrukturierung der meteorologischen Eingangsdaten und die Eigenschaften der Partikel /HOF 24/. Für viele Teile des Codes, insbesondere für den Kernel der Advektion, wurde die Rechenzeit maßgeblich durch die Menge an freiem Speicher, die zum Halten der Arbeitsdaten erforderlich ist (engl. "memory-bound"), beschränkt. Ebenso erfolgte der Speicherzugriff größtenteils in beliebiger Reihenfolge (engl. "random access memory pattern"). Zufällige Speicherzugriffsmuster sind dabei im Allgemeinen schädlich für die Cache- und Speicherzugriffszeiten.

Der erste Aspekt, "memory-bound", wurde dadurch optimiert, dass die Datenstrukturierung der meteorologischen Daten angepasst wurde. Dabei wurden die dreidimensionalen horizontalen und vertikalen Windgeschwindigkeitskomponenten (u, v, w), die zuvor jeweils durch einem 3D-Array, bestehend aus Float Variablen, umgesetzt wurden (z. B.  $u[ex][ey][ez]^6$ ), durch ein 4D-Array ausgetauscht, welches als vierte Komponente die einzelnen Komponenten (u, v, w) enthält (d. h. uvw[ex][ey][ez][3]). Technisch gesprochen entspricht dies einem Wechsel von "Structure of Arrays" (SoAS) zu einem "Array of Structures" (AoSs). Hintergrund dieser Änderung ist, dass in der Programmiersprache C Arrays im Speicher zeilenweise angeordnet sind. Im Fall der 3D-Arrays mit der x-Koordinate als erste Dimension, der y-Koordinate als zweite und der z-Koordinate als dritte sind die Elemente der Windgeschwindigkeitskomponenten entlang der z-Achse am nächsten zueinander im Speicher abgelegt, gefolgt von der y-Dimension und der x-Dimension. In der Umsetzung SoAS kann somit das Vertikalprofil effektiv vom Haupt-

\_

<sup>&</sup>lt;sup>5</sup> Eine Funktion, die parallel auf einer angeschlossenen GPU ausgeführt werden soll, wird als Kernel bezeichnet.

<sup>&</sup>lt;sup>6</sup> ex, ey, und ez sind dabei die Dimensionen des Rechengitters in x-, y- und z-Richtung.

speicher auf den GPU-Speicher durch sogenannte Cache-Lines transferiert werden, d. h. der Zugriff vom Cache-Speicher zum Hauptspeicher erfolgt in einem einzigen, blockweisen Transfer. Falls jedoch der Kernel primär auf horizontale Profile zurückgreifen muss, wie es bei der Advektion größtenteils der Fall ist, ist die SoAS wenig effizient, da in der horizontalen Ebene die Daten weiter im Speicher voneinander getrennt sind als in der vertikalen Ebene und somit bei dem Transfer über Cache-Lines, die bei der GPU-Parallelisierung notwendig sind, teilweise auch unnötige Daten transferiert werden, auf die gar nicht zugegriffen werden muss. Dieses Problem wurde durch die Umstellung auf AoSs in MPTRAC gelöst.

Ein weiterer Faktor ist das Problem des zufälligen Speicherzugriffsmuster der Partikeldaten. Zu diesem Zweck wurde ein Sortierungsalgorithmus eingeführt, der es ermöglicht die Daten für die Partikeleigenschaften im Speicher besser zum allgemeinen Speicherzugriffsmuster der meteorologischen Daten zu orientieren. Der Algorithmus bewirkt dabei, dass ein lineares Iterieren über die Teilchen ermöglicht wird und dabei in einer optimierten Speicherzugriffsreihe auf die meteorologischen Daten zugegriffen werden kann. Zusammenfassend wurde also die Speicherstruktur der Partikel auf die Speicherstruktur der meteorologischen Daten angepasst.

MPTRAC ist ein sehr guter Kandidat, um Vergleiche zu ARTM zu ziehen. Zu den Vorteilen gehört u. a., dass beide Programme in C geschrieben und OpenSource sind. Als C Kompilierer wird bei MPTRAC die GNU Compiler Collection (GCC) verwendet, welcher ebenfalls für ARTM verwendet werden kann. Die Array-Struktur bei ARTM besteht zu großen Teilen aus AoSs, jedoch mit einem relativ komplizierten Table-Manager. Eine zentrale Aussage, die aus der Dokumentation von MPTRAC mitzunehmen ist, ist die genaue Speicherstruktur des Table-Managers zu studieren und im Fall auch anzupassen. Dieser Aspekt spielt jedoch primär dann eine Rolle, wenn eine Parallelisierung über die Grafikkarte realisiert werden soll.

Ein weiterer wichtiger Punkt, der aus der Dokumentation entnommen werden konnte, ist die Rechenzeit und deren Skalierbarkeit mit der Anzahl an verwendeten CPUs. In MPTRAC besteht sowohl die CPU-Parallelisierung der Advektion über OpenMP sowie die GPU-Parallelisierung mittels OpenACC.

#### 3.5.3 FLEXPART

FLEXPART (engl. "FLEXible PARTicle Dispersion Model") ist ein Lagrange-Transportund Dispersionsmodell, das für die Simulation einer Vielzahl atmosphärischer Transportprozesse geeignet ist. Geschrieben ist FLEXPART in der Programmiersprache Fortran 90 und ist wie ARTM und MPTRAC Open Source.

In FLEXPART wurde in der Version 10.4 zunächst die Parallelisierung durch MPI umgesetzt /PIS 19/. In Version 11 wurde diese Art der Parallelisierung durch OpenMP ersetzt /BAK 24/. Der Hintergrund der Umstellung war der Speicherzugriff. Während bei einer Parallelisierung mittels OpenMP zwischen den einzelnen Prozessen der Speicher, z. B. für die meteorologischen Eingangsfelder, gemeinsam genutzt wird ("shared memory"), wird bei einer Parallelisierung mittels MPI für jede Prozessor-Speichereinheit eine separate Datenkopie benötigt. Ein Testfall zeigte, dass eine Rechnung mit 10<sup>6</sup> freigesetzten Simulationspartikeln mittels einer OpenMP Parallelisierung, unabhängig von der Anzahl an Prozessorkernen, in etwa 11 GB an Speicher belegt. Eine analoge Rechnung mittels MPI und 32 Prozessor-Speichereinheiten benötigte hingegen 132 GB. Ebenso wurde argumentiert, dass durch das Aufsplitten der Ausbreitungsrechnung in mehrere einzelne Simulationen, wie es auch in ARTM aktuell durch das Aufsplitten in mehrere Instanzen von ARTM möglich ist, weiterhin ein Ansatz zur Parallelisierung auf verteilte Speicher Systemen verfügbar ist.

In FLEXPART Version 11 wurden große Teile des Codes parallelisiert. Dazu gehört die Parallelisierung aller partikelabhängigen Berechnungen (ausgenommen der initialen Freisetzung), der Advektion, der nassen und trockenen Deposition sowie der vertikalen Koordinatentransformation der Felder. Testrechnungen zeigten dabei, dass bei 10<sup>6</sup> und 10<sup>7</sup> Simulationspartikeln die Rechenzeit lediglich um einen Faktor 1.3 langsamer ist als die bei einer perfekten Skalierung<sup>7</sup>. Hingegen steigt bei einer geringeren Anzahl von Simulationspartikeln, beispielsweise 10<sup>5</sup> Simulationspartikeln, der Faktor schon auf 2. Zu erklären ist dies damit, dass der Geschwindigkeitsvorteil durch die Parallelisierung den Geschwindigkeitsnachteil durch die aufwendigere Speicherverwaltung nicht kompensie-

.

Eine perfekte Skalierung bedeutet, dass eine Reduzierung der Rechenzeit linear einhergeht mit der Anzahl an verwendeten Prozessoren, d. h. beispielsweise, wenn eine serielle Rechnung sechs Stunden dauert, dauert die identische Rechnung mittels einer Parallelisierung durch sechs Prozessoren lediglich eine Stunde. Ein Faktor von 1 bedeutet perfekte Skalierung. Faktoren größer als 1 deuten an, dass die Parallelisierung nicht perfekt ist. Serielle und parallele Ausführung wären zeitlich identisch, wenn der Faktor der Anzahl der verwendeten Prozessoren entspräche.

ren kann. Ähnliche Erkenntnisse ergaben sich auch bei der Parallelisierung mittels MPI, nämlich dass die Parallelisierung mit steigender Anzahl von Simulationspartikeln zielführender ist.

Ebenfalls in Entwicklung ist eine für die CTBTO<sup>8</sup> angepasste FLEXPART Version, die es ermöglichen soll, GPUs effizient zur Parallelisierung nutzen zu können /MOR 23/. Die Anpassung wird an der Version v10 vorgenommen und soll die GPU-Parallelisierung mittels des Fortran-Kompilierer nvfortran erreichen. nvfortran ist dabei kompatibel mit NVIDIA-GPUs und umfasst eine CUDA-Toolchain<sup>9</sup>, Bibliotheken und Header-Dateien für GPU-Computing /NVI 24b/. Die Erstellung von Leistungsprofilen des Codes mit benutzerdefinierten und von NVIDIA bereitgestellten Tools zeigte, dass insbesondere der Transport der Partikel mittels der GPUs am zielführendsten zu parallelisieren sei. Im Vortrag von Herrn Morton auf der CTBT: Science and Technology Conference 2023 /MOR 23/ wird jedoch hervorgehoben, dass die einzelnen Iterationen des Partikeltransportes stark voneinander abhängig sind. Analog zu ARTM weist der FLEXPART Code eine tiefe Hierarchie von Unterprogramm- und Funktionsaufrufen auf, die zudem mit über mehr als 200 globalen Variablen stark voneinander abhängen und in vielen Fortran-Modulen verteilt und definiert sind. Aus diesem Grund wurden Teile des Codes in einfachere, schnell auszuführende und eigenständige Testprogramme extrahiert. Die Parallelisierung wurde dabei mittels OpenACC und mehr als 200 Direktiven umgesetzt. Deutlich wird im Vortrag hervorgehoben, dass die GPU-Parallelisierung von FLEXPART mittels OpenACC eine große Herausforderung darstellt. Ein Zitat aus dem Vortrag ist:

"The application of OpenACC directives – **just to get it to compile and execute** – has been quite complicated and tedious, requiring many directives, and the creation of a spreadsheet to maintain an inventory of all 200+ global module variables referenced in the underlying code."

Die Comprehensive Nuclear-Test-Ban Treaty Organization (CTBTO) ist eine internationale Organisation, die mit Inkrafttreten des Kernwaffenteststopp-Vertrages (CTBT) ihre Arbeit aufnehmen und sodann die Einhaltung dieses Vertrages überwachen soll.

<sup>&</sup>lt;sup>9</sup> Eine Toolchain ist eine Sammlung von Softwareentwicklungstools, welche zur Erzeugung einer Software verwendet werden. Der Begriff "chain" bedeutet dabei, dass die Tools nacheinander ausgeführt werden und von den Ergebnissen der jeweiligen Tools abhängen.

#### 3.5.4 PALM

PALM (engl. "PArallelized Large-Eddy Simulation Model") wurde vom Institut für Meteorologie und Klimatologie der Leibniz Universität Hannover entwickelt und basiert auf der Programmiersprache Fortran 95 mit einigen Erweiterungen in Fortran 2003. PALM ist frei verfügbar und unterliegt der GNU GPL Lizenz.

Wie der Name schon sagt, werden Large-Eddy Simulationen (LES) für verschiedene atmosphärische und ozeanische Grenzschichten mit PALM durchgeführt /MAR 15/. Ein Lagrange-Partikelmodell ist in PALM implementiert und nimmt als Eingabe die Windund Turbulenzfelder der LES von PALM.

PALM ist optimiert für die Simulation auf HPCs und wird seit Version 3.9 aus dem Jahr 2013 sukzessiv für die Anwendung auf GPUs erweitert. Die Umsetzung der GPU-Parallelisierung innerhalb des Codes wird mittels OpenACC realisiert. Eine vollständige GPU-Umsetzung wurde im Jahr 2016 abgeschlossen /KNO 16/.

PALM enthält zwei Methoden der Parallelisierung, eine basierend auf einer zwei- dimensionalen Domain Decomposition Methode (DDM), eine weitere auf Schleifenebene.

Details zur DDM können /RAA 01/ entnommen werden. Kurz zusammengefasst wird das gesamte Rechengebiet in Teilbereiche (engl. "Subdomain") unterteilt, die den Prozessoreinheiten (PE) zugeordnet werden. Pro PE gibt es einen dazugehörigen Teilbereich und jede PE löst die gesamte Menge an Modellgleichungen auf seinem Teilbereich. Die Kommunikation zwischen den PEs wird durch MPI realisiert, und Randbedingungen der zu lösenden Modellgleichungen werden implizit durch eine virtuellen zweidimensionalen Prozessortopologie realisiert, in der die Prozessoren an den entsprechenden Enden einzelner Zeilen bzw. Spalten gekoppelt sind.

Die Parallelisierung auf Schleifenebene, auf Basis der "shared memory" Architektur, wird durch OpenMP realisiert. Im sogenannten Hybridmodus können durch verteiltes Rechnen mit MPI mehrere MPI-Prozesse mit mehreren OpenMP-Threads auf unterschiedlichen Knoten gestartet werden.

#### 3.5.5 HYSPLIT

Im Hybrid Single-Particle Lagrangeian Integrated Trajectory Model (HYSPLIT) wurde eine Parallelisierung durch die "shared memory" Architektur und OpenMP sowie durch

eine GPU-Parallelisierung auf einer NVIDIA GTX960 und Tesla P100 Grafikkarte mittels CUDA realisiert /YU 19/. Ebenso existiert eine Möglichkeit der Parallelisierung mittels MPI, welche jedoch nur effektiv für Programme mit grober Granularität ist, bei denen die Prozesse eine lange Ausführungszeit haben und damit nur wenig Datenaustausch zur Synchronisation benötigen.

Das analysierte Leistungsprofil des nicht parallelisierten Ursprungscode zeigte, dass mehr als 80 % der Rechenzeit auf Interpolationsschritte, der Dispersion sowie der Advektion innerhalb der Schleifenebene der Simulationspartikel fallen. Die Schleifenebene der Simulationspartikel besaß in ihrer Ursprungsform schon eine nahezu perfekte Parallelisierbarkeit und hatte nur zwei kritische Funktionen, die eine Parallelisierung verhinderten. Die erste Funktion war die Zuordnung eines Simulationspartikels in ein Teilrechengebiet basierend auf seiner vorherigen Iteration, die zweite Funktion die am Ende einer Schleife zu berechnende Konzentration. Um die Datenabhängigkeit dieser beiden Funktionen zu umgehen, wurde die Schleifenebene in eine serielle Schleife (Neuladen des Teilrechengebiets und weitere Datei-Eingabe/Ausgabe-Vorgänge), eine parallele Schleife (Advektion, Interpolation, Dispersion und Deposition), gefolgt von einer seriellen Schleife (zu berechnende Konzentration) aufgeteilt. Die parallele Schleife wurde dabei mittels OpenMP realisiert.

Die GPU-Parallelisierung erfolgt durch die Abarbeitung von zwei Kernelfunktionen auf der GPU, eine für Advektion und Interpolation und eine weitere für die Dispersion, mit anschließendem Übertrag der Ergebnisse von der GPU auf den Wirt.

Eine mögliche weitere Optimierung (engl. "Coarse Grain GPU Parallelization Approach") ist eine Überlappung verschiedener Kernel-Aufrufe, welche den Speicheraufwand des Wirt-Geräts reduziert und eine schlechte GPU-Auslastung korrigiert. Dabei gibt es in HYSPLIT drei verschiedene Ansätze:

Single-Thread-Ansatz: Ein einzelner CPU-Thread weist gemäß des Round-Robin-Verfahrens<sup>10</sup> Aufgaben den verschiedenen CUDA-Streams<sup>11</sup> zu.

\_

Ein Verfahren, bei dem die Aufgaben reihum und gleichmäßig an die abarbeitende Struktur verteilt werden.

<sup>&</sup>lt;sup>11</sup> Ein Stream ist eine Reihe von Befehlen, die der Reihe nach ausgeführt werden. In CUDA-Anwendungen erfolgen die Kernel-Ausführung sowie einige Speicherübertragungen innerhalb von CUDA-Streams.

- Multi-Thread-Ansatz: Jeder CPU-Thread weist Aufgaben seinem eignen CUDA-Stream zu.

- Multiprozess-Ansatz: Jeder MPI-Prozess weist Aufgaben seinem eignen CUDA-Stream zu.

Für die Parallelisierung mittels OpenMP wurde bei Performancetests eine nahezu perfekte Skalierung mit minimalem seriellem Overhead erreicht. Bei der GPU-Parallelisierung ergab sich eine 4 – 5-mal schnellere Gesamtleistung als das Original ohne Parallelisierung ausgeführt auf einer CPU. Mit Hilfe der Überlappung verschiedener Kernel-Aufrufe wurde eine maximale Beschleunigung um das 12,9-fache im Vergleich zum Originalprogramm erreicht.

### 3.5.6 Parallel Micro-SWIFT-SPRAY (PMSS)

Parallel Micro-SWIFT-SPRAY (PMSS) ist die parallele Programmierungsumsetzung der Kombination aus dem Windfeldmodell Micro-SWIFT und dem Lagrange-Partikelmodell Micro-SPRAY. Die Parallelisierung in PMSS wird durch verteiltes Rechnen mit MPI realisiert /OLD 11/.

SWIFT wird über zwei Wege parallelisiert, einerseits der DDM ähnlich zu PALM, und andererseits über die zeitliche Parallelisierung (engl. "time frame parallelization" (TP)). Beide Wege können parallel genutzt werden. Bei der DDM wird das Rechengitter in kleinere Teilbereiche unterteilt, so dass sie in den Speicher eines einzelnen Prozessorkerns passen. Liegen nach der initialisierten DDM noch Prozessorkerne für die TP vor, werden parallel verschiedene Zeitschritte auf den Prozessorkernen berechnet. Da zwischen zwei einzelnen Zeitschritten keine Kommunikation erforderlich ist, ist die Beschleunigung unter TP sehr effizient. Bei der DDM erfordert jeder einzelne Schritt des Lösungsalgorithmus eine MPI-Kommunikation zwischen benachbarten Teilbereichen, sowohl für den massenkonsistenten als auch für den RANS-Löser in SWIFT. Neben den Prozessorkernen, die die Parallelisierung und Rechnungen durchführen, braucht SWIFT auch einen sogenannten Master Prozessorkern (engl. "master core"), welcher die Aufgaben und Eingangsdaten auf die entsprechenden Prozessorkerne verteilt.

Die Parallelisierung von SPRAY baut auf der übergebenen Datenstruktur von SWIFT auf. Falls SWIFT lediglich ein Rechengitter übergibt, wird SPRAY im sogenannten Single-Tile Parallelization (STP)-Modus betrieben. Der STP-Modus benötigt nur eine geringe Kommunikation zwischen den einzelnen Prozessorkernen und verteilt mittels MPI

die emittierten Simulationspartikel auf die zur Verfügung gestellten Prozessorkerne. Da die emittierten Simulationspartikel zufällig den Prozessorkernen zugeteilt werden, ergibt sich ein Gleichgewicht zwischen schnellen und langsam dispergierenden Simulationspartikeln, so dass jeder Prozessorkern ähnlich lange für die Berechnung braucht. Ebenso wird jeder Prozessorkern mit einer anderen Anfangszahl des Zufallszahlengenerators gestartet, um die statistische Eigenschaft des Modells aufrecht zu halten. Zum Zeitpunkt der Synchronisierung, d. h. am Ende jedes Zeitschrittes, summiert der Master Prozessor die dreidimensionalen Konzentrationsfelder der einzelnen Prozessorkerne auf. Diese werden dem Master Prozessor über MPI-Kommunikation von den einzelnen Prozessorkernen zur Verfügung gestellt.

Falls SWIFT mehrere separate Teilgebiete des Rechengitters an SPRAY übergibt, aktiviert SPRAY den Multiple-Tiles Parallelization (MTP)-Modus. In einem ersten Schritt werden beim Aufruf der Routinen für den allerersten Zeitschritt alle Teilgebiete aktiviert, in denen eine Quelle vorliegt. Alle anderen werden deaktiviert. Abhängig von den Massenraten der vorliegenden Quellen, werden anschließend die zur Verfügung stehenden Prozessorkerne auf die aktivierten Teilgebiete verteilt. Liegen beispielsweise zwei Quellen an unterschiedlichen Stellen im Rechengebiet vor und besitzt die eine Quelle eine doppelte Massenrate als die andere, werden dem Teilgebiet mit der doppelten Masse entsprechend auch doppelt so viele Prozessorkerne mittels spezifischer MPI-Kommunikatoren (engl. "specific MPI communicators" (SMPIC)) zugeteilt. Im nächsten Schritt werden den Prozessorkernen in den Teilgebieten die Simulationspartikel zugeteilt. Dieses erfolgt analog zum STP-Modus. Da Simulationspartikel dispergieren und somit Teilgebiete verlassen oder aus anderen Teilgebieten einfließen können, sind die einzelnen Teilgebiete nicht unabhängig voneinander. Aus diesem Grund muss jedes Teilgebiet einen Master Prozessorkern besitzen, der zum Zeitpunkt der Synchronisation sowohl Simulationspartikel an andere Teilgebiete sendet als auch von anderen Teilgebieten empfängt. Falls zum Zeitpunkt der Synchronisation Simulationspartikel in ein noch nicht aktiviertes Teilgebiet dispergiert sind, werden die Prozessorkerne anderer Teilgebiete für das nun aktivierte Teilgebiet zur Verfügung gestellt. Da durch das Dispergieren der Simulationspartikel schnell ein Ungleichgewicht zwischen den aktivierten Teilgebieten und den darin enthaltenen Simulationspartikeln entstehen kann, wurde in SPRAY ein sogenannter "Load Balancing Process" entwickelt. Dieser berechnet zunächst durch den Master Prozessorkern in jedem Teilgebiet die Gesamtanzahl an Simulationspartikeln. Je mehr Simulationspartikel in einem Teilgebiet vorliegen, desto mehr verfügbare Prozessorkerne werden diesem Teilgebiet zugeteilt. Die dazu notwendigen Prozessorkerne werden dabei von Teilgebieten weggenommen, die im Vergleich eine geringe Anzahl an

Simulationspartikeln aufweisen. In einem letzten Schritt werden erneut die Simulationspartikel auf die für das Teilgebiet zugeteilten Prozessorkerne verteilt.

Für ARTM ist MTP wahrscheinlich nicht zielführend, da der "Load Balancing Process" am Ende jedes Zeitschrittes viel Rechenzeit benötigt. MTP wird insbesondere dann interessant, wenn das Rechengebiet sehr groß ist. Die PMSS Simulation im Rahmen des EMED Projektes umfasste beispielsweise ein Rechengebiet von 19.333 x 16.666 x 39 Gitterzellen mit einer horizontalen Auflösung von 3 m und einer vertikalen Auflösung von 1 m in Bodennähe /OLD 19/. Die Leistungsfähigkeit von MTP wurde für einzelne Teilgebiete mit der kleinsten Auflösung von 201 x 201 Punkten bis hin zu einer Auflösung von 1001x1001 getestet. Dadurch ergaben sich 8051 bzw. 340 Teilgebiete. Zur Verfügung standen 500 bis 3.000 Prozessorkerne. Anhand dieser Zahlen ist deutlich zu erkennen, dass MTP für ARTM nicht geeignet ist, da tendenziell schon die kleinsten Teilgebiete in der Größenordnung der maximal erlaubten Gitterzellen in der horizontalen Ebene von ARTM liegen. Für ARTM ist somit lediglich die STP von Relevanz. Tests der Leistungsfähigkeit zeigten dabei eine nahezu perfekte Skalierung. Details zur Dimension des Rechengitters sind jedoch nicht angegeben, so dass eine Bewertung hinsichtlich der Effektivität der STP für ARTM nicht möglich ist.

### 3.5.7 Zusammenfassung

Die Tab. 3.1 gibt einen Überblick über die verwendeten Parallelisierungsmodelle innerhalb der betrachteten Lagrange-Partikelmodelle.

**Tab. 3.1** Überblick über die verwendeten Parallelisierungsmodelle innerhalb der betrachteten Lagrange-Partikelmodelle

| Modell   | OpenMP | MPI        | OpenACC                 | CUDA |

|----------|--------|------------|-------------------------|------|

| MPTRAC   | ✓      | ✓          | ✓                       | ×    |

| FLEXPART | ✓      | <b>x</b> 1 | <b>(√)</b> <sup>2</sup> | ×    |

| PALM     | ✓      | ✓          | ✓                       | ×    |

| HYSPLIT  | ✓      | ✓          | *                       | ✓    |

| PMSS     | *      | ✓          | *                       | ×    |

<sup>&</sup>lt;sup>1</sup> Aktuelle Version nur noch OpenMP, zuvor Parallelisierung mittels MPI

Nahezu alle Modelle enthalten eine Parallelisierung mittels der "shared memory" Architektur und dem Standard OpenMP. Alle Modelle haben dabei den Transport der Simulationspartikel als kritischsten Punkt der Laufzeit identifiziert und somit diesen parallelisiert.

<sup>&</sup>lt;sup>2</sup> Anpassung an Version 10.0 für die CTBTO, noch in Entwicklung

In mehreren Publikationen wird hervorgehoben, dass das verteilte Rechnen mittels MPI nur dann sinnvoll ist, wenn für die Rechnungen eine grobe Granularität gegeben ist, d. h. die Prozesse besitzen eine lange Ausführungszeit bei nur wenig Datenaustausch zur Synchronisation. Dies ist insbesondere für hochaufgelöste und große Rechengebiete der Fall, wie z. B. das PMSS Rechengebiet von 19.333 x 16.666 x 39 Gitterzellen mit einer horizontalen Auflösung von 3 m und einer vertikalen Auflösung von 1 m in Bodennähe innerhalb des EMED Projektes /OLD 19/. Ein weiteres Beispiel sind die Large-Eddy Simulationen in PALM, die als Grundvoraussetzung sehr feine Gitterstrukturen benötigen. Ebenso ist zu beachten, dass Modelle wie MPTRAC, PALM und auch HYSPLIT für massiv parallele Computerarchitekturen programmiert sind. Durch die Vielzahl an zur Verfügung stehenden Knoten ist dabei eine Parallelisierung mittels MPI zielführend. Die Ansprüche sind jedoch nicht unbedingt identisch zu denen von ARTM, da ARTM nicht primär für massiv parallele Computerarchitekturen ausgelegt sein soll.

FLEXPART wurde in der neuesten Version von MPI auf OpenMP umgestellt, da der notwendige Speicher durch eine Parallelisierung mittels MPI zu groß wurde und die Speicherverwaltung länger brauchte als die eigentliche Aufgabe.

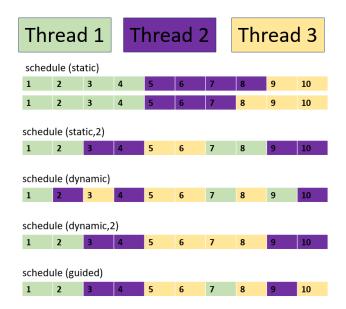

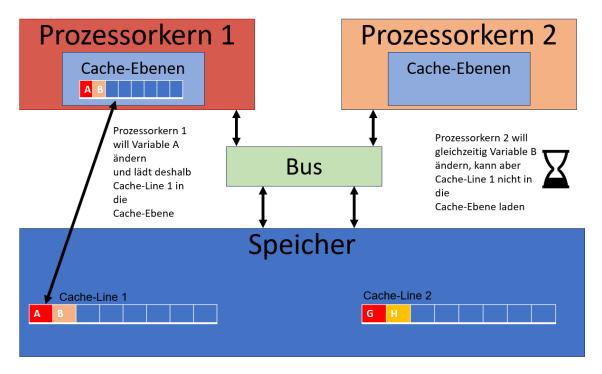

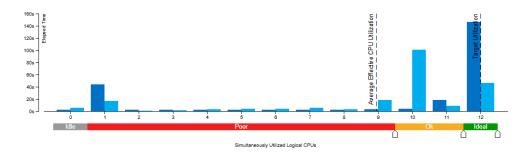

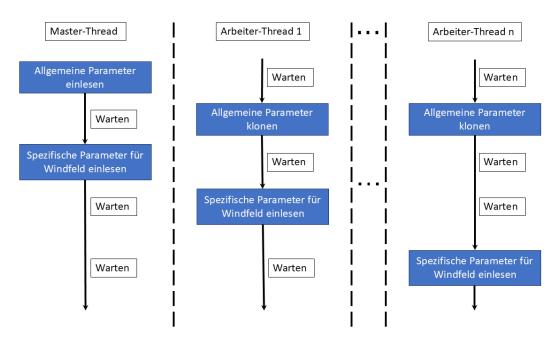

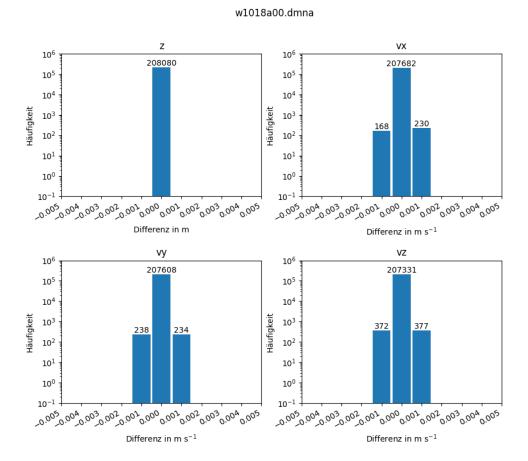

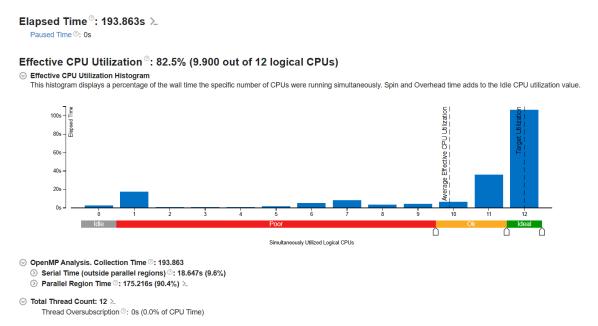

Tendenziell sieht die GRS ARTM eher im Bereich der feinen Granularität, d. h. die Ausführungszeit bzw. Arbeitsweise der einzelnen Aufgaben ist klein bzw. schnell im Vergleich zur Abarbeitungszeit des kompletten Programmes. Aus diesem Grund wird für eine feinkörnige Parallelität ein Programm in eine große Anzahl kleiner Aufgaben zerlegt und einzeln vielen Prozessoren zugewiesen. Da jede Aufgabe somit weniger Daten verarbeiten muss und aufgrund dessen nur eine geringe Datenmenge zur Synchronisation notwendig ist, diese aber sehr häufig unter den Prozessen ausgetauscht werden müssen, ist solch eine Architektur am effektivsten parallelisierbar mittels der "shared memory" Architektur und somit mittels OpenMP. Aus diesem Grund schätzt die GRS für die Schleifenebene des Partikeltransports die Umsetzung analog zu der von HYSPLIT als am sinnvollsten für ARTM ein.