Development and Evaluation of Architecture Concepts for a System-on-Chip Based Neuromorphic Compute Node for Accelerated and Reproducible Simulations of Spiking Neural Networks in Neuroscience

Guido Trensch

IAS Series Band / Volume 71 ISBN 978-3-95806-832-2

Forschungszentrum Jülich GmbH Institute for Advanced Simulation (IAS) Jülich Supercomputing Centre (JSC)

Development and Evaluation of Architecture Concepts for a System-on-Chip Based Neuromorphic Compute Node for Accelerated and Reproducible Simulations of Spiking Neural Networks in Neuroscience

**Guido Trensch**

Schriften des Forschungszentrums Jülich IAS Series

Bibliografische Information der Deutschen Nationalbibliothek. Die Deutsche Nationalbibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliografie; detaillierte Bibliografische Daten sind im Internet über http://dnb.d-nb.de abrufbar.

Herausgeber Forschungszentrum Jülich GmbH

und Vertrieb: Zentralbibliothek, Verlag

52425 Jülich

Tel.: +49 2461 61-5368 Fax: +49 2461 61-6103 zb-publikation@fz-juelich.de

www.fz-juelich.de/zb

Umschlaggestaltung: Grafische Medien, Forschungszentrum Jülich GmbH

Druck: Grafische Medien, Forschungszentrum Jülich GmbH

Copyright: Forschungszentrum Jülich 2025

Schriften des Forschungszentrums Jülich IAS Series, Band / Volume 71

D 82 (Diss. RWTH Aachen University, 2024)

ISSN 1868-8489 ISBN 978-3-95806-832-2

Vollständig frei verfügbar über das Publikationsportal des Forschungszentrums Jülich (JuSER) unter www.fz-juelich.de/zb/openaccess.

This is an Open Access publication distributed under the terms of the <u>Creative Commons Attribution License 4.0</u>, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

# **Abstract**

Despite the great strides neuroscience has made in recent decades, the underlying principles of brain function remain largely unknown. Advancing the field strongly depends on the ability to study large-scale neural networks and perform complex simulations. Simulations in hyper-real time are of high interest here, as they would enable both comprehensive parameter scans and the study of slow processes such as learning and long-term memory. Not even the fastest supercomputer available today is capable of meeting the challenge of accurate and reproducible simulation with hyper-real acceleration. The development of novel neuromorphic computing architectures holds out promise, but the high costs and long development cycles for application-specific hardware solutions makes it difficult to keep pace with the rapid developments in neuroscience. Commercial off-the-shelf System-on-Chip (SoC) devices, integrating programmable logic, general-purpose processors, and memory in a single chip, offer an alternative. This technology is providing interesting new design possibilities for application-specific implementations while avoiding costly chip development.

The primary aim of this thesis is to develop and evaluate a novel SoC-based architecture for a neuromorphic compute node intended to operate in a multi-node cluster configuration and capable of performing hyper-real-time simulations. As a complementary, yet distinct approach to the neuromorphic developments aiming at brain-inspired and highly efficient novel computing architectures for solving real-world tasks, the design of the compute node is strictly driven by neuroscience requirements. These requirements are demanding, as is the process of deriving appropriate design decisions from them.

Even for domain experts, it is often difficult to judge the correctness of a simulation result. This leaves some uncertainty when making design decisions and proving the correctness of an architectural design and its physical implementation. Methods for building credibility, such as verification and validation, have been developed but are not yet well established in the field of neural network modeling and simulation. This thesis therefore also outlines a rigorous model substantiation methodology for increasing the correctness of neural network simulation results in the absence of experimental validation data. The method was applied during the development and

evaluation of the neuromorphic compute node to build credibility on implementation correctness. Finally, with the goal of large-scale neuromorphic computing, related technological aspects are discussed and architectural enhancements for the neuromorphic compute node are presented. This is accompanied by a workload analysis of two large-scale neural network models used in neuroscience. Also, a concept for system integration is proposed that incorporates the high-performance computing (HPC) landscape and takes into account existing tools and workflows for modeling and simulation in computational neuroscience.

The results presented in this thesis reveal the potential of commercial off-the-shelf SoC technology and demonstrate its suitability as a substrate for neuromorphic computing for application in computational neuroscience. Recent developments in this technology, particularly the integration of high-bandwidth memory (HBM), promise significant performance improvements. Acceleration factors on the order of 100 become within reach, even for the simulation of large-scale spiking neural networks.

# Zusammenfassung

Trotz der enormen Fortschritte, die die Neurowissenschaften in den letzten Jahrzehnten erzielt haben, sind die grundlegenden Prinzipien der Funktionsweise des Gehirns noch weitgehend unverstanden. Der Fortschritt auf diesem Gebiet hängt stark von der Fähigkeit ab, großskalige neuronale Netzwerke untersuchen zu können und komplexe Simulationen durchzuführen. In diesem Zusammenhang sind Simulationen in Hyper-Echtzeit von großem Interesse, da dies sowohl umfassende Parameterscans als auch das Studium langsamer Prozesse, wie Lernen und Langzeitgedächtnis, ermöglichen würde. Doch selbst der leistungsfähigste heute verfügbare Supercomputer ist nicht in der Lage, die Herausforderung einer genauen, reproduzierbaren und zugleich signifikant beschleunigten Simulation zu bewältigen. Die Entwicklung neuartiger neuromorpher Computerarchitekturen ist hier vielversprechend. Dem gegenüber stehen jedoch hohe Kosten und lange Entwicklungszyklen für anwendungsspezifische Hardwarelösungen, die es erschweren, mit dem rasanten Tempo der Entwicklungen in den Neurowissenschaften Schritt zu halten. Eine Alternative bietet hier kommerziell verfügbare System-on-Chip (SoC) Technologie, die programmierbare Logik, Allzweckprozessoren und Speicher in einem einzigen Chip integriert. Diese Technologie eröffnet interessante neue Designmöglichkeiten für anwendungsspezifische Implementierungen, wobei eine kostspielige Chipentwicklung vermieden wird.

Das Hauptziel dieser Arbeit ist die Entwicklung und Evaluierung einer neuartigen SoC-basierten Architektur eines neuromorphen Rechenknotens, der in einer Clusterkonfiguration betrieben werden soll und in der Lage ist, Hyper-Echtzeit-Simulationen durchzuführen. Als komplementärer, aber dennoch eigenständiger Ansatz zu den neuromorphen Entwicklungen, die auf vom Gehirn inspirierte und hocheffiziente neuartige Computerarchitekturen zur Lösung realer Aufgaben abzielen, orientiert sich das Design des Rechenknotens streng an den Anforderungen der Neurowissenschaften. Diese Anforderungen sind anspruchsvoll, ebenso wie der Prozess der Ableitung angemessener Designentscheidungen daraus.

Selbst für Fachexperten ist es oft schwierig, die Korrektheit eines Simulationsergebnisses zu beurteilen. Dies führt zu einer Unsicherheit bei Designentscheidungen und beim Nachweis der Korrektheit eines Architekturentwurfes und dessen technischer Implementierung. Methoden, die

Sicherheit schaffen, wie z.B. Verifizierungs- und Validierungsverfahren, wurden zwar entwickelt, sind aber in den Neurowissenschaften im Bereich der Modellierung und Simulation neuronaler Netzwerke noch nicht gut etabliert.

Ergänzend stellt diese Arbeit daher eine strenge Methodologie zur Modellabsicherung vor, mit der die Korrektheit von Ergebnissen neuronaler Netzwerksimulationen erhöht werden kann, wenn keine experimentellen Validierungsdaten zur Verfügung stehen. Bei der Entwicklung und Evaluierung des neuromorphen Rechenknotens wurde diese Methodik eingesetzt, um Sicherheit hinsichtlich der Implementierungskorrektheit zu schaffen.

Schliesslich, mit dem Ziel großskaligen neuromorphen Computings, werden hierbei relevante technologische Aspekte diskutiert und Architekturverbesserungen für den neuromorphen Rechenknoten aufgezeigt. Begleitet wird dies von einer Analyse der bei der Simulation großskaliger Netwerke zu erwartenden Arbeitslast. Hierfür werden zwei in den Neurowissenschaften verwendete großskalige neuronale Netzwerkmodelle herangezogen. Ebenso wird ein Konzept für eine Systemintegration vorgestellt, welches die High-Performance Computing (HPC) Landschaft einbezieht und bestehende Werkzeuge und Arbeitsabläufe für die Modellierung und Simulation berücksichtigt.

Die Ergebnisse dieser Arbeit zeigen das Potential kommerziell verfügbarer SoC-Technologie und demonstrieren dessen Eignung als Platform für neuromorphes Computing für die Anwendung in den computergestützten Neurowissenschaften. Aktuelle Entwicklungen dieser Technologie, insbesondere die Integration von High-Bandwidth-Memory (HBM), versprechen darüber hinaus deutliche Leistungssteigerungen. Selbst für die Simulation großskaliger spikender neuronaler Netzwerke rücken damit Beschleunigungsfaktoren in der Größenordnung von 100 in den Bereich des technologisch Erreichbaren.

# **Acknowledgments**

This thesis summarizes my work from 2017 to 2023 at the Research Center Jülich. Completing this thesis would not have been possible without the support of friends and colleagues, and I am very grateful to everyone I had the pleasure to work with during this project.

First and foremost, I would like to express my special thanks to my supervisor, Prof. Abigail Morrison, for always providing invaluable guidance and feedback. I am also indebted to Prof. Tobias Gemmeke for supporting my work and for taking on the role of the second reviewer. I furthermore would like to sincerely thank Prof. Matthias Müller and Prof. Torsten Kuhlen for taking on the roles of the third examiner and the chair of the examination committee, respectively.

I gratefully acknowledge all the colleagues I had the privilege to work with in the Advanced Computing Architectures (ACA) project. I cannot emphasize enough the value of this collaboration, the fruitful discussions we have had, and the feedback I have received. In particular, I would like to extend my special thanks to Prof. Tobias Noll, Dr. Georgia Psycho, Eqbal Maraqa, Dr. Michael Schiek, Dr. Markus Robens, Darshana Amarasingha, and especially Dr. Arne Heittmann for his comments on an earlier version of the manuscript on the neuromorphic compute node concept. I would also like to thank Prof. Markus Diesmann, one of the main initiators and driving forces of the ACA project, as well as Dr. Tom Tetzlaff for the inspiring discussions we had during our *neuromorphic tea* sessions and in his garden. I particularly remember our conversation about the computational cost of time- and event-driven simulations, which inspired the development of the workload and performance model.

I would also like to express my gratitude to Robin Gutzen, Dr. Michael Denker, Dr. Michael von Papen, Pietro Quaglio, and Prof. Sonja Grün for the fruitful collaboration throughout the model validation project. I would especially like to thank Fahad Kahlid for his comments on an earlier manuscript about model validation. I thank my colleagues at the Simulation and Data Laboratory Neuroscience and the Jülich Supercomputing Centre for their support and continuous collaboration, and for being a great bunch of people in and out of the lab. I also thank the NEST and NESTML developer community. Working in this community has given me valuable knowledge about modeling and simulation technologies. On a personal level, here I would like to

thank Dennis Terhorst, Dr. Jochen Martin Eppler and Dr. Dimitri Plotnikov.

I am also grateful to the German and European institutions that have supported my work. This project has received funding from the Helmholtz Association Initiative and Networking Fund under project No. SO-092 (Advanced Computing Architectures, ACA) and through the Helmholtz Portfolio Theme Supercomputing and Modeling for the Human Brain (SMHB). In addition, this project has also received funding from the European Union's Horizon 2020 Framework Programme for Research and Innovation under Specific Grant Agreements No. 720270 (Human Brain Project SGA1) and No. 785907 (Human Brain Project SGA2). Open Access publications have been funded by the Deutsche Forschungsgemeinschaft (DFG, German Research Foundation) – 491111487.

Finally, I dedicate this work to my dear wife, Dr. phil. Nosrat Kazemi-Trensch, for her constant support, love, understanding, and encouragement through life's challenges.

Jülich, December 2024

# Eidesstattliche Erklärung

Ich, Guido Trensch, erkläre hiermit, dass diese Dissertation und die darin dargelegten Inhalte die eigenen sind und selbstständig, als Ergebnis der eigenen originären Forschung, generiert wurden. Hiermit erkläre ich an Eides statt:

- Diese Arbeit wurde vollständig oder größtenteils in der Phase als Doktorand und wissentschaftlicher Mitarbeiter des Simulation and Data Laboratory Neuroscience des Forschungszentrum Jülich angefertigt.

- Sofern irgendein Bestandteil diseser Dissertation zuvor für einen akademischen Abschluss oder eine andere Qualifikation an dieser oder einer anderen Institution verwendet wurde, wurde dies klar angezeigt.

- Wenn immer andere, eigene oder Veröffentlichungen Dritter herangezogen wurden, wurden diese klar benannt.

- 4. Wenn aus anderen, eigenen oder Veröffentlichungen Dritter zitiert wurde, wurde stets die Quelle hierfür angegeben.

- 5. Diese Dissertation is vollständig meine eigene Arbeit, mit der Ausnahme solcher Zitate.

- 6. Alle wesentlichen Quellen von Unterstützung wurden benannt.

- 7. Wenn immer ein Teil dieser Dissertation auf der Zusammenarbeit mit anderen basiert, wurde von mir klar gekennzeichnet, was von anderen und was von mir selbst erarbeitet wurde.

- 8. Teile dieser Arbeit wurden zuvor veröffentlicht, ersichtlich im Abschnitt *Declaration of Publications and Contributions*.

# Declaration of Publications and Contributions

Parts of this thesis have already been published in peer-reviewed scientific journals.

Guido Trensch, Robin Gutzen, Inga Blundell, Michael Denker, Abigail Morrison (2018). Rigorous Neural Network Simulations: A Model Substantiation Methodology for Increasing the Correctness of Simulation Results in the Absence of Experimental Validation Data. Frontiers in Neuroinfor- matics 12, 81. doi:10.3389/fninf.2018.00081

#### Author contributions:

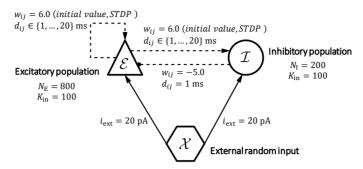

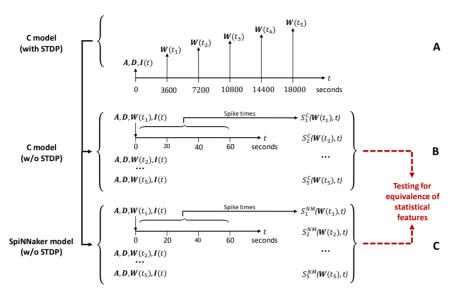

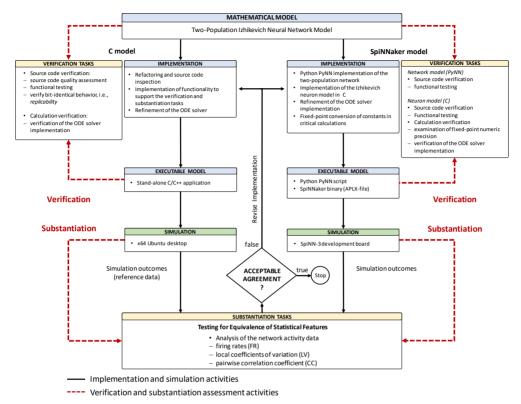

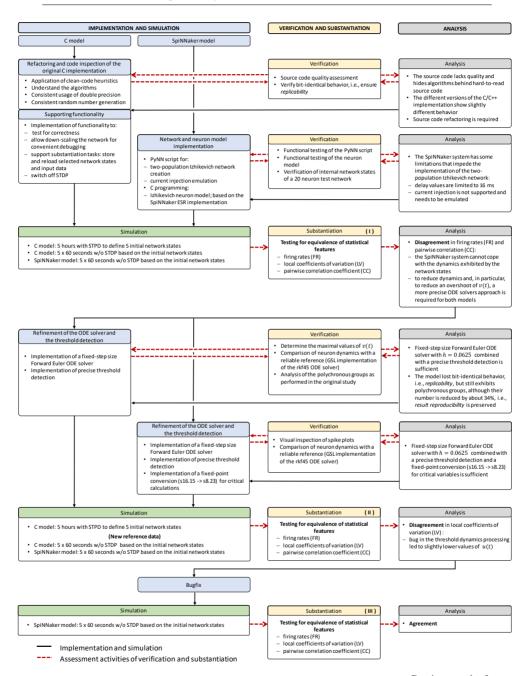

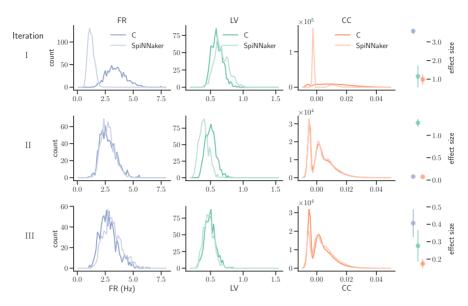

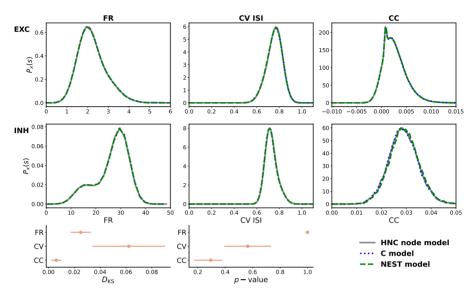

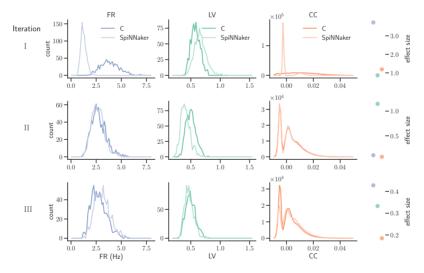

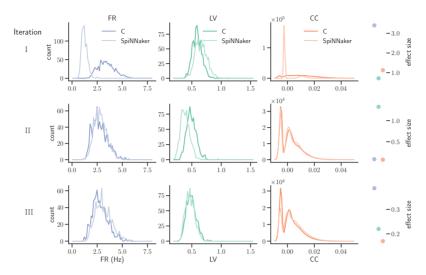

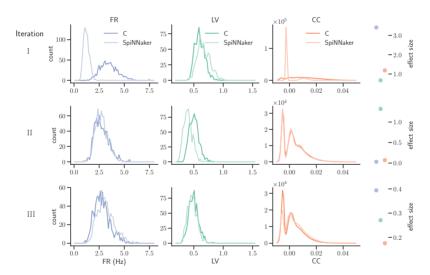

The author devised the project, developed the main conceptual ideas and workflows, performed the verification tasks, the implementation of the models and their refinement, and carried out the numerical simulations under the supervision of Abigail Morrison. Inga Blundell contributed expertise on numeric integration. Robin Gutzen, Michael Denker, Abigail Morrison, and the author established the terminology. Robin Gutzen and Michael Denker designed the statistical analysis, which was then performed by Robin Gutzen. Robin Gutzen and Michael Denker have also written the passage on analysis of network spiking activity. The author has revised this section for this thesis (Section 2.3.2.2) and added descriptions of the statistical measures used throughout this work. The figures showing the results of the model substantiation assessments have been created by Robin Gutzen and are used in this thesis (Figures 2.11, B1 – B5). All other figures are the author's own work. Chapter 2 of this thesis is based on this publication. Here, some passages are quoted verbatim, particularly passages defining and describing terminology.

Robin Gutzen, Michael von Papen, Guido Trensch, Pietro Quaglio, Sonja Grün, Michael Denker (2018). Reproducible Neural Network Simulations: Statistical Methods for Model Validation on the Level of Network Activity Data. Frontiers in Neuroinformatics 12, 90. doi:10.3389/fninf.2018.00090

#### **Author contributions:**

Robin Gutzen, Michael von Papen, Sonja Grün, Michael Denker and the author designed the

study. Robin Gutzen and Pietro Quaglio performed the analysis. The author performed the simulations and implemented the model. Robin Gutzen, Michael von Papen, and Pietro Quaglio wrote the software for performing the validations. All authors contributed to the writing of the manuscript. The project was supervised by Sonja Grün and Michael Denker. This study accompanied and complemented the above publication.

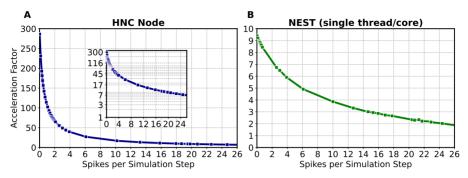

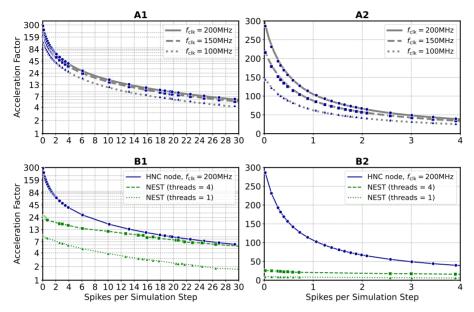

Guido Trensch, Abigail Morrison (2022). A System-on-Chip Based Hybrid Neuromorphic Compute Node Architecture for Reproducible Hyper-Real-Time Simulations of Spiking Neural Networks. Frontiers in Neuroinformatics 16. doi:10.3389/fninf.2022.884033

#### **Author contributions:**

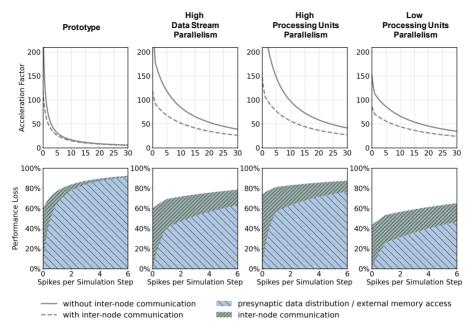

The author developed the System-on-Chip based hybrid neuromorphic compute node architecture, implemented the prototype, performed the hardware and software development, developed the workload and performance model, and carried out the experiments. The project was supervised by Abigail Morrison. Chapter 3 of this thesis is based on the architectural description presented in this publication. For this thesis, the author reworked and substantially expanded the content. The workload and performance model, and the results presented in this publication also formed the basis of Chapter 5.

Arne Heittmann, Georgia Psychou, Guido Trensch, Charls E. Cox, Winfried W. Wilcke, Markus Diesmann, Tobias G. Noll (2022). Simulating the Cortical Microcircuit Significantly Faster Than Real Time on the IBM INC-3000 Neural Supercomputer. Frontiers in Neuroscience doi:10.3389/fnins.2021.728460

#### **Author contributions:**

Arne Heittmann elaborated the concept of configurable spiking neural network (CsNN) simulations in cooperation with Tobias G. Noll, implemented and verified CsNN on the IBM Neural Computer INC-3000. Winfried W. Wilcke founded and leads the *Machine Intelligence* project at IBM Research, where the INC-3000 was designed and built. Charls E. Cox was the main hardware designer of the INC-3000 system. Georgia Psychou contributed by providing critical review, feedback, and proofreading of the manuscript. Markus Diesmann contributed to the initial draft and edited the manuscript. The author of this thesis has contributed to the validation and to the writing of the manuscript with the section on correctness. This section's description of statistical measures was revised and expanded for this thesis and is used in Section 2.3.2.2.

During the course of this dissertation, the author co-authored a publication that is related to this work but was not used in this thesis.

Inga Blundell, Romain Brette, Thomas A. Cleland, Thomas G. Close, Daniel Coca, Andrew P. Davison, Sandra Diaz-Pier, Musoles Carlos Fernandez, Padraig Gleeson, Dan F. M. Goodman, Hines Michael Michael, Michael W. Hopkins, Pramod Kumbhar, David R. Lester, Bóris Marin, Abigail Morrison, Eric Müller, Thomas Nowotny, Alexander Peyser, Dimitri Plotnikov, Paul Richmond, Andrew Rowley, Bernhard Rumpe, Marcel Stimberg, Alan B. Stokes, Adam Tomkins, Guido Trensch, Marmaduke Woodman, Jochen Martin Eppler (2018). Code Generation in Computational Neuroscience: A Review of Tools and Techniques. Frontiers in Neuroinformatics 12, 68. doi:10.3389/fninf.2018.00068

## **Author contributions:**

Inga Blundell, Abigail Morrison, Jochen Martin Eppler, and Dimitri Plotnikov have coordinated the work on this review paper. All authors contributed to the publication with sections from their respective areas of expertise. The author of this thesis has written passages on classical processors and accelerators.

| 1 | Intro                                                  | oductio                                                                    | n                                                                                  | 19                               |  |

|---|--------------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------|----------------------------------|--|

|   | 1.1                                                    | Motivation                                                                 |                                                                                    |                                  |  |

|   | 1.2 Spiking Neural Network Simulations in Neuroscience |                                                                            |                                                                                    |                                  |  |

|   |                                                        | 1.2.1                                                                      | Spiking Neurons                                                                    | 24                               |  |

|   |                                                        | 1.2.2                                                                      | Phenomenological Models                                                            | 26                               |  |

|   |                                                        | 1.2.3                                                                      | Digital Simulation                                                                 | 32                               |  |

|   |                                                        | 1.2.4                                                                      | Methods and Tools                                                                  | 34                               |  |

|   | 1.3                                                    | Neuro                                                                      | morphic Computing as Tool for Neuroscience                                         | 35                               |  |

|   |                                                        | 1.3.1                                                                      | Requirements                                                                       | 35                               |  |

|   |                                                        | 1.3.2                                                                      | Choice of Technology                                                               | 36                               |  |

|   |                                                        | 1.3.3                                                                      | Neuromorphic Developments                                                          | 37                               |  |

|   | 1.4                                                    | Contri                                                                     | butions                                                                            | 41                               |  |

|   | 1.5                                                    | Thesis                                                                     | Outline                                                                            | 42                               |  |

| 2 | Rigo                                                   | orous N                                                                    | leural Network Simulations: A Model Substantiation Methodology for                 |                                  |  |

|   |                                                        | easing t                                                                   | he Correctness of Simulation Results in the Absence of Experimental                | 45                               |  |

|   |                                                        | dation D                                                                   | he Correctness of Simulation Results in the Absence of Experimental                | <b>45</b> 46                     |  |

|   | Valid                                                  | dation D                                                                   | the Correctness of Simulation Results in the Absence of Experimental lata          |                                  |  |

|   | <b>Valid</b> 2.1                                       | dation D                                                                   | the Correctness of Simulation Results in the Absence of Experimental lata auction  | 46                               |  |

|   | <b>Valid</b> 2.1                                       | dation D<br>Introd                                                         | the Correctness of Simulation Results in the Absence of Experimental lata action   | 46<br>48                         |  |

|   | <b>Valid</b> 2.1                                       | Introde<br>Termin                                                          | the Correctness of Simulation Results in the Absence of Experimental lata auction  | 46<br>48<br>48                   |  |

|   | <b>Valid</b> 2.1                                       | Introduced Termin 2.2.1 2.2.2                                              | the Correctness of Simulation Results in the Absence of Experimental lata auction  | 46<br>48<br>48<br>49             |  |

|   | <b>Valid</b> 2.1                                       | Introde Termin 2.2.1 2.2.2 2.2.3 2.2.4                                     | the Correctness of Simulation Results in the Absence of Experimental lata action   | 46<br>48<br>48<br>49<br>51       |  |

|   | <b>Valid</b> 2.1 2.2                                   | Introduce Termin 2.2.1 2.2.2 2.2.3 2.2.4 Worke                             | the Correctness of Simulation Results in the Absence of Experimental lata  uction  | 46<br>48<br>48<br>49<br>51       |  |

|   | <b>Valid</b> 2.1 2.2                                   | Introduce Termin 2.2.1 2.2.2 2.2.3 2.2.4 Worker                            | the Correctness of Simulation Results in the Absence of Experimental lata function | 46<br>48<br>48<br>49<br>51<br>53 |  |

|   | <b>Valid</b> 2.1 2.2                                   | Introduction D Introduction Terminal 2.2.1 2.2.2 2.2.3 2.2.4 Worked on the | the Correctness of Simulation Results in the Absence of Experimental lata  uction  | 46<br>48<br>48<br>49<br>51<br>53 |  |

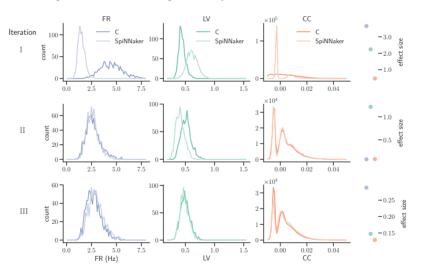

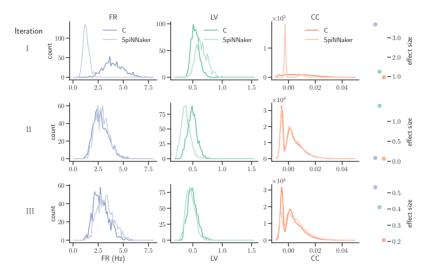

|   |     | 2.3.2             | Definition of the Model Substantiation Assessment                  | 56  |

|---|-----|-------------------|--------------------------------------------------------------------|-----|

|   |     |                   | 2.3.2.1 Experimental Setup                                         | 57  |

|   |     |                   | 2.3.2.2 Analysis of Network Spiking Activity                       | 58  |

|   |     | 2.3.3             | Definition of the Model Verification and Substantiation Workflow   | 60  |

|   |     | 2.3.4             | Application of the Method                                          | 62  |

|   |     |                   | 2.3.4.1 Iteration I: Source Code Verification                      | 62  |

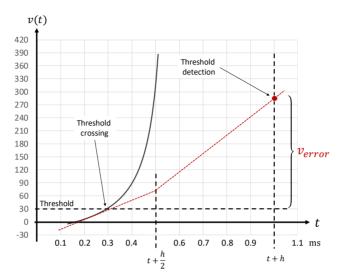

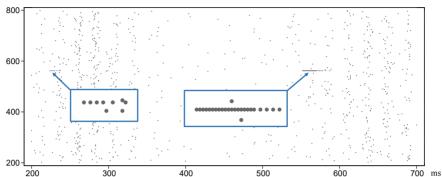

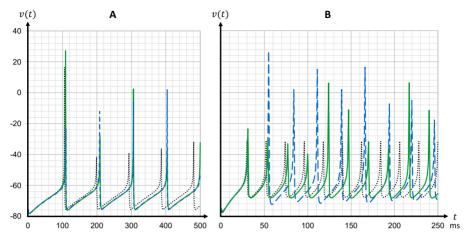

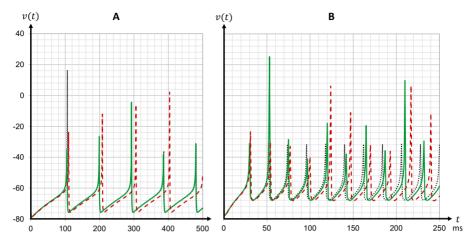

|   |     |                   | 2.3.4.2 Iteration II: Calculation Verification                     | 66  |

|   |     |                   | 2.3.4.3 Iteration III: Resolving an Implementation Issue           | 78  |

|   | 2.4 | Discus            | sion                                                               | 79  |

| 3 |     | -                 | on-Chip Based Hybrid Neuromorphic Compute (HNC) Node Ar-           |     |

|   |     | ecture 1<br>works | for Reproducible Hyper-Real-Time Simulations of Spiking Neural     | 85  |

|   | 3.1 |                   | action                                                             | 86  |

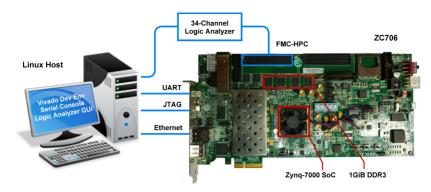

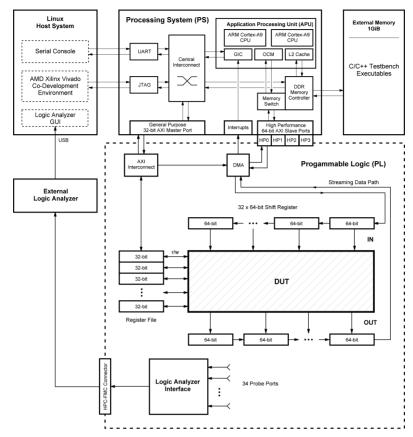

|   | 3.2 |                   | ppment Environment                                                 | 87  |

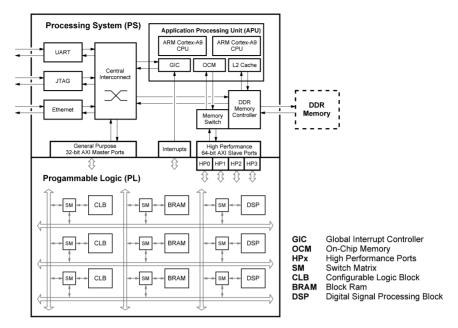

|   | 3.2 | 3.2.1             | Development Platform                                               | 87  |

|   |     | 3.2.2             | AMD Xilinx Zynq-7000 SoC Device Architecture                       | 88  |

|   |     | 3.2.3             | Co-development and Logic Design Methodology                        | 90  |

|   | 3.3 |                   | Node Architecture                                                  | 92  |

|   | 3.3 | 3.3.1             | Architecture Concept                                               | 92  |

|   |     | 3.3.2             | System-Level Architecture                                          | 95  |

|   |     | 3.3.3             | Software System                                                    | 99  |

|   |     | 0.0.0             | 3.3.3.1 Software System Architecture                               | 99  |

|   |     |                   | 3.3.3.2 Technical Concepts                                         | 100 |

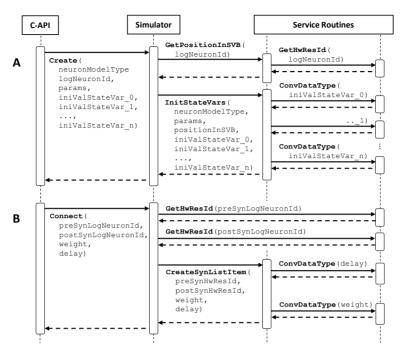

|   |     |                   | 3.3.3.3 Node-Local Network Instantiation                           | 103 |

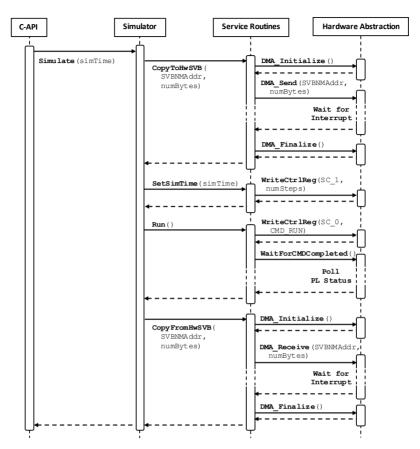

|   |     |                   | 3.3.3.4 Simulation                                                 | 104 |

|   |     |                   | 3.3.3.5 Recording                                                  | 106 |

|   |     |                   | 3.3.3.6 Interactive User Console Interface                         | 107 |

|   |     | 3.3.4             | Hardware Microarchitecture                                         | 107 |

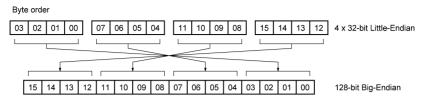

|   |     |                   | 3.3.4.1 Technical Concepts                                         | 108 |

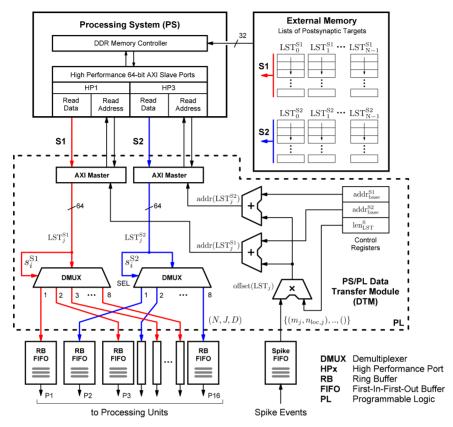

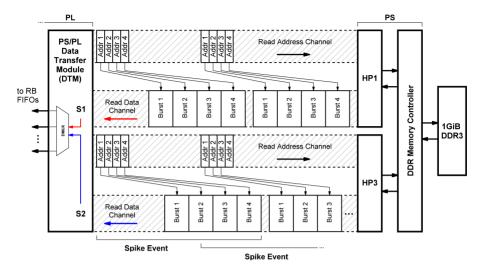

|   |     |                   | 3.3.4.2 Presynaptic Data Distribution – PS/PL Data Transfer Module | 111 |

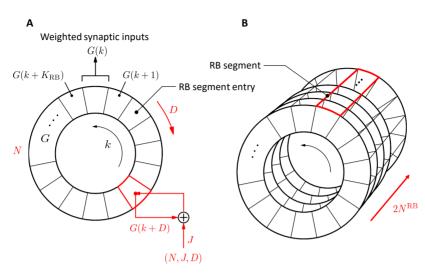

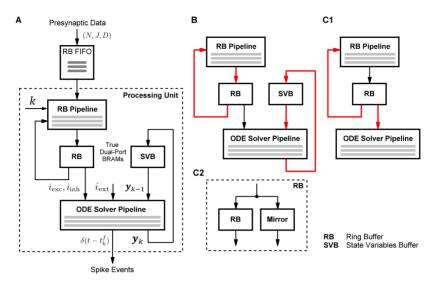

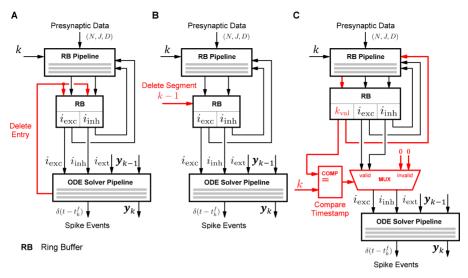

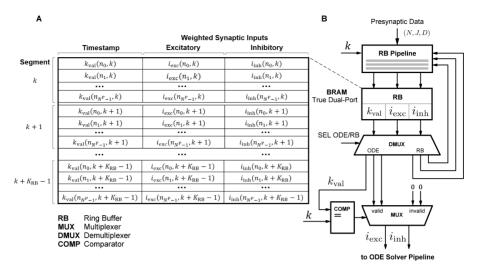

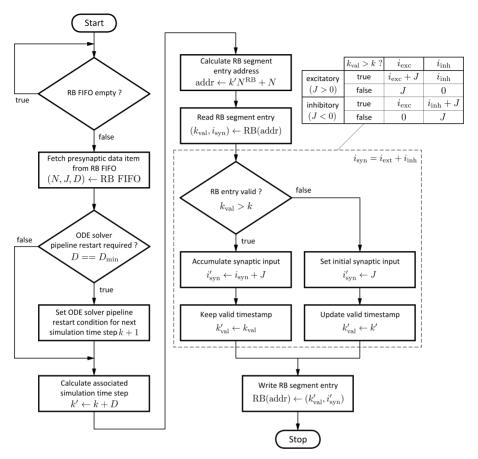

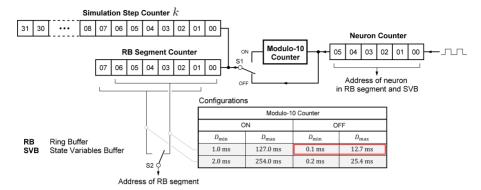

|   |     |                   | 3.3.4.3 Presynaptic Data Processing – Ring Buffers                 | 116 |

|   |     |                   | 3.3.4.3.1 Architecture Exploration                                 | 117 |

|   |     |                   | 3.3.4.3.2 The Implemented Architecture Design                      | 123 |

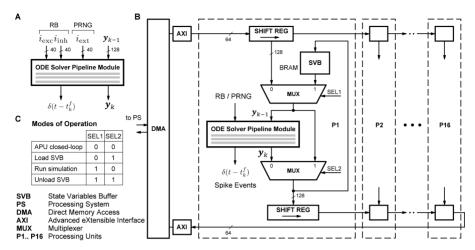

|   |     |          | 3.3.4.4    | Neuron a     | nd Synapse Model Update - ODE Solver Pipelines .   | 126   |

|---|-----|----------|------------|--------------|----------------------------------------------------|-------|

|   |     |          | 3          | 3.3.4.4.1    | Processing Unit Modes of Operation                 | 126   |

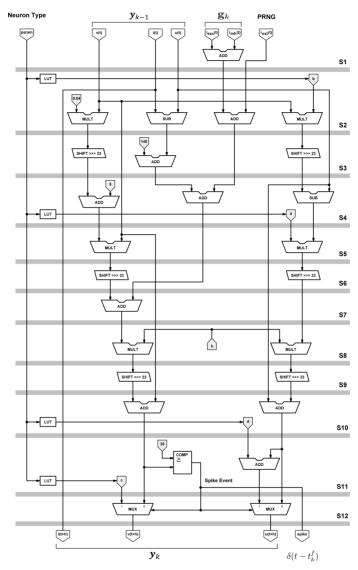

|   |     |          | 3          | 3.3.4.4.2    | Example Implementation: Izhikevich Neuron Mode     | 1 129 |

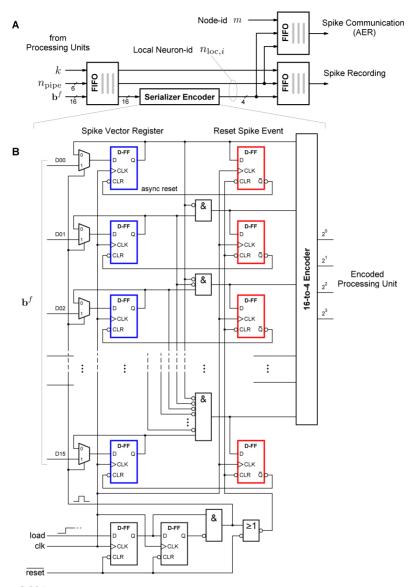

|   |     |          | 3.3.4.5    | Spike Eve    | ents Processing – Serializer and Encoder           | 133   |

|   |     |          | 3.3.4.6    | Synaptic     | Delay Resolution – Address Counters                | 135   |

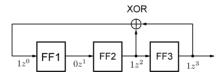

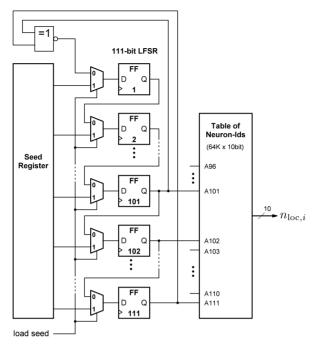

|   |     |          | 3.3.4.7    | Pseudo-R     | Random Number Generation                           | 137   |

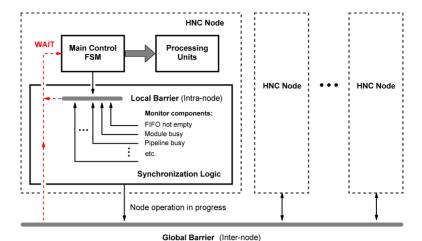

|   |     |          | 3.3.4.8    | Synchron     | nization                                           | 138   |

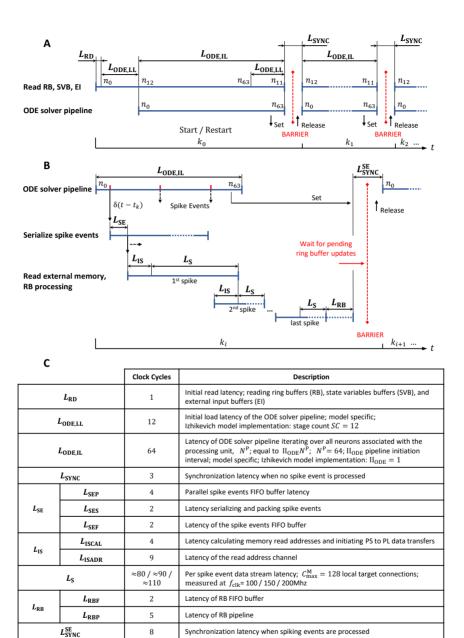

|   |     | 3.3.5    | Operation  | ng Latencies | s                                                  | 142   |

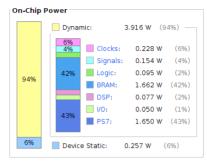

|   |     | 3.3.6    | Breakdo    | own of FPG   | A Resources and Power Consumption                  | 144   |

|   | 3.4 | Discus   | sion       |              |                                                    | 146   |

| 4 | HNC | : Node I | lmpleme    | entation Co  | orrectness                                         | 151   |

| • | 4.1 |          | -          |              |                                                    |       |

|   | 4.2 |          |            |              |                                                    |       |

|   |     | 4.2.1    |            |              | umerical Precision                                 |       |

|   |     | 4.2.2    |            | _            | n Scheme                                           |       |

|   | 4.3 |          |            | _            | 1                                                  |       |

|   |     | 4.3.1    |            |              | FPGA verification                                  |       |

|   |     | 4.3.2    |            |              | on Tests                                           |       |

|   | 4.4 | Results  |            |              |                                                    |       |

|   | 4.5 |          |            |              |                                                    |       |

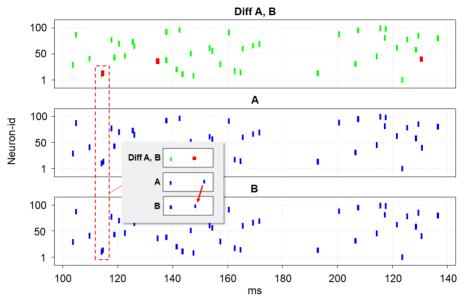

|   |     | 4.5.1    | Definition | on of the Su | ubstantiation Entities                             | 160   |

|   |     | 4.5.2    | Quantita   | ative Compa  | arison of Statistical Measures                     | 162   |

|   | 4.6 | Discus   | sion       |              |                                                    | 163   |

| 5 | HNC | Node I   | Performa   | ance         |                                                    | 167   |

|   | 5.1 |          |            |              |                                                    | 168   |

|   | 5.2 |          |            |              |                                                    |       |

|   |     | 5.2.1    |            |              |                                                    |       |

|   |     | 5.2.2    | Perform    | ance Model   | 1                                                  | 171   |

|   | 5.3 | Results  | s          |              |                                                    | 174   |

|   |     | 5.3.1    |            |              | mance                                              |       |

|   |     | 5.3.2    | _          |              | cteristics for Different Sets of Design Parameters |       |

|   | 5.4 | Discus   |            |              |                                                    |       |

| 6                                    | Towa   | ard Lar | ge Scale                                              | 187  |  |  |  |

|--------------------------------------|--------|---------|-------------------------------------------------------|------|--|--|--|

|                                      | 6.1    | Introdu | action                                                | 188  |  |  |  |

| 6.2 Arch                             |        |         | itectural Enhancements                                |      |  |  |  |

|                                      |        | 6.2.1   | Further Parallelization Options                       | 189  |  |  |  |

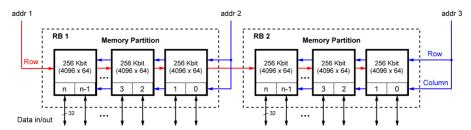

|                                      |        | 6.2.2   | Memory Partitioning                                   | 191  |  |  |  |

|                                      | 6.3    | Perform | nance Estimation                                      | 197  |  |  |  |

|                                      |        | 6.3.1   | Measure of Workload                                   | 197  |  |  |  |

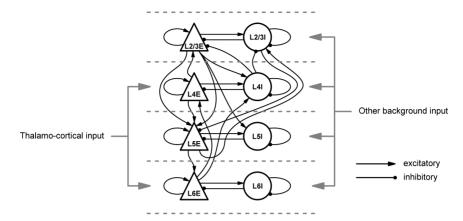

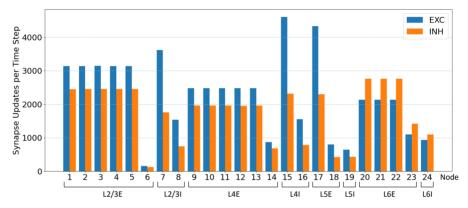

|                                      |        | 6.3.2   | Workloads of Large-Scale Networks                     | 198  |  |  |  |

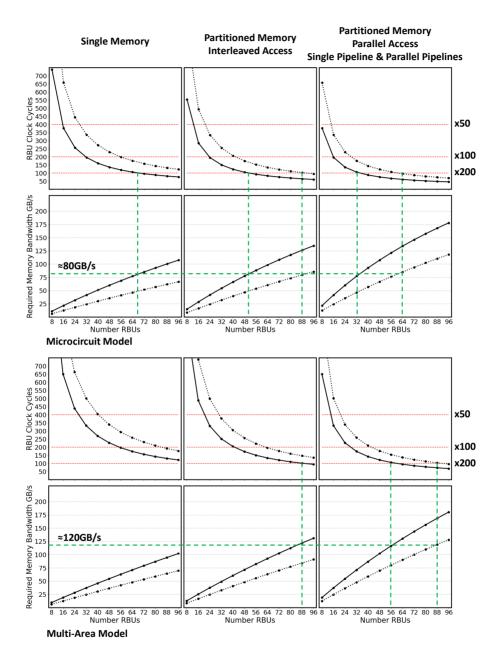

|                                      |        | 6.3.3   | Achievable Acceleration and Required Memory Bandwidth | 205  |  |  |  |

|                                      | 6.4    | System  | Integration                                           | 209  |  |  |  |

|                                      | 6.5    | Discus  | sion                                                  | 211  |  |  |  |

| 7                                    | Dies   | ussian  | and Outlook                                           | 213  |  |  |  |

| ′                                    | 7.1    |         | isions                                                | 214  |  |  |  |

|                                      | 7.1    |         | ary and Discussion                                    | 215  |  |  |  |

|                                      | 7.2    |         | k                                                     | 218  |  |  |  |

|                                      | 1.5    | Outloo  | · · · · · · · · · · · · · · · · · · ·                 | 210  |  |  |  |

| Аp                                   | pend   | ix A    | Two-Population Izhikevich Network Model               | I    |  |  |  |

| Αp                                   | pend   | ix B    | Model Substantiation Assessment                       | ٧    |  |  |  |

| Αp                                   | pend   | ix C    | Control Registers                                     | IX   |  |  |  |

| Appendix D Connection Data Structure |        |         |                                                       | ΧI   |  |  |  |

| Αp                                   | pend   | ix E    | Monte Carlo Simulations                               | XIII |  |  |  |

| No                                   | men    | clature |                                                       | χV   |  |  |  |

| Lis                                  | t of F | igures  |                                                       | XX   |  |  |  |

| Lis                                  | t of T | Tables  |                                                       | XXII |  |  |  |

| Bil                                  | oliogi | aphy    |                                                       | XXI\ |  |  |  |

# **Chapter 1**

# Introduction

# 1.1 Motivation

Over the past century, an enormous body of knowledge has been accumulated about the structure and function of the nervous system and the brain. Our understanding of neurobiology has become increasingly precise and has been incorporated into neuroscience, which evolved into an academic discipline in its own right. In 1952, Alan Lloyd Hodgkin and Andrew Huxley presented a mathematical model that describes how action potentials in neurons of the giant axon of a squid are initiated and propagated (Hodgkin and Huxley, 1952). The Hodgkin-Huxley model is central to neuroscience research, and the authors received the 1963 Nobel Prize in Physiology or Medicine for their work. In 1961, Richard FitzHugh suggested a simplified version of this model, replacing the four equations of Hodgkin and Huxley by two (FitzHugh, 1961). An equivalent electrical circuit was presented in 1962 by Jinichi Nagumo (Nagumo et al., 1962). The model is therefore known as the FitzHugh-Nagumo model. In the same year, Bernard Katz modeled neurotransmission across nerve cells (neurons) and uncovered fundamental properties of synapses, the junctions between nerve cells that allow a signal to pass from one neuron to another. In the 1960s and 1970s, David Hubel and Torsten Wiesel greatly expanded our knowledge of sensory processing and the development of the visual system in a number of fundamental studies (Hubel and Wiesel, 2005). Beginning in 1966, Eric Kandel and collaborators studied biochemical changes in neurons associated with learning and memory in Aplysia and identified the physiological changes that occur in the brain during the formation and storage of memories (Kandel, 2007). How learning and information storage is achieved in the brain is still one of the central questions to neuroscience. Research in this area is heavily influenced by Hebb's 1949 postulate (Hebb, 1949), which states that a correlated activity of two neurons strengthens their synaptic connection.

During the second half of the twentieth century, advancements in molecular biology and technical innovations such as patch-clamp electrophysiology significantly increased scientific study (Altimus et al., 2020). In particular, the incredible technological progress in computer technology we have seen over the past five decades has accelerated neuroscience research. Computerized models of neurons and neural networks have made significant contributions here – and continue to do so. Computational neuroscience is still a young but rapidly growing area within the field of neuroscience, involving a variety of disciplines including mathematics, physics, computer science, and engineering. Supercomputers, with their unprecedented computational power, have become indispensable tools in today's neuroscience research with a broad range of applications. For example, in neuroimaging, which aims to understand the microscopic organization and detailed anatomy of the brain, supercomputers are used to analyze big data

sets (e.g., Axer and Amunts, 2022). Research on the principles of brain structure, dynamics, and function uses supercomputers to simulate large neural networks – networks with millions of neurons and billions of synapses.

Despite the great strides neuroscience has made in recent decades, the underlying principles of how the brain works are still largely unknown. Chris Eliasmith notes in his book *How to Build a Brain:* "An answer that picks out the parts of the brain that have increased activity while reading words, or an answer that describes what chemicals are in less abundance when someone is depressed, is not what we have in mind. Certainly these observations are all part of an answer, but none of them traces the path from perception to action ..." (Eliasmith, 2013). The ultimate goal remains to understand consciousness and the underlying mechanisms by which we perceive, learn, act, and remember.

The human brain contains nearly 86 billion neurons, with each neuron in the neocortex forming on the order of 10,000 synapses with other neurons. While the human brain consumes about the same amount of power as a light bulb, the power consumption of a supercomputer is five orders of magnitude larger, in the megawatt range. The von Neumann architecture of today's computers physically separates computation from storage. In brains, no conceptual or physical distinction is made here. Data processing and storage are performed in a distributed manner by complex networks of nerve cells. The brain's efficiency, computational capabilities, processing speed, and robustness to noise and malfunction is unique. From the earliest days of computing, this encouraged engineers to profitably apply brain principles in the design of machines. An early example is the *Mark I Perceptron* machine, built in 1957 at the Cornell Aeronautical Laboratory by Frank Rosenblatt (Cornell Aeronautical Laboratory Inc., 1960). Because of his pioneering work on artificial neural networks, Frank Rosenblatt is today recognized as one of the fathers of deep learning (Tappert, 2019).

Since then, a plethora of brain-inspired computers and devices have been built. They are used to model neuroscience theories and to solve machine learning tasks. The field of neuromorphic computing, as we are calling it today, is evolving at an incredible pace, where the research on neuromorphic algorithms and applications is becoming more and more of an important area. The term *neuromorphic* emerged in the late 1980s and it is closely associated with Carver Mead, a pioneer of modern microelectronics, who popularized the term with his 1990 publication entitled *Neuromorphic Electronic Systems* (Mead, 1990). Carver Mead also published the first book on neuromorphic computing, in which he describes electronic analog circuits to mimic neurobiological architectures found in the nervous system (Mead, 1989). Today, the term *neuromorphic computing* or *neuromorphic engineering* is much more broadly defined. We use it to refer to brain-inspired analog circuits and devices in the tradition of Carver Mead, such

as the neuron circuits developed by Giacomo Indiveri and his group (Indiveri et al., 2011), as well as advanced computer architectures that are inspired by brain principles or are dedicated to neuroscience simulation, such as the SpiNNaker neuromorphic system (Furber and Bogdan, 2020).

The main driver for most neuromorphic developments is undoubtedly brain-inspired computing aiming at solving real-world tasks, where it draws inspiration from insights from neuroscience. The application of neuromorphic computing in neuroscience research, however, is a niche area, although there is great interest in its application in modeling and simulation. Progress in neuroscience research depends to a large extent on the ability to study large neural networks and perform complex simulations. Performing simulations in hyper-real time is of great interest here, as it would allow comprehensive parameter scans and the study of slow processes such as learning and long-term memory. However, even the fastest and most advanced supercomputers available today cannot meet the challenge of significantly accelerating the simulation of a large-scale network. Neuromorphic computing, leveraging novel technologies and application-specific hardware architectures, is therefore an attractive option that promises to provide the necessary tools for this task.

Despite all technological innovations, making neuromorphic computing a useful tool for neuroscientists is a demanding technical challenge. Neuroscience research employs mathematical models to gain understanding of the complex dynamics of neural networks. Their simulation requires numerical accuracy. Judging the correctness of a simulation outcome is often difficult, even for domain experts. Methods for building credibility, such as verification and validation, have been developed and are common practice in engineering disciplines, but they are not yet well established in the field of neural network modeling and simulation. Deriving appropriate design decisions for the implementation of numerical operations and algorithms can be hampered by this. Neuroscience simulation also uses a wide variety of neuron and synapse models. Besides the requirement for accuracy, there is therefore also a need for flexibility. At a technical level, flexibility conflicts with the objective of achieving efficiency, which is tied to the goal of accelerated simulation. In addition, a neuromorphic system dedicated to neuroscience must also integrate with the existing landscape of tools and workflows for modeling and simulation in order to attain user acceptance.

To date, there is no neuromorphic system available to neuroscientists that can meet all criteria equally while achieving significant acceleration. A system capable of speeding up the simulation of a large-scale neural network by a factor of 100 with respect to the biological time domain would be a major breakthrough.

Developing such a system based on application-specific integrated circuits (ASICs) is a

time-consuming and costly process. A promising alternative is commercial off-the-shelf chip technology, integrating programmable logic, such as field-programmable gate arrays (FPGAs), along with general-purpose processors and memory in a single device called a System-on-Chip (SoC). This technology has the potential to provide the substrate to take neuromorphic computing as a tool for neuroscience to the next level without costly chip development.

The objectives of this thesis are:

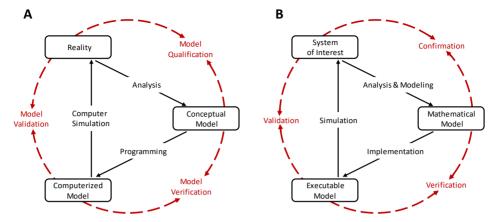

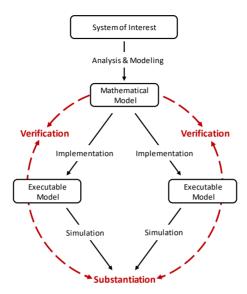

- to introduce the concept of *model verification and substantiation* as a methodology for accumulating evidence of a model's plausibility and correctness, even in the absence of experimental validation data;

- to demonstrate a rigorous model verification and validation process, including an investigation of the required numerical precision on the SpiNNaker neuromorphic system;

- to develop and evaluate a novel FPGA-SoC-based neuromorphic compute node architecture

capable of performing simulations in hyper-real-time, with the design strictly driven by

neuroscience requirements, as a complementary yet distinct approach to the neuromorphic

developments aiming at brain-inspired novel computer architectures for solving real-world

tasks:

- to explore commercial off-the-shelf FPGA-SoC device technology and investigate its suitability as substrate for neuromorphic computing for application in computational neuroscience, in modeling and simulation; and

- to examine the technical requirements for large-scale neuromorphic computing and to propose a concept for a neuromorphic system integration that incorporates high-performance computing (HPC), taking into account the existing tools and workflows for modeling and simulation.

# 1.2 Spiking Neural Network Simulations in Neuroscience

This section introduces elementary notions of neurobiology and the basic concepts of numerical simulation of spiking neural networks in computational neuroscience. A comprehensive introduction to the complex fields is beyond the scope of this thesis. The presentation in this section is therefore highly selective, focusing on those aspects necessary for further understanding.

# 1.2.1 Spiking Neurons

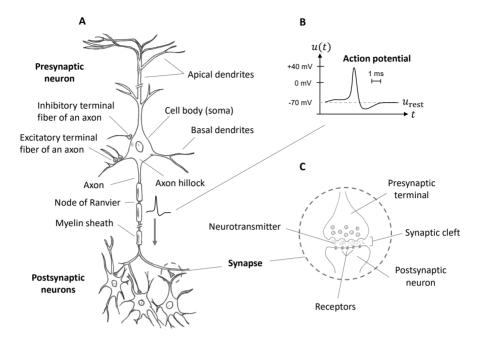

Neurons are the primary functional units of the nervous system. They generate electrical signals that convey information. There are many different types of neurons, but most of them share the same main features. A typical neuron can be divided into three distinct parts: a cell body; dendrites; and an axon. These three parts are anatomically separate and serve different purposes. A schematic drawing of a neuron is shown in Figure 1.1A. The cell body (Greek soma) performs the essential life functions of a neuron by supporting all its chemical processes. Dendrites are projections from the soma, cellular extensions with many branches. Their function is to receive signals from other neurons or sensory information from the environment. The axon is a cable-like projection, the component of the neuron that conveys the electrical signals generated by the neuron and received by other neurons. These signals are all-or-none impulses, called *action potentials* or *spikes* (Figure 1.1B). Axons can vary greatly in length, ranging from 0.1 mm to 3 m (Kandel et al., 2000). Long axons are coated with an insulating sheath of myelin that is interrupted at regular intervals by the *nodes of Ranvier*. Action potentials traveling down the axon regenerate at these uninsulated spots, preventing signal degradation.

The branches of a neuron's axon form connections to many other neurons, the recipients of the signals. The point at which two neurons communicate is called a *synapse*. Accordingly, the neuron transmitting an action potential is called the *presynaptic neuron* and the neuron that is receiving this signal is called the *postsynaptic neuron*. Figure 1.1C shows a schematic drawing of a chemical synapse, which is the most common synapse type<sup>1</sup>. Axon branches end in what are called *presynaptic terminals*. They attach to the dendrites (and also the cell bodies) of the postsynaptic neurons, where they form synapses. At these contact points pre- and postsynaptic neuron are anatomically separated by a tiny space, the *synaptic cleft*.

A synapse translates electrical stimuli into chemical signals, i.e., the release of neurotransmitters from the presynaptic terminal into the synaptic cleft. The neurotransmitter molecules are detected by receptors in the postsynaptic cell membrane, where they open specific channels that initiate an ionic current flow into the cell. This current flow produces a so-called *postsynaptic potential* (PSP) and gradually changes the electrical charge of the neuron. A synapse here can be excitatory (the change in charge is positive) or inhibitory (the change in charge is negative), where a neuron forms either excitatory or inhibitory synaptic connections at all of its axonal branches. This is a consequence of *Dale's principle*, after Sir Henry Dale, a British physiologist who, in 1935, stated that a neuron performs identical chemical actions at all of its synaptic connections to other cells.

<sup>&</sup>lt;sup>1</sup>Apart from chemical synapses, some operate purely electrical. These are called gap junctions.

**Figure 1.1** | **Structure of a neuron.** (**A**) Structure of a neuron schematically redrawn after Kandel et al. (2000) and modified. A neuron can be divided into three distinct parts: a cell body (soma), dendrites, and an axon (see main text for a description of their function). (**B**) Neurons generate stereotyped, uniform electrical signals, called *action potentials*. (**C**) The branches of a neuron's axon form communication sites with many other neurons. The point at which two neurons communicate is called a *synapse*. Shown here is a schematic drawing of a chemical synapse.

Synapses are dynamic plastic elements whose behavior is shaped by the previous history of both presynaptic and postsynaptic activity. Changes in synaptic signal transmission arise from a number of synaptic plasticity mechanisms, which gives synapses an active role in information processing (Abbott and Regehr, 2004).

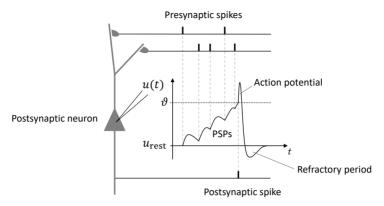

A neuron maintains an electrochemical gradient between the inside and the outside of the cell, resulting in an electrical charge of the neuron. The synaptic inputs of a neuron continually change this charge. This can be measured by injecting an electrode into the neuron's cell body, recording the voltage across the cell membrane. The sketch in Figure 1.2 illustrates this. At its resting state, to which a neuron always tends to return, this membrane voltage, or *membrane potential*, has a value of approximately –70 mV (Dayan et al., 2005) (see also Figure 1.1B); the cell membrane here has a strong negative polarization. If the membrane potential exceeds some threshold value,

**Figure 1.2** | **Neuronal dynamics.** The membrane potential u(t) of a postsynaptic neuron changes depending on the synaptic input; here an excitatory input from two presynaptic neurons. Each incoming spike event evokes a postsynaptic potential (PSP), which decays over time. When the membrane potential exceeds some threshold value  $\vartheta$ , the neuron generates an action potential; it emits a spike. After a refractory period, during which the neuron is unable to generate another action potential, the membrane potential returns to the resting state  $u_{\text{rest}}$ .

i.e., the synaptic input (the superposition of PSPs) is strong enough, the neuron generates an action potential; the neuron emits a *spike*. After emitting a spike, the neuron enters a refractory period during which it is unable to generate another action potential. One could also say that a neuron *integrates* incoming excitatory and inhibitory signals into a single cell response.

In the nervous system, billions of neurons work together forming complex communication networks. To study these networks, computational neuroscience uses mathematical models and numerical simulations.

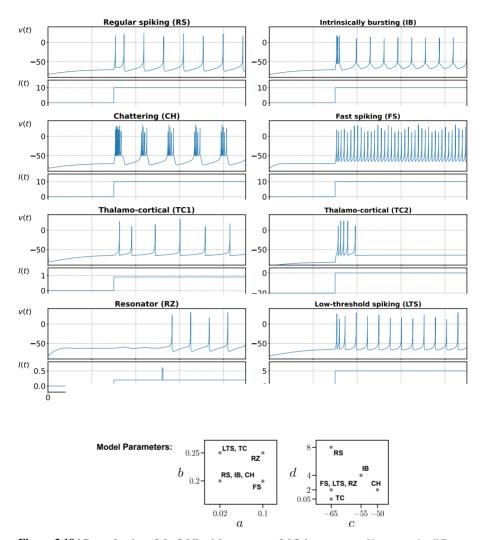

# 1.2.2 Phenomenological Models

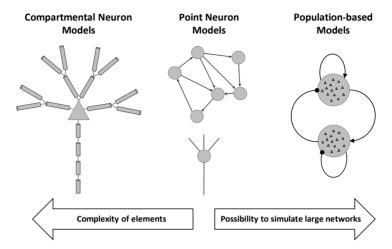

Depending on the scientific question, computational neuroscience employs different types of models with different levels of abstraction and complexity. Figure 1.3 compares three categories of models that use different abstraction: compartmental neuron models; point neuron models; and population-based models. Compartmental neuron models include the morphology of neurons, i.e., the spatial structure of dendritic trees and axons, which they decompose into many compartments. They can represent the electrophysiological properties of neurons with a high degree of accuracy, but due to their intrinsic complexity, their simulation comes at a very high computational cost. Point neuron models are not morphologically detailed. They are less complex and reduce a neuron to a single compartment, where the modeling of neuronal dynamics is grounded in

**Figure 1.3** | **Model classes with different levels of abstraction.** In computational neuroscience, different types of models are employed. Here three levels of abstraction and complexity are shown. Compartmental neuron models are morphologically detailed. Correspondingly, these models are complex. Point neuron models reduce this complexity by modeling selected phenomenological properties. An even higher level of abstraction is used in population-based models, which describe the coarse-grained activity of large populations of neurons sharing the same properties. The computational cost of simulation increases with the complexity of a model, the amount of detail it contains. Reducing complexity, in turn, reduces computational cost, allowing the simulation of larger networks.

phenomenological properties. Point neuron models are suited for studies of network dynamics and memory. The reduction in complexity allows the simulation of larger spiking neural networks. A high level of abstraction is used in population-based models. These models describe the coarse-grained activity of populations of neurons sharing the same properties. Population-based models contain less detail, but allow for the simulation at a large scale.

The variety of models used in computational neuroscience is large (see, e.g., Gerstner et al., 2014; Dayan et al., 2005), and new models are being added continually. In this thesis, only point neuron models are considered. The neuromorphic compute node that is presented in Chapter 3 was developed with the objective of hyper-real-time simulation of networks of neurons belonging to this specific category of models.

In order to give an example of a basic point neuron model, the leaky integrate-and-fire (LIF) model is presented in the following. In addition, for a more thorough picture, a simple synapse model is also described, and some technical aspects of simulation are explained. Another point neuron model, the Izhikevich neuron model, will be described in Section 2.3.1.1.

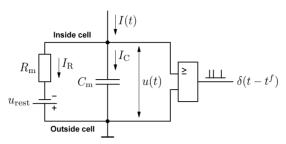

Figure 1.4 | Equivalent circuit diagram of the LIF neuron model. The capacitor  $C_{\rm m}$  acts like the cell membrane. The voltage u(t) across the capacitor is representing the membrane potential. In absence of an input current I(t), the capacitor charges to the voltage  $u_{\rm rest}$ . The *neuron* is then in the resting state, with the membrane potential  $u(t) = u_{\rm rest}$ . A positive input current increases the charge of the capacitor. When u(t) reaches the threshold  $\theta$ , a spike event is generated. Spike events are represented as Dirac pulses  $\delta(t-t^f)$ , where  $t^f$  is the time at which a spike event occurs. If the driving current I(t) vanishes, u(t) returns to the resting value with the time constant  $R_{\rm m}C_{\rm m}$ , where  $R_{\rm m}$  represents the neuron's membrane resistance.

## Leaky integrate-and-fire (LIF) neuron model

The concept of the LIF model can be traced back to Louis Lapicque, a French physiologist, who, in 1907, published a study in which he introduces a model of electrical excitation of nerves that is based on a capacitor (Lapicque, 1907; Brunel and Van Rossum, 2007b,a). The LIF model is one of the simplest models and widely used in computational neuroscience.

The model describes neuronal dynamics as an integration process combined with a mechanism to trigger an action potential when the membrane voltage reaches some threshold. Action potentials are reduced to *events*, exploiting the fact that they always have roughly the same stereotyped shape. The model can be expressed as an RC-circuit. The circuit diagram is shown in Figure 1.4.

**Subthreshold dynamics:** The LIF model characterizes a neuron by a membrane voltage u(t) that has a resting value  $u_{\text{rest}}$  (the resting potential of the neuron), a membrane capacitance  $C_{\text{m}}$  (the integrator), and a membrane resistance  $R_{\text{m}}$  (the leakage). Synaptic input is represented by an injected current I(t). By applying Kirchhoff's law we can write I(t) as

$$I(t) = I_{\mathcal{C}} + I_{\mathcal{R}},\tag{1.1}$$

where  $I_{\rm C}$  is the current that charges the capacitor  $C_{\rm m}$ , and  $I_{\rm R}$  is the current that passes through the resistor  $R_{\rm m}$ . From Equation (1.1), using Ohm's law and the capacitor equation  $I_{\rm C} = C_{\rm m} \frac{du}{dt}$ , we derive

$$I(t) = C_{\rm m} \frac{du}{dt} + \frac{u(t) - u_{\rm rest}}{R_{\rm res}}.$$

(1.2)

The standard form of the model (see, e.g., Gerstner et al., 2014) rewrites Equation (1.2) as

$$\tau_{\rm m} \frac{du}{dt} = u_{\rm rest} - u(t) + R_{\rm m} I(t), \tag{1.3}$$

where  $\tau_{\rm m}$  is interpreted as the membrane time constant with  $\tau_{\rm m} = R_{\rm m} C_{\rm m}$ , the time constant of the *leaky integrator*. The linear differential Equation (1.3) describes the evolution of the membrane potential u(t); in electrical terms, it describes the voltage response of the RC-circuit to an input current.

**Threshold and refractory:** The generation of action potentials is modeled as an artificial process. Action potentials are expressed as events that happen at precise times  $t^f$ , that is, when the membrane potential u(t) reaches the threshold value  $\vartheta$  from below. This gives the threshold conditions for the emission of the fth (f = 1, 2, ...) spike at time  $t^f$  as

$$t^f: u(t^f) \ge \vartheta \text{ and } t^f = \{t | u(t) \ge \vartheta\}.$$

(1.4)

When a spike event has occurred, the model enters a refractory period and is reset

$$\forall f, \ \forall t \in \left(t^f, t^f + \tau_{\text{ref}}\right]: \quad u(t) = u_{\text{reset}}. \tag{1.5}$$

In Equation (1.5),  $\tau_{\text{ref}}$  denotes the absolute refractory time, and  $u_{\text{reset}}$  is the membrane reset potential, for which  $u_{\text{reset}} < \vartheta$  has to apply.

*Spike events:* A spike event is represented as an infinitely tall pulse in the form of the Dirac  $\delta$ -function  $\lim_{t \to t^f} \delta(t - t^f) = \infty$ . A *spike train* can thus be denoted as a sequence of spike times

$$s(t) = \sum_{f} \delta(t - t^f). \tag{1.6}$$

The LIF model (Equation (1.3)) describes the voltage response to the time-dependent input current I(t), the driving synaptic input. As an example of how this input is derived, the following describes a simple synapse model. This synapse model will use an alpha-function to shape synaptic inputs.

## Current-based alpha-shaped synapse

Generally, synapse models can be divided into two basic types: conductance-based (COBA); and current-based (CUBA) models. The former respond to a presynaptic spike with a postsynaptic

potential (PSP), the latter with a postsynaptic current (PSC). The model presented here as an example is a current-based model frequently used in computational neuroscience.

The model describes the time course of a PSC by the alpha-function

$$\alpha(t) = \frac{t}{\tau_s} e^{1 - t/\tau_s} \Theta(t), \tag{1.7}$$

which exponentially rises and decays with the time constant  $\tau_s$ , the synaptic time constant. In Equation (1.7),  $\Theta$  is the Heaviside step function with  $\Theta(t) = 1$  for t > 0 and  $\Theta(t) = 0$  else. The use of an alpha-function here accounts for the low-pass characteristics of synaptic transmission. The PSC that a spike event evokes in a postsynaptic neuron is derived by multiplying the alpha-function by a factor. A PSC is then given as

$$PSC_{ij}(t) = w_{ij}\alpha(t), \tag{1.8}$$

where the factor  $w_{ij}$  determines the amplitude of the PSC, specifying the synaptic weight, i.e., the strength of the synaptic connection between the presynaptic neuron j and the postsynaptic neuron i. For a positive  $w_{ij}$ , the PSC is positive and the synapse is excitatory; a spike event induces an excitatory postsynaptic current (EPSC). If  $w_{ij}$  is negative, the PCS is negative and the synapse is inhibitory; a spike event results in an inhibitory postsynaptic current (IPSC). The superposition of PSCs gives the total synaptic input current of a neuron i, which can be formulated as

$$I_i(t) = \sum_j (PSC_{ij} * s_j)(t - d_{ij}).$$

(1.9)

In Equation (1.9),  $s_j(t)$  denotes the spike train of the presynaptic neuron j according to Equation (1.6),  $d_{ij}$  is the synaptic transmission delay from the presynaptic neuron j to the postsynaptic neuron i, which accounts for the dendritic and axonal delays of the connection, and "\*" is the convolution operator, which is defined as

$$(f * g)(t) = \int_{-\infty}^{\infty} f(s)g(t-s) ds.$$

(1.10)

The modeling of synapses has a technical aspect that requires explanation, as it is relevant for digital simulation and thus for the architecture of a neuromorphic accelerator.

Each synapse, i.e., each PSC-kernel, can in principle have a different time constant  $\tau_s$ . Technically, in a simulation, this would require a neuron to maintain a PSC for each of its incoming

connections, resulting in an enormous computational cost and memory requirement when simulating a large network. Therefore, implementations typically use only two synaptic time constants per neuron, one for excitatory and one for inhibitory synapses, reducing the number of PSCs to be maintained to two. This is a generally accepted simplification, which allows a postsynaptic neuron to lump together the weighted spike trains of all excitatory presynaptic neurons, and lump together the weighted spike trains of all inhibitory presynaptic neurons. Thus, in a simulation, synaptic weights can be accumulated at spike arrival time and the combined effect of all synapses can then be incorporated into the model dynamics (see Rotter and Diesmann, 1999).

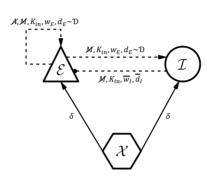

We can reformulate Equation (1.9) as two equations that divide the synaptic input current into an excitatory  $\mathcal{E}$  component (the superposition of EPSCs)

$$I_{\mathcal{E},i}(t) = \alpha(t, \tau_s = \tau_{\mathcal{E}}) \sum_{j \in \mathcal{E}} (w_{ij} * s_j)(t - d_{ij}), \tag{1.11}$$

and an inhibitory I component (the superposition of IPSCs)

$$I_{I,i}(t) = \alpha(t, \tau_s = \tau_I) \sum_{j \in I} (w_{ij} * s_j)(t - d_{ij}),$$

(1.12)

where  $\tau_E$  and  $\tau_I$  denote the synaptic time constants of excitatory and inhibitory synapses, respectively. The total synaptic input current of a neuron *i* is then given by

$$I_i(t) = I_{\mathcal{E},i}(t) + I_{\mathcal{T},i}(t).$$

(1.13)

LIF models with current-based synapses have an advantage in digital simulations. They allow exact integration (see, e.g., Rotter and Diesmann, 1999; Morrison et al., 2007). However, this is generally not the case for the majority of models. The dynamical systems that the mathematical models of neurons and synapses describe are typically nonlinear and require numerical methods for their solution.

Mathematical models of neurons and synapses are the basis for the construction of network models, which arrange neurons into populations, and connect populations to cortical circuits, and cortical circuits to brain areas, and so forth. These models can be supplemented with further phenomenological properties, for instance the description of topologies and rules for plasticity (a spike-timing-dependent plasticity (STDP) rule is described in Section 2.3.1.1). Due to their nonlinear and complex nature, digital simulation is the tool of choice to study these systems.

# 1.2.3 Digital Simulation

Digital simulation plays a key role in gaining insight into the underlying principles of neural computation. It enables neuroscientists to study the interaction of neurons and synapses and the complex dynamics that arise when large numbers of them are connected into networks.

When simulating a dynamical system on a digital computer, we generally have to differentiate between a *discrete-time* simulation and a *discrete-event* simulation. In a discrete-time simulation, the time axis is divided into evenly spaced intervals, a time grid. A continuously evolving system is then advanced in steps using discrete-time approximation methods – state changes are considered at specific points in time and not continuously through time. In contrast, in a discrete-event simulation, the system is advanced when an event occurs, where an event is an action that affects the state of the system. The two simulation paradigms are also known as *time-driven* and *event-driven* simulation. Both have their advantages and disadvantages. However, the pros and cons will not be the subject of further discussion here, as they are of secondary interest.

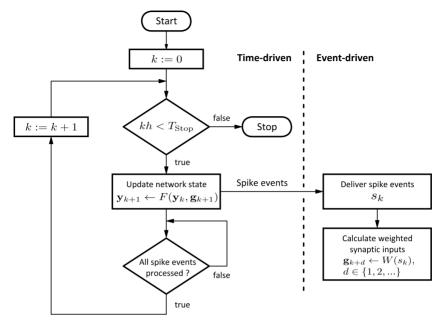

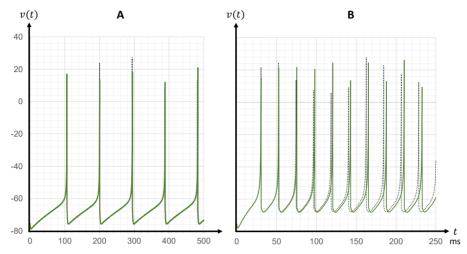

Software tools for the simulation of spiking neural networks, such as the neural simulation tool NEST (Gewaltig and Diesmann, 2007), typically use a hybrid simulation scheme. Neuron states are updated in a time-driven manner, whereas spike events are processed in an event-driven way (Morrison et al., 2005). This is a reasonable choice: the time-driven scheme allows the network state to be advanced effectively, and the event-driven scheme is appropriate because between the occurrence of two successive spike events arriving at a neuron, the weighted synaptic input to the neuron does not change – the process is inherently event-discrete. The flow diagram in Figure 1.5 illustrates this hybrid simulation scheme.

#### Notions of time

The system is evaluated in steps where the time axis is divided into intervals

$$t_k \le t \le t_{k+1}, \ t_{k+1} = t_k + h.$$

(1.14)

In Equation (1.14), h is the temporal spacing of the grid, i.e., the time resolution of the simulation. The indices k enumerate the simulation time steps. The simulated time is then given by

$$T = kh. (1.15)$$

The term *simulated time* refers to the biological time domain and is used here to avoid ambiguities with the term *simulation time*. The latter is also often used to refer to the duration of a simulation,

**Figure 1.5** | **Hybrid simulation scheme.** The network state is advanced at evenly spaced time intervals, i.e., time-driven, whereas spike events are processed as they occur, i.e., event-driven. See main text for description.

i.e., the physical time elapsed in the system.

# State update

In each simulation time step, each neuron is *visited* and its dynamic behavior is approximated on the time grid by employing numerical methods. Depending on the type of ordinary differential equations (ODEs) that describe these dynamics, Euler or Runge-Kutta-Fehlberg methods are often used here. A state transition from one grid point to the next is based on the current state  $y_k$  and incorporates the weighted synaptic inputs  $g_{k+1}$ , the summed synaptic weights of all events arriving at time step k+1:  $y_{k+1} \leftarrow F(y_k, g_{k+1})$ . At the grid points, the system is always in a well-defined state.

Spike events,  $s_k$ , are processed as they occur, calculating the synaptic inputs that will be incorporated into the dynamics at subsequent time steps:  $\mathbf{g}_{k+d} \leftarrow W(s_k)$ ,  $d \in \{1, 2, ...\}$ . To preserve the temporal causality of events, the time-driven process may need to wait until the events that occurred during a state transition are processes.

This hybrid simulation scheme has proven efficient and is also used by the neuromorphic compute node presented in Chapter 3.

#### 1.2.4 Methods and Tools

In the process of gaining insight into the underlying principles of neural computation, the methods and software tools developed and provided by the computational neuroscience community play a key role. The tools listed below are only a selection with a focus on modeling and simulation.

To conveniently describe the dynamics of neuron and synapse models, domain-specific languages (DSLs) such as NeuroML (Gleeson et al., 2010), NMODL (Hines and Carnevale, 2000), and NESTML (Plotnikov et al., 2016) have been developed. These tools allow models to be formulated in a high-level language, a DSL description, from which tools then generate simulation code.

Community software for simulation has been developed to run on all scales from laptops to the largest supercomputers. Examples are the simulation engines NEURON (Hines and Carnevale, 1997), Arbor (Akar et al., 2019), NEST (Gewaltig and Diesmann, 2007), and Brian (Goodman and Brette, 2008). For convenient graphical user interaction, tools such as NEST Desktop (Spreizer et al., 2021) are also available.

Network models are often described using a higher-level language such as PyNEST (Eppler et al., 2009) or PyNN (Davison et al., 2009). PyNN, for example, provides a common user interface for software-based neural network simulation tools (e.g., NEURON, NEST, and Brian) and also supports the neuromorphic systems SpiNNaker (Furber et al., 2013) and BrainScaleS (Schemmel et al., 2010). Here the Python programming language has established as front-end for user interaction. The language is easy to learn, has a large active community base, and offers extensive support for numerical calculations and data analytics.

This software landscape is complemented by numerical tools for statistical analysis, such as the Electrophysiology Analysis Toolkit *Elephant*<sup>2</sup> as well as tool support for model validation methodologies, for example, the validation framework *NetworkUnit*<sup>3</sup> (Gutzen et al., 2018).

The requirements with respect to efficiency, correctness and the reproducibility of results place high demands on these tools and the entire software ecosystem. This infrastructure and its requirements must be taken into account when developing new tools or designing a novel neuromorphic system if it should be of value for the computational neuroscience community.

<sup>&</sup>lt;sup>2</sup>RRID:SCR\_003833; http://neuralensemble.org/elephant

<sup>&</sup>lt;sup>3</sup>RRID:SCR\_016543; https://github.com/INM-6/NetworkUnit

# 1.3 Neuromorphic Computing as Tool for Neuroscience

The main driving force behind the developments in neuromorphic computing is undoubtedly brain-inspired computing, which seeks to apply new technologies and develop novel computer architectures inspired by the working principles of the brain – although these are not yet fully understood. The application of neuromorphic computing in computational neuroscience, however, is still a niche area, but of high interest in the field. As a tool to accelerate simulations, it can help unlock the secrets of brain function and thus contribute to the theoretical foundations of practical applications.

When studying neural networks, it is generally desirable to simulate them as fast as possible. Whereas real-time simulation is interesting because of the possibility of interacting with real-world applications, hyper-real-time would enable the study of slow processes such as learning and memory, and permit researchers to perform more comprehensive parameter scans of faster processes. However, not even the fastest and most advanced supercomputers available today can meet the challenge of significantly accelerating the simulation of a large-scale spiking neural network. The use of neuromorphic computing for this purpose, leveraging novel technologies and application-specific hardware architectures, is therefore highly attractive as it promises to provide the necessary tools for this task.

# 1.3.1 Requirements

Despite all technological innovations, making neuromorphic computing a useful tool in computational neuroscience modeling and simulation is a demanding technical challenge. Neuroscience research employs mathematical models to gain understanding of the complex dynamics of neural networks. Their simulation requires numerical accuracy. Simulations must be deterministic with reproducible outcomes. The plethora of neuron and synapse models used in simulations makes it difficult to arrive at an architecture design that satisfies all requirements equally. Plasticity rules and algorithms, which is a rapidly evolving area of research, also require a high degree of flexibility in algorithmic implementation.

Moreover, there are questions that lack a clear answer, leaving design decisions in a state of uncertainty. One such question is, for example, the required numerical precision. The answer here determines the specification of data types and the implementation of arithmetic operations and algorithms – design decisions that affect implementation complexity, chip area, and power efficiency. To the best of my knowledge, so far, only a few studies have examined the effects of numerical accuracy on simulation outcomes (e.g., Pfeil et al., 2012; Gutzen et al., 2018; Dasbach

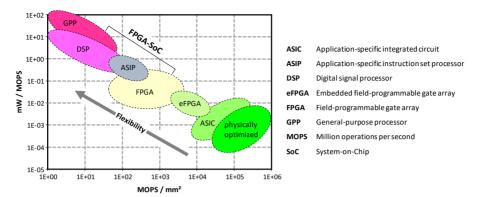

**Figure 1.6** | **Energy vs. flexibility conflict.** Invers energy efficiency and area efficiency of different implementation styles (scaled to a 130 nm CMOS technology) redrawn after Noll et al. (2010) and modified. The alternatives span more than five orders of magnitude in both energy and area efficiency. Flexibility increases toward general-purpose solutions as efficiency decreases. From an application perspective, FPGA-SoC technology can bridge the flexibility-gap between programmable logic devices and general-purpose processors.

## et al., 2021; Trensch et al., 2018, and Chapter 2).

A neuromorphic architecture must therefore provide flexibility in model implementation. It should not be bound to a specific model and should be open to extensions. To achieve high user acceptance, it must integrate with the existing landscape of tools and workflows for modeling and simulation. Scalability and the capability of delivering significant acceleration are of course also key requirements.

Flexibility and efficiency are both essential, yet they are technically conflicting requirements that constrain the design space and influence the choice of technology and implementation style. The requirement for numerical accuracy and reproducibility here rules out approaches based on analog circuits.

# 1.3.2 Choice of Technology

Flexibility and efficiency are opposing goals in the choice of technology, resulting from the so called *energy vs. flexibility conflict* (Noll et al., 2010). This conflict is illustrated in Figure 1.6, which shows a quantitative comparison of different circuit implementation styles.

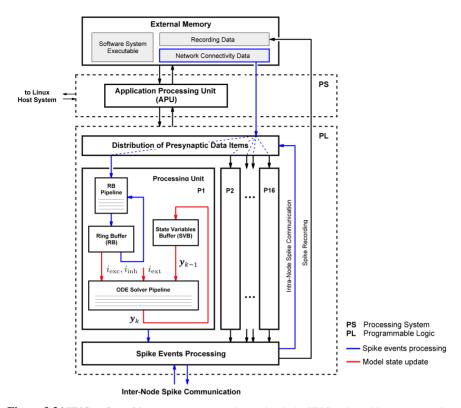

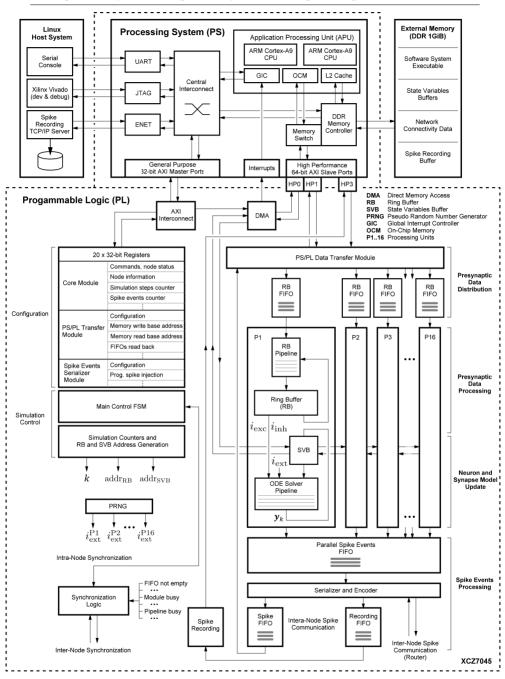

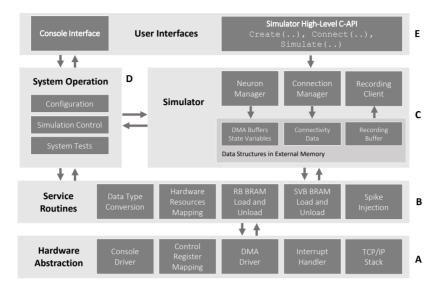

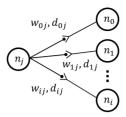

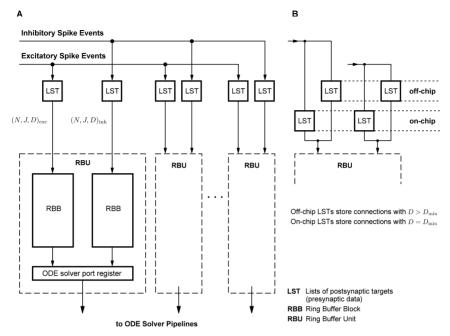

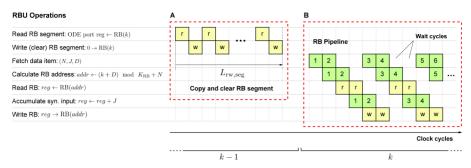

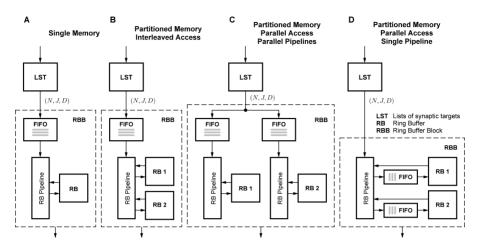

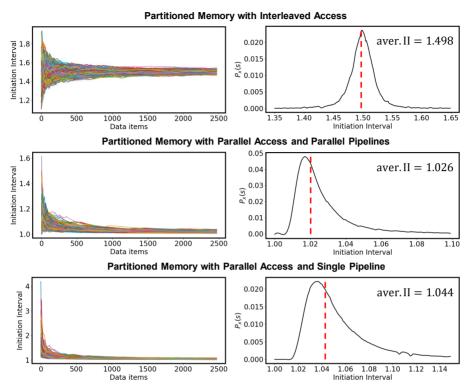

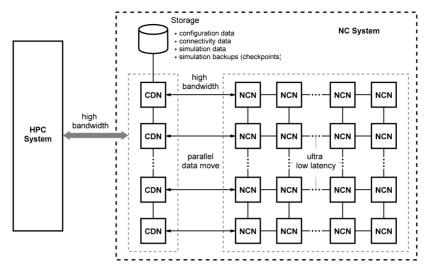

While traditional programmable general-purpose processors (GPPs) provide the highest level of flexibility, a physically optimized application-specific integrated circuit (ASIC) *freezes* a specific use case in silicon. Physically optimized ASICs achieve the highest efficiency, but are inflexible.