# Software-Configurable Analog-To-Digital Converters for Configurable Pulse Detection

Lukas Krystofiak

Information

Band / Volume 112

ISBN 978-3-95806-826-1

Forschungszentrum Jülich GmbH Peter Grünberg Institut (PGI) Integrated Computing Architectures (PGI-4)

# Software-Configurable Analog-To-Digital Converters for Configurable Pulse Detection

Lukas Krystofiak

Schriften des Forschungszentrums Jülich Reihe Information / Information

Bibliografische Information der Deutschen Nationalbibliothek. Die Deutsche Nationalbibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliografie; detaillierte Bibliografische Daten sind im Internet über http://dnb.d-nb.de abrufbar.

Herausgeber Forschungszentrum Jülich GmbH

und Vertrieb: Zentralbibliothek, Verlag

52425 Jülich

Tel.: +49 2461 61-5368 Fax: +49 2461 61-6103 zb-publikation@fz-juelich.de

www.fz-juelich.de/zb

Umschlaggestaltung: Grafische Medien, Forschungszentrum Jülich GmbH

Druck: Grafische Medien, Forschungszentrum Jülich GmbH

Copyright: Forschungszentrum Jülich 2025

Schriften des Forschungszentrums Jülich Reihe Information / Information, Band / Volume 112

D 464 (Diss. Duisburg-Essen, Univ., 2024)

ISSN 1866-1777 ISBN 978-3-95806-826-1

Vollständig frei verfügbar über das Publikationsportal des Forschungszentrums Jülich (JuSER) unter www.fz-juelich.de/zb/openaccess.

This is an Open Access publication distributed under the terms of the <u>Creative Commons Attribution License 4.0</u>, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

# Acknowledgement

First and foremost, I would like to start by thanking my doctoral advisor Prof. Dr.-Ing. Stefan van Waasen for giving me the opportunity to work on this truly interesting and innovative project. I am grateful for your guidance and help during the work on this thesis.

Special thanks goes to my scientific supervisors Christian Grewing and André Zambanini for offering a lot of their time and help with the thesis as well as the project. Your guidance and supervision has been invaluable throughout my work.

My deepest gratitude goes towards the whole IC design team. Thank you for helping me developing the chips for my thesis and always taking the time as well as having the patience to answer all my questions. In particular I would like to thank Volker Christ who helped me a lot during the design and also the verification in simulation of the chip.

I would also like express my appreciation to Christian Roth, Markus Harff and Daniel Liebau for all the help and advice offered in measurement, verification in the laboratory and testing of the chips.

I am thankful to my colleagues, at the Central Institute of Engineering, Electronics and Analytics - Electronic Systems (ZEA-2) who I have worked with, for their kindness and company. This is extended especially to all the PhD students. Your friendship and support showed me new perspectives to problems and helped me through hard times during the thesis. I will never forget the memories we created throughout my time at the institute.

Finally, I would like to thank my family and Eva. Your belief in me and moral support is invaluable to me. This work would have not been possible without your help.

## **Abstract**

With ever increasing digital processing capabilities, the analog-to-digital converter moves more and more in the focus of analog integrated circuit design becoming one of the most important building blocks. The progression to modern process technology nodes offers great potential, but comes in general along with an exponential growth in time effort for design, layout and verification. The overall cost for projects exceeds the capacities in research traditionally coping with smaller budgets than industry. Future developments therefore have to be accomplished in joint efforts, distributing different circuit blocks among research groups. But this also implicates that future electronics become more generic covering multiple areas of application.

In this thesis, the concept of a software-configurable analog-to-digital converter is proposed. Its matrix-like structure consisting of many sub analog-to-digital converters is able to adjust the resolution and sample rate, but ultimately the power consumption, to fit a wide range of applications in research. A first version of a software-configurable analog-to-digital converter can be switched from a high-precision mode with 11 bit resolution to a low-power mode with 8 bit. It is the focus of this work and is manufactured in a silicon 28 nm bulk CMOS process technology node. Its high integration factor allows the implementation of powerful digital signal processing on-chip, while analog performance and conventional design methodologies largely stay valid as it is still a planar bulk silicon process.

In a first step, a chip was designed and manufactured featuring a 6 bit successive approximation register analog-to-digital converter. It served as a pilot project marking the transition from a previously used 65 nm technology process to a more modern 28 nm node at the institute. The main focus here was to identify the potential and also the drawbacks of the technology as well as to gather experience in the design of successive approximation register analog-to-digital converters. The results of literature research, design decisions, consequences and finally the measurement results are presented in detail.

Subsequently, a second chip has a first version of a software-configurable analog-to-digital converter at its core. For the two sub analog-to-digital converters it is mainly based on, the experience from the first chip helped to accelerate the design and enabled significant improvements. Apart from that, further improvements were integrated on an architectural level to increase power efficiency and increase the competitiveness of a generic solution. Simulation and measurement results are presented in detail. Finally, an error analysis is given investigating the non optimal behavior of the high-precision mode.

# Zusammenfassung

Der stetige Anstieg der Leistungsfähigkeit digitaler Signalverarbeitung rückt Analog-Digital-Wandler mehr und mehr in den Fokus der Entwicklung integrierter Schaltungskreise. Der Fortschritt beim Wechsel zu modernen Prozesstechnologien zeigt einerseits starkes Potenzial, allerdings erhöht sich auch der Design-, Layout- und Verifikationsaufwand exponentiell. Die Gesamtkosten von Projekten übersteigen so die Möglichkeiten in der Forschung, welche traditionell mit kleineren Budgets auskommen muss als die Industrie. Entwicklungen müssen daher in Zukunft gemeinsam erarbeitet werden und einzelne Schaltblöcke auf unterschiedliche Forschungsgruppen aufgeteilt werden. Dies hat allerdings auch zur Folge, dass Schaltungen allgemeiner gebaut werden müssen, um verschiedene Anwendungsgebiete abzudecken.

In dieser Arbeit wird das Konzept eines softwareseitig einstellbaren Analog-Digital-Wandlers vorgestellt. Dieser ist aus mehreren kleineren und simplen Analog-Digital-Wandlern aufgebaut, die in einer Art Matrixstruktur zusammengefasst werden. Durch Abschalten einzelner Bereiche ist es möglich unterschiedliche Auflösungen und Abtastraten zu realisieren, wodurch letztendlich die Leistungsaufnahme skaliert werden kann. Zur genaueren Untersuchung wurde eine erste Version eines softwareseitig einstellbaren Analog-Digital-Wandlers entwickelt. Dieser hat einen Modus mit hoher Auflösung von 11 bit sowie einen Modus mit verringerter Leistungsaufnahme und 8 bit Auflösung. Als Prozessknoten wird eine 28 nm bulk CMOS Technologie eingesetzt. Mit einer hohen Integrationsdichte können komplexe Signalverarbeitungsblöcke realisiert werden, gleichzeitig erlaubt die Ähnlichkeit zu früheren Knoten den Einsatz von bekannten Designmethoden.

In einem ersten Schritt wurde ein Chip mit einem 6 Bit Analog-Digital-Wandler entwickelt und gefertigt, der nach dem Prinzip der sukzessiven Approximation arbeitet. Dieses Pilotprojekt markiert dabei den Wechsel von einer 65 nm-Technologie zu einer 28 nm-Technologie am Institut. Hauptziel war die Untersuchung von Vor- und Nachteilen der neuen Prozesstechnologie und allgemeiner Erfahrungsgewinn beim Entwickeln von Analog-Digital-Wandlern, die nach dem Prinzip der sukzessiven Approximation arbeiten. Die Resultate der Literaturrecherche, der Simulationen und der Verifikationsmessungen im Labor werden detailliert wiedergegeben.

Ein zweiter Chip mit einer ersten Version eines softwareseitig einstellbaren Analog-Digital-Wandlers wurde darauf basierend entwickelt. Für die kleineren und simplen Analog-Digital-Wandler konnte dabei stark auf die Erfahrungen des ersten Chips zurückgegriffen werden. Darüber hinaus wurden weitere Verbesserungen auf Architekturebene eingefügt, um die Nachteile einer generischen Lösung zu verringern. Simulationen und Messungen werden wieder detailliert beschrieben. Weiterhin wird auch eine Analyse vorgestellt, die das nicht optimale Verhalten im Hochpräzisionsmodus untersucht.

# **Contents**

| Ac  | Acknowledgement i |         |                                         |      |  |

|-----|-------------------|---------|-----------------------------------------|------|--|

| Lis | st of             | Figures |                                         | хi   |  |

| Lis | st of             | Tables  |                                         | xv   |  |

| Ac  | rony              | ms      |                                         | xvii |  |

| 1   | Intr              | oductio | on                                      | 1    |  |

|     | 1.1               | Motiv   | ation                                   | . 1  |  |

|     | 1.2               | Outlin  | ne of the Thesis                        | . 2  |  |

| 2   | Fun               | damen   | tals of the Analog-To-Digital Converter | 5    |  |

|     | 2.1               | Princi  | ple Theory of Operation                 | . 5  |  |

|     | 2.2               | Funda   | mental Limits                           | . 6  |  |

|     |                   | 2.2.1   | Quantization Noise                      | . 6  |  |

|     |                   | 2.2.2   | kTC Noise                               | . 7  |  |

|     |                   | 2.2.3   | Jitter                                  | . 8  |  |

|     | 2.3               | Funda   | mental Characterization Units           | . 9  |  |

|     |                   | 2.3.1   | Signal-to-Noise Ratio                   | . 9  |  |

|     |                   | 2.3.2   | Total Harmonic Distortion               |      |  |

|     |                   | 2.3.3   | Signal-to-Noise-and-Distortion Ratio    |      |  |

|     |                   | 2.3.4   | Dynamic Range                           |      |  |

|     |                   | 2.3.5   | Spurious-Free Dynamic Range             |      |  |

|     |                   | 2.3.6   | Differential Nonlinearity               |      |  |

|     |                   | 2.3.7   | Integral Nonlinearity                   |      |  |

|     |                   | 2.3.8   | Figure of Merit                         |      |  |

|     | 2.4               |         | Types                                   |      |  |

|     |                   | 2.4.1   | Flash ADC                               |      |  |

|     |                   | 2.4.2   | SAR ADC                                 |      |  |

|     |                   | 2.4.3   | Slope ADC                               |      |  |

|     |                   | 2.4.4   | Sigma-Delta ADC                         |      |  |

|     |                   | 2.4.5   | Pipelined ADC                           |      |  |

|     |                   | 2.4.6   | Time-Interleaved ADC                    |      |  |

|     | 2.5               |         | of the Art                              |      |  |

|     | 2.3               | State   | in the Art                              | . 24 |  |

| 3   | Con               | cept fo | or a Software-Configurable ADC          | 31   |  |

|     | 3.1               |         | 1                                       |      |  |

|     | 3.2               | First I | teration of a Software-Configurable ADC | . 32 |  |

|     | 3.3               | Proces  | ss Technology Choice                    | . 34 |  |

| 4 | First | ADC Chip 35                              |

|---|-------|------------------------------------------|

|   | 4.1   | Overview SAR ADC                         |

|   | 4.2   | Technical Specifications                 |

|   | 4.3   | Asynchronous Operation                   |

|   | 4.4   | Capacitive Digital-To-Analog Converter   |

|   |       | 4.4.1 CDAC Switching Scheme              |

|   |       | 4.4.2 Implementation                     |

|   | 4.5   | Comparator                               |

|   |       | 4.5.1 The Dynamic Latch-Based Comparator |

|   |       | 4.5.2 Implementation                     |

|   | 4.6   | Sequencer                                |

|   |       | 4.6.1 The classical Sequencer            |

|   |       | 4.6.2 Implementation                     |

|   | 4.7   | Input Buffer                             |

|   |       | 4.7.1 Specifications                     |

|   |       | 4.7.2 Implementation                     |

|   | 4.8   | Bootstrapped Switches                    |

|   |       | 4.8.1 Fundamentals                       |

|   |       | 4.8.2 Implementation                     |

|   | 4.9   | Delay Element                            |

|   |       | 4.9.1 Introduction                       |

|   |       | 4.9.2 Implementation                     |

|   | 4.10  | Metastability detector                   |

|   |       | Reference Buffer                         |

|   |       | Layout                                   |

| 5 | Mea   | surement Results of First ADC Chip 63    |

|   | 5.1   | Printed Circuit Board                    |

|   | 5.2   | Measurement Setup                        |

|   | 5.3   | Delay Line Configuration                 |

|   | 5.4   | Maximum Sample Rate                      |

|   | 5.5   | Power Consumption                        |

|   | 5.6   | Maximum Input Signal Frequency           |

|   | 5.7   | DNL and INL                              |

|   | 5.8   | Performance Summary                      |

|   | 5.9   | Discussion of the First Chip ADC         |

| 6 | Seco  | and ADC Chip 71                          |

|   |       | Technical Specifications                 |

|   | 6.2   | Overview Pipelined SAR ADC               |

|   |       | 6.2.1 First Stage Bypass                 |

|   |       | 6.2.2 Residue Interleaving               |

|   |       | 6.2.3 Self-Adjusted Duty Cycle           |

|   |       | 6.2.4 1.8 Volt Switches                  |

|   | 6.3   | Input buffer                             |

|   | 6.4   | Metastability                            |

|   | 6.5   | Sequencer                                |

|   |       | =                                        |

| Bi | bliog      | raphy          |                                     | xix      |

|----|------------|----------------|-------------------------------------|----------|

| 8  | Con        | clusion        | and Outlook                         | 111      |

|    |            | 7.5.2          | High-Precision Mode                 | 110      |

|    |            | 7.5.1          | Low-Power Mode                      |          |

|    | 7.5        | Discus         | sion of Second Chip ADC             |          |

|    |            | 7.4.7          | Performance Summary                 | 108      |

|    |            | 7.4.6          | DNL and INL                         | 107      |

|    |            | 7.4.5          | SNDR and SFDR                       | 106      |

|    |            | 7.4.4          | Power Consumption                   | 105      |

|    |            | 7.4.3          | Impact of Input Common-Mode Voltage | 103      |

|    |            | 7.4.2          | First Stage ADC Investigation       | 102      |

|    | 7.1        | 7.4.1          | Erroneous Output Characteristic     | 102      |

|    | 7.4        |                | Precision Mode Measurements         | 100      |

|    |            | 7.3.5<br>7.3.6 | Performance Summary                 | 100      |

|    |            | 7.3.4<br>7.3.5 | Maximum Input Signal Frequency      | 98<br>99 |

|    |            | 7.3.3          | Power Consumption                   | 97<br>98 |

|    |            | 7.3.2          | Maximum Sample Rate                 | 96       |

|    |            | 7.3.1          | Delay Line Configuration            | 96       |

|    | 7.3        |                | ower Mode Measurements              | 96       |

|    | 7.2        |                | rement Setup                        | 95       |

|    | 7.1        |                | l Circuit Board                     | 95       |

| 7  | Mea        |                | ent Results of Second ADC Chip      | 95       |

|    |            | •              |                                     |          |

|    |            |                | Overview                            | 93       |

|    | 6.10       |                | I Stage Comparator                  | 92       |

|    | 6.9        |                | I Stage CDAC                        | 90       |

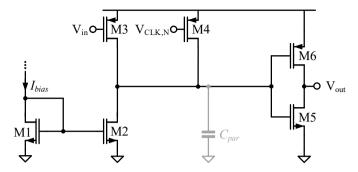

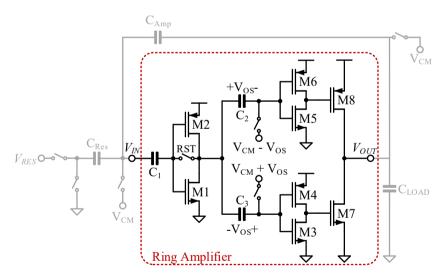

|    |            | 6.8.2          | The Ring Amplifier                  | 88       |

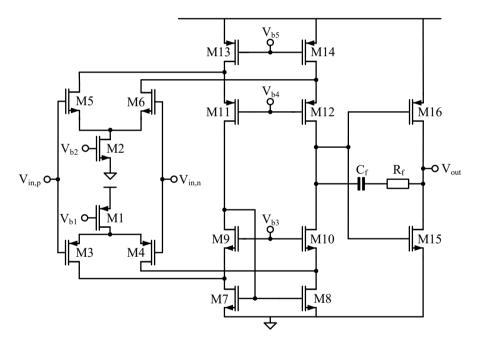

|    | 0.8        | 6.8.1          | e Amplifier                         | 86       |

|    | 6.7<br>6.8 | •              | Element                             | 86       |

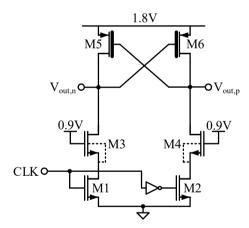

|    |            | 6.6.2          | Comparator                          | 84<br>85 |

|    |            | 6.6.1          | CDAC                                | 81       |

|    | 6.6        |                | tage SAR ADC                        | 81       |

# **List of Figures**

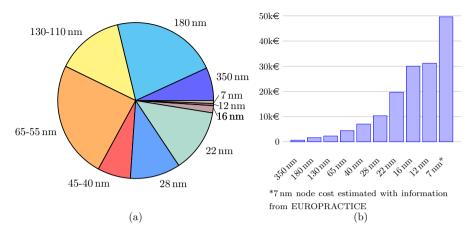

| 1.1        | (a) Share of the individual process node on the overall manufactured chips. (b) Manufacturing cost for process nodes in a multi-project wafer run [1]         | 2  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

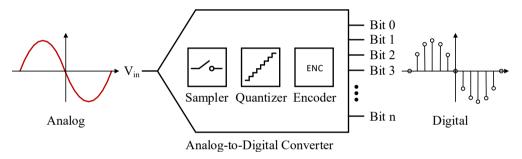

| 2.1<br>2.2 | Fundamental elements of an ADC                                                                                                                                | 5  |

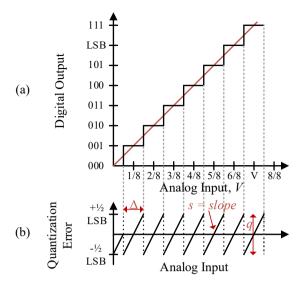

|            | (b) Resulting quantization error for the individual quantization intervals                                                                                    | 7  |

| 2.3        | Equivalent noise circuit of a classical sampler in an ADC                                                                                                     | 7  |

| 2.4        | Maximum reachable SNR for different values of jitter plotted over the input                                                                                   |    |

|            | signal frequency                                                                                                                                              | 11 |

| 2.5        | SNR caused by kTC noise plotted over the sampling capacitance of an ADC and a signal amplitude $V_0$ of 0.5 V. The stair plot shows the resolution in integer |    |

|            | ENOB steps as was done in [9]                                                                                                                                 | 13 |

| 2.6        | Spectrum of a signal highlighting the fundamental and harmonics                                                                                               | 14 |

| 2.7        | (a) A DC output characteristic of an ADC showing different DNL errors. (b)                                                                                    |    |

|            | A DC output characteristic of an ADC showing the INL error of the output in                                                                                   |    |

|            | blue compared to the ideal transfer curve shown here in red                                                                                                   | 16 |

| 2.8        | (a) Exemplary DNL of a 8 bit ADC. (b) Exemplary INL of a 8 bit ADC                                                                                            | 17 |

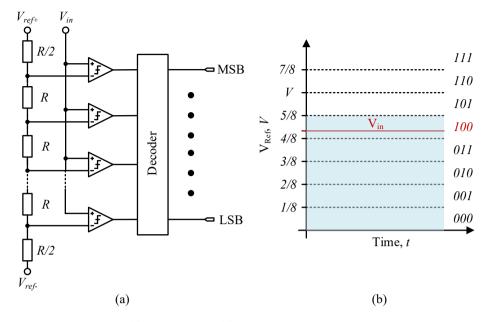

| 2.9        | (a) Structure and (b) conversion principle for a flash ADC                                                                                                    | 19 |

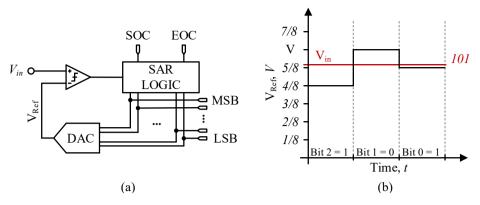

| 2.10       | (a) Structure and (b) conversion principle for a SAR ADC                                                                                                      | 20 |

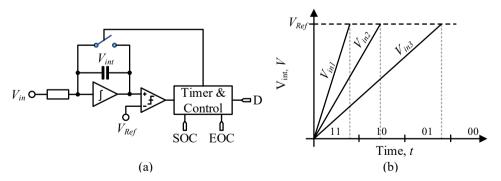

| 2.11       | (a) Structure and (b) conversion principle for a slope ADC                                                                                                    | 20 |

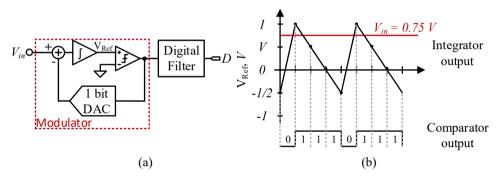

| 2.12       | (a) Structure and (b) conversion principle of a sigma delta ADC                                                                                               | 21 |

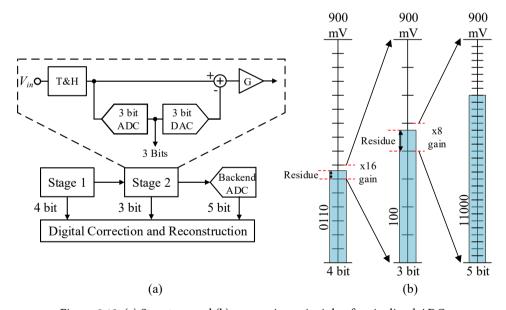

| 2.13       | (a) Structure and (b) conversion principle of a pipelined ADC                                                                                                 | 22 |

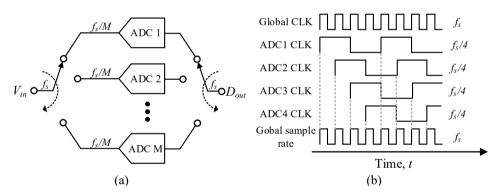

| 2.14       | (a) Structure and (b) conversion principle of a time-interleaved ADC. The                                                                                     |    |

|            | example assumes a four times time-interleaved ADC                                                                                                             | 23 |

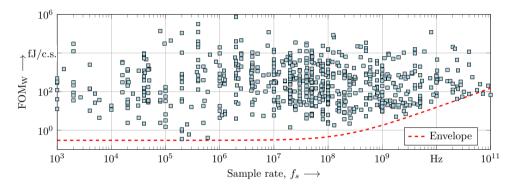

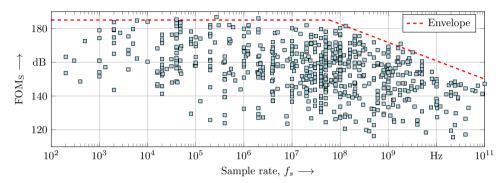

| 2.15       | FoM <sub>W</sub> plotted over sample rate for ADCs published in ISSCC and VLSI circuit                                                                        |    |

|            | symposium from 1997 to 2023, and performance envelope [43]                                                                                                    | 24 |

| 2.16       | FoM <sub>S</sub> plotted over sample rate for ADCs published in ISSCC and VLSI circuit                                                                        |    |

|            | symposium from 1997 to 2023, and performance envelope [43]                                                                                                    | 25 |

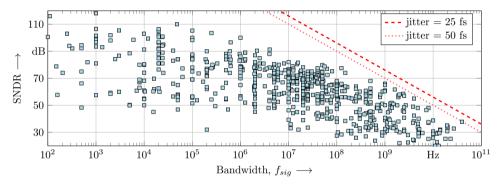

| 2.17       | SNDR plotted over sample rate for ADCs published in ISSCC and VLSI circuit                                                                                    |    |

|            | symposium from 1997 to 2023, and jitter noise limitations on SNDR for a jitter                                                                                | ۰. |

| 0.10       | of 25 fs and 50 fs [43]                                                                                                                                       | 26 |

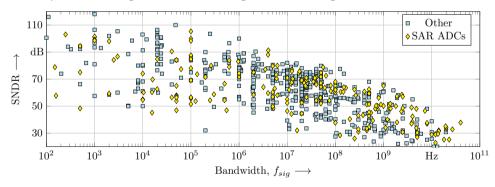

| 2.18       | SNDR plotted over sample rate for ADCs published in ISSCC and VLSI circuit                                                                                    |    |

|            | symposium from 1997 to 2023 with SAR ADCs highlighted which make up                                                                                           | 27 |

|            | 31.2 % of the total publications [43]                                                                                                                         | 27 |

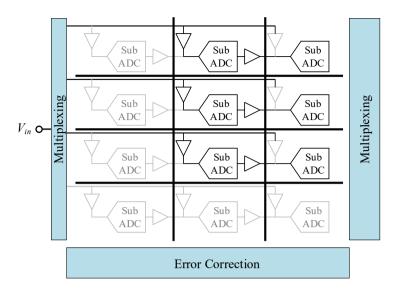

| 3.1        | Concept of a software-configurable ADC with concatenated sub ADCs for                                                                                         |    |

|            | increasable resolution and parallel sub ADCs for increasable sample rate                                                                                      | 32 |

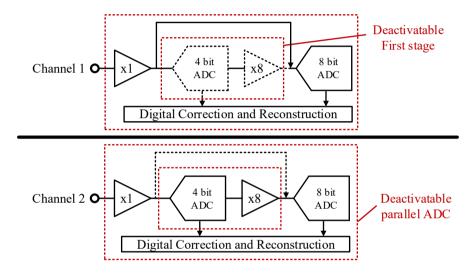

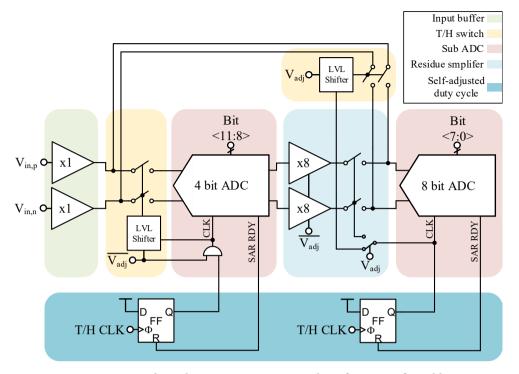

| 3.2        | Schematic of the first implemented version of a software-configurable ADC                                                                                     | 33 |

| 4 1        | An accompliant about the main blocks accomplished in a CAR ARC                                                                                                | 27 |

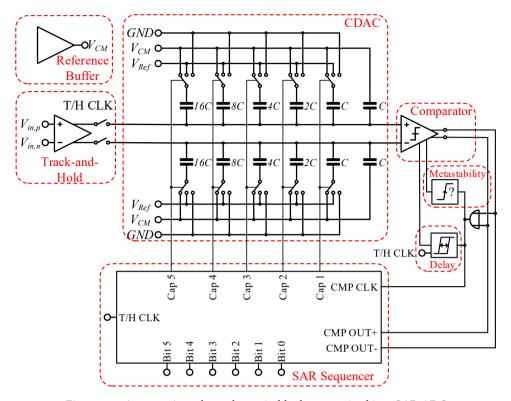

| 4.1        | An overview about the main blocks comprised in a SAR ADC                                                                                                      | 36 |

| 4.2        | , , ,                                                                                                                                                         | 38 |

|            | SAR ADC.                                                                                                                                                      | 30 |

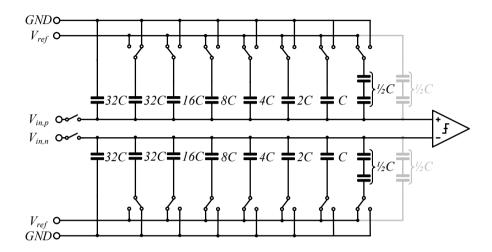

| 4.3  | Principle theory for the capacitive DACs                                            | 39         |

|------|-------------------------------------------------------------------------------------|------------|

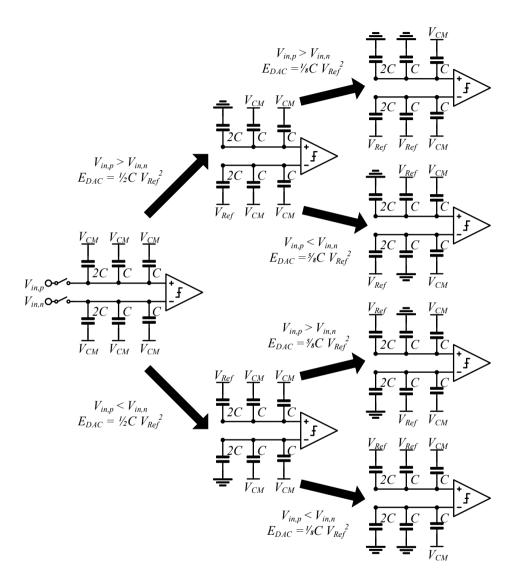

| 4.4  | Principle of the switching scheme for a $V_{CM}$ -based CDAC                        | 41         |

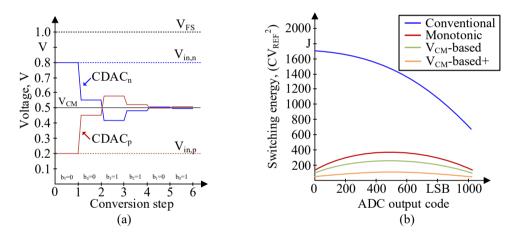

| 4.5  | (a) Progression of the voltage on the top side of the CDAC and the negative side    |            |

|      | of the CDAC for the $V_{CM}$ -based switching scheme for a 6 bit ADC. (b) Switching |            |

|      | energy for different switching schemes plotted for every output code of a 10        |            |

|      | bit ADC.                                                                            | 42         |

| 4.6  | Modified $V_{CM}$ -based switching scheme implemented in the SAR ADC in this        |            |

|      | thesis. The grayed out capacitors are omitted in design and layout as parasitic     |            |

|      | elements have a larger effect                                                       | 45         |

| 4.7  | Illustration of the common-centroid distribution of the capacitors in the CDAC      |            |

|      | and additional dummy elements to create even manufacturing conditions for           |            |

|      | all unit capacitors                                                                 | 47         |

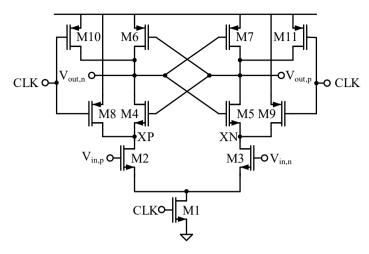

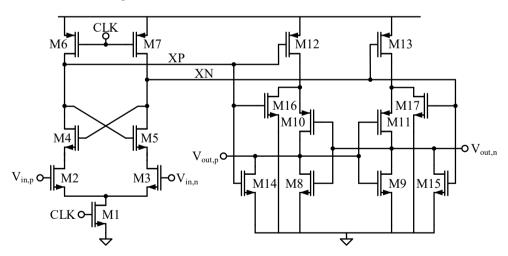

| 4.8  | Schematic of a strong-arm, dynamic latch-based comparator [68] [69]                 | 48         |

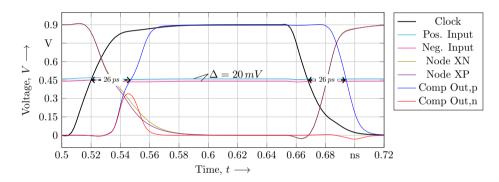

| 4.9  | Schematic of the double-tail latched comparator implemented in the SAR ADC          |            |

| ,    | of this thesis.                                                                     | 49         |

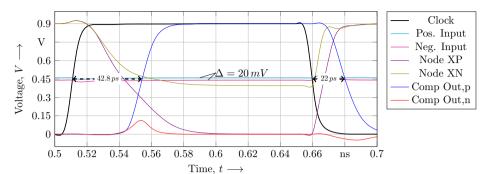

| 4.10 | Simulated output characteristic of the comparator for a differential input voltage  |            |

| 1.10 | of 10 mV and common-mode voltage of 450 mV.                                         | 49         |

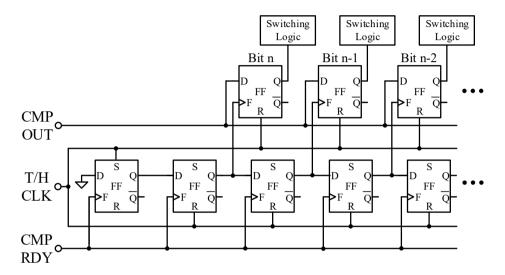

| 4 11 | Classical sequencer built mainly out of DFFs [73]                                   | 50         |

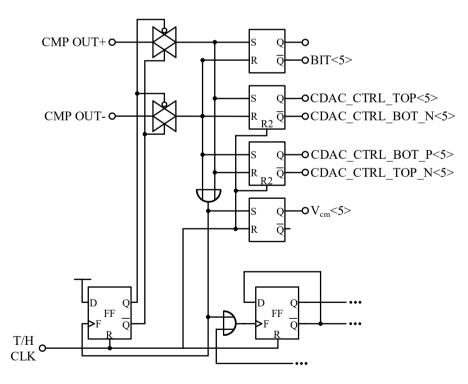

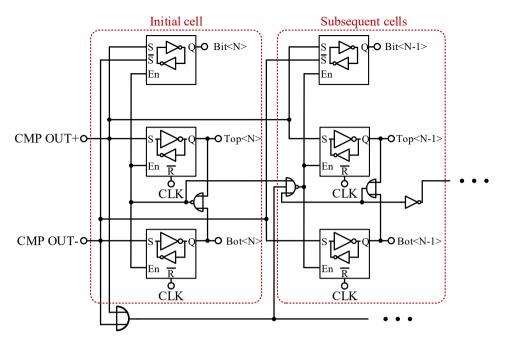

|      | One cell of the implemented sequencer responsible for one conversion step           | 30         |

| 7.12 | plus one start DFF on the bottom left in the figure                                 | 51         |

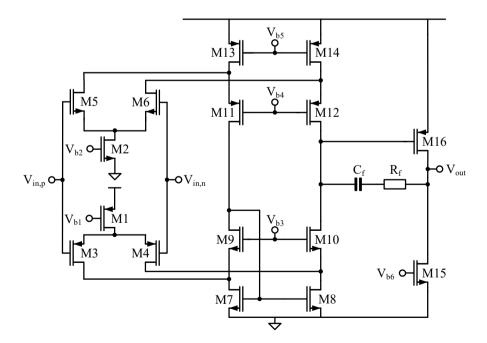

| 4 13 | Schematic of the implemented input buffer for the implemented SAR ADC               | 53         |

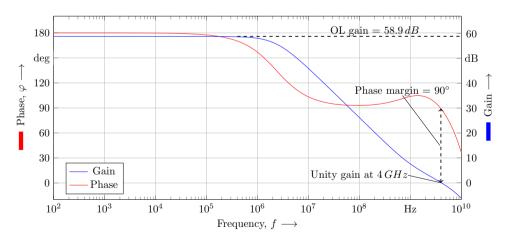

|      | Gain and phase margin of the input buffer for the implemented SAR ADC               | 54         |

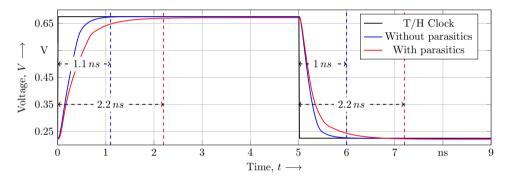

|      | Step response of the input buffer for the implemented SAR ADC                       | 55         |

| 4.16 |                                                                                     | J          |

| 4.10 | ADC. Highlighted is the bootstrapped switch passing the input signal from the       |            |

|      | input buffer to the CDAC                                                            | 57         |

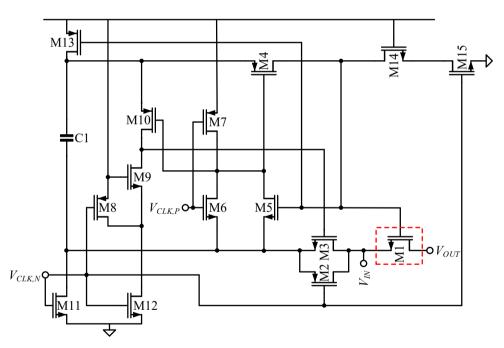

| 4.17 |                                                                                     | 58         |

|      | An adjustable current mirror used to control the current available in the current   | 30         |

| 4.18 | starved inverters of the delay element.                                             | 59         |

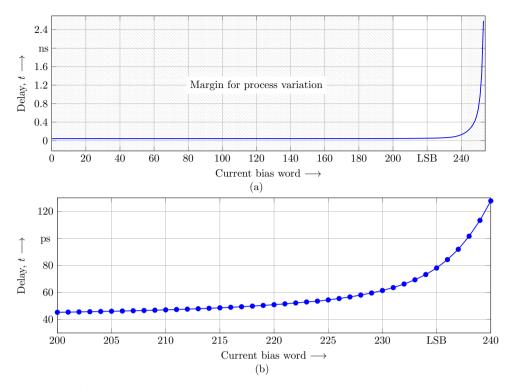

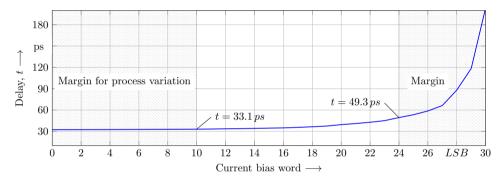

| 4.19 | (a) Propagation time of the delay element plotted over bias current for the full    | J;         |

| 4.19 | configuration range. (b) A zoomed-in range showing the needed delay                 | 60         |

| 4.20 |                                                                                     | OC         |

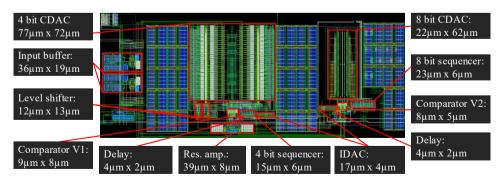

| 4.20 | Layout screenshot of the implemented SAR ADC with its individual components         | <i>(</i> 1 |

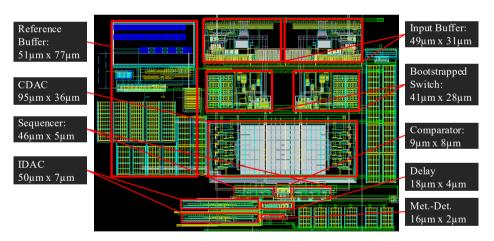

|      | highlighted                                                                         | 61         |

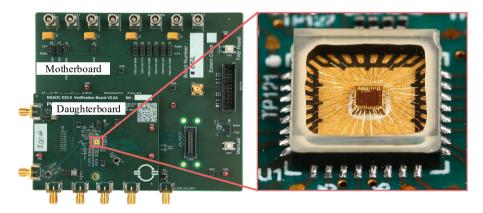

| 5.1  | Illustration of the PCBs split into motherboard and daughterboard for the chip      |            |

|      | with the SAR ADC on the left. Close up of the packaged chip with the lid            |            |

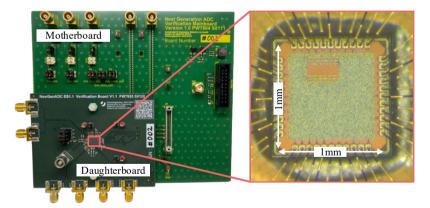

|      | removed on the right                                                                | 63         |

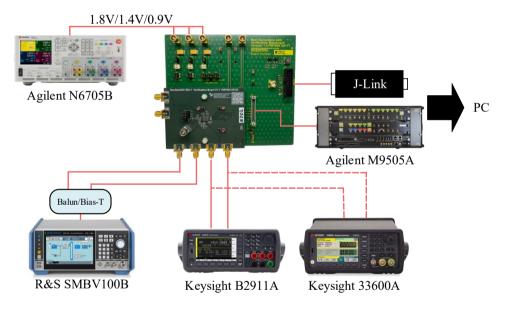

| 5.2  | Measurement setup for the implemented SAR ADC                                       | 64         |

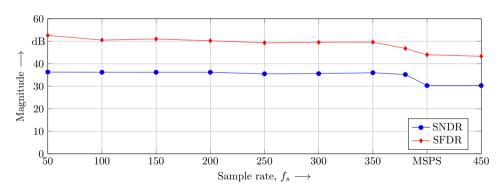

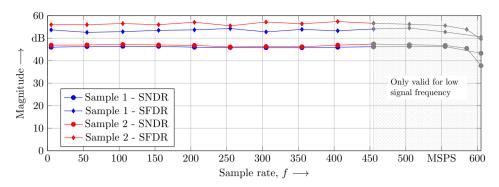

| 5.3  | Measured SNDR and SFDR plotted over the sample rate of the implemented              |            |

|      | SAR ADC.                                                                            | 65         |

| 5.4  | Measured power consumption plotted over the sample rate of the implemented          |            |

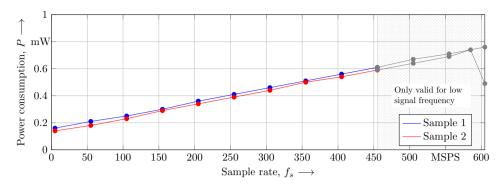

|      | SAR ADC.                                                                            | 66         |

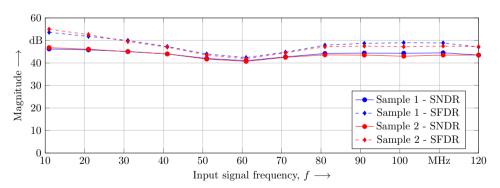

| 5.5  | Measured SNDR and SFDR plotted over the input signal frequency of the               |            |

|      | implemented SAR ADC                                                                 | 67         |

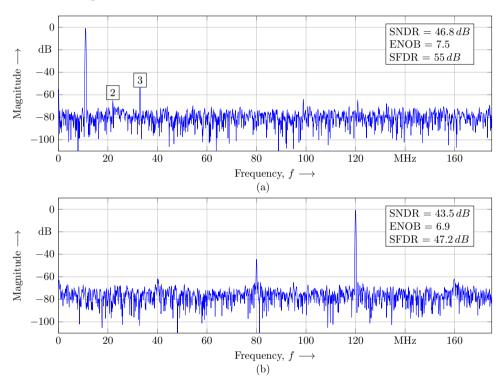

| 5.6  | Measured spectrum of the implemented ADC at a sample rate of 350 MSPS. (a)          | ٠,         |

|      | Spectrum for a low frequency input signal of 10.99 MHz. (b) Spectrum for a          |            |

|      | high frequency input signal of 119.99 MHz.                                          | 67         |

|      | mon mediane, interesting or 11/1// 1/11/20.                                         | 57         |

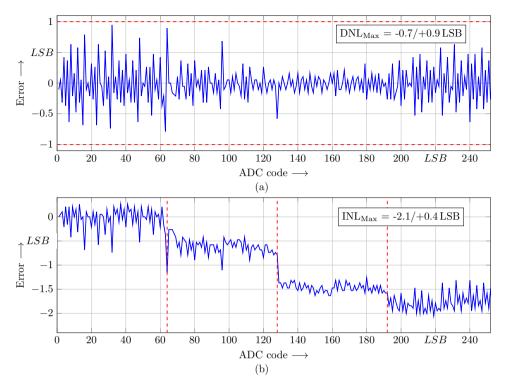

| 5.7         | (a) Measured DNL and (b) measured INL of the implemented SAR ADC                                                                                                | 68       |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 6.1         | Overview about the main components in the software-configurable ADC (a) Conversion timing of a conventional pipelined ADC. (b) Conversion timing                | 72       |

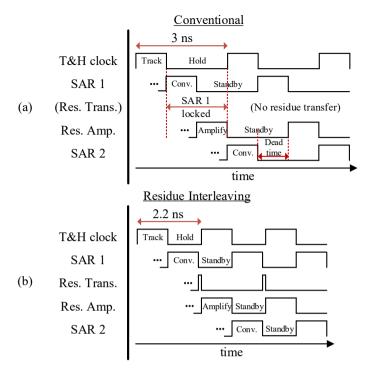

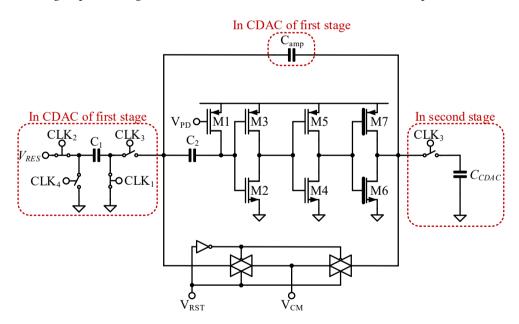

| 6.2         |                                                                                                                                                                 | 7/       |

| 6 2         | of a pipelined ADC with the proposed residue interleaving                                                                                                       | 74<br>75 |

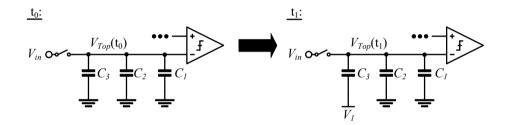

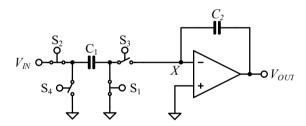

| 6.3<br>6.4  | Implementation of residue interleaving in the CDAC of a SAR ADC Principle of accurate amplification in a charge-based amplifier with bottom-                    | /:       |

|             | plate sampling                                                                                                                                                  | 75       |

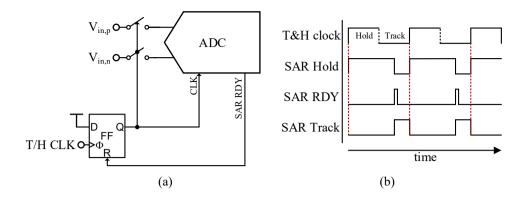

| 6.5         | (a) Basic implementation method for a SAR ADC with a self-adjusted duty cyle.                                                                                   |          |

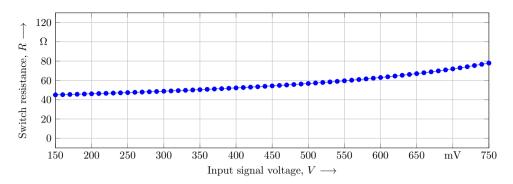

| 6.6         | (b) Diagram of the internal signals for a SAR ADC with a self-adjusted duty cyle. Diagram of the resistance change over voltage for a 1.8 V switch used as sam- | 76       |

| 6.7         | pling switch for the given input signal amplitude                                                                                                               | 77       |

| 0.7         | to the 1.8 V domain.                                                                                                                                            | 77       |

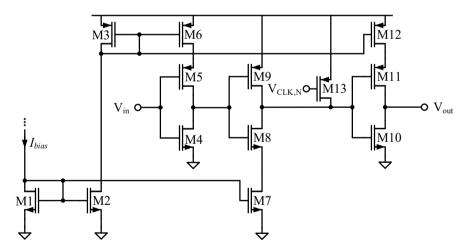

| 6.8         | Schematic of the input buffer used in the software-configurable ADC                                                                                             | 78       |

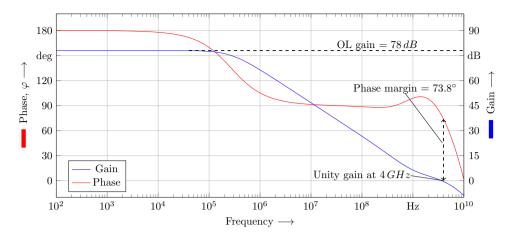

| 6.9         | Gain and phase margin of the implemented input buffer for the software-                                                                                         |          |

|             | configurable ADC.                                                                                                                                               | 79       |

| 6.10        | Step response of the input buffer used in the software-configurable ADC for a                                                                                   | 70       |

| <i>(</i> 11 | maximum voltage step size                                                                                                                                       | 79       |

| 6.11        | General structure of the sequencer used in both sub ADCs of the pipelined ADC.                                                                                  | 81       |

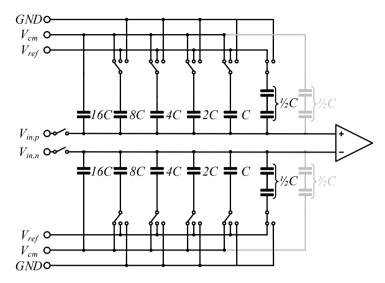

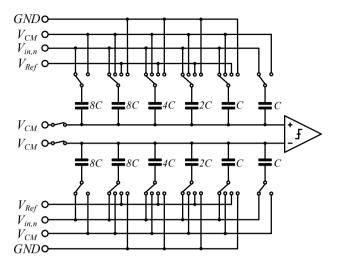

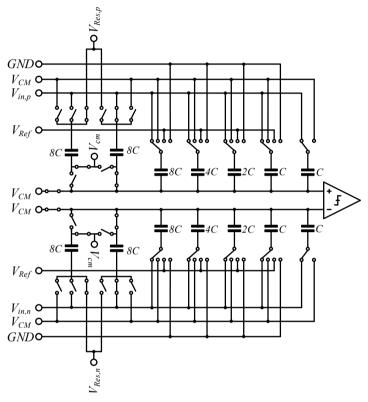

| 6.12        | Schematic of a CDAC utilizing a $V_{CM}$ -based switching scheme with bottom-plate switching.                                                                   | 82       |

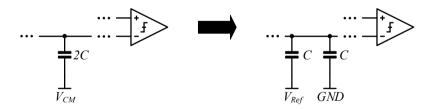

| 6.13        | Principle of splitting a single capacitor driven by a common-mode voltage $V_{CM}$                                                                              |          |

|             | into two individual capacitors driven by $V_{Ref}$ and $GND$ for an equivalent behavior.                                                                        | 82       |

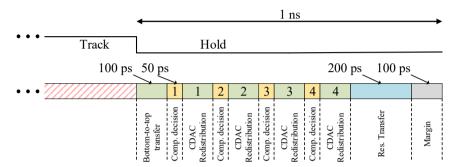

| 6.14        | Final schematic of the first stage ADC CDAC combining the bottom-plate $V_{CM}$ -based switching scheme with the residue interleaving through the attenuation   |          |

|             | capacitors. Not shown is the capacitor splitting for better overview                                                                                            | 83       |

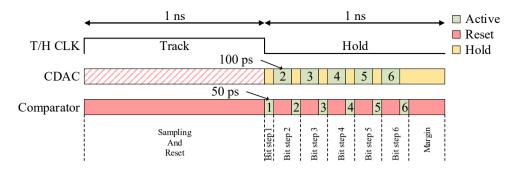

| 6.15        | Timing for the first stage SAR ADC                                                                                                                              | 84       |

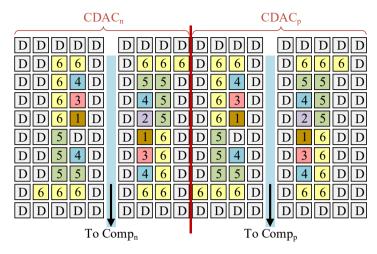

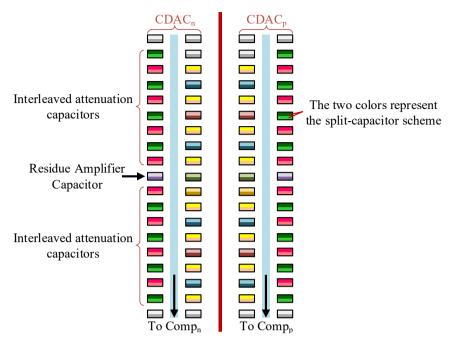

|             | Illustration of the interdigitated capacitor distribution in the CDAC of the first                                                                              |          |

|             | stage SAR ADC                                                                                                                                                   | 85       |

| 6.17        | Basic schematic of the delay implemented in the SAR ADC stages of the                                                                                           |          |

|             | pipelined ADC.                                                                                                                                                  | 86       |

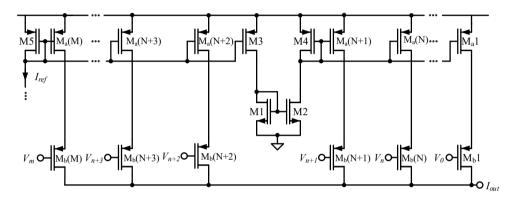

| 6.18        | Propagation time of the delay element plotted over the configuration word for                                                                                   |          |

|             | the 5 bit current DAC                                                                                                                                           | 86       |

| 6.19        | Schematic of a ring amplifier in a switched-capacitor feedback network                                                                                          | 87       |

| 6.20        | Schematic of the implemented residue amplifier with a ring amplifier at its core.                                                                               | 89       |

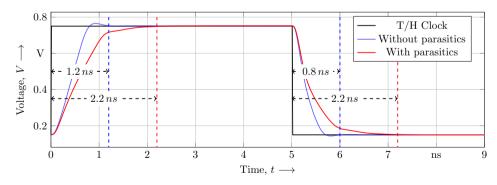

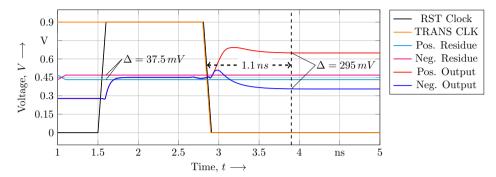

| 6.21        | Settling behavior of the implemented residue amplifier with parasitic post-layout elements                                                                      | 90       |

| 6 22        | Schematic of the monotonic switching scheme with reversely connected MSB                                                                                        |          |

| 0.22        | capacitors and half-unit capacitors for the second stage 8 bit SAR ADC                                                                                          | 91       |

| 6.23        | Illustration of the capacitor distribution in the CDAC of the second stage SAR                                                                                  |          |

| 0.23        | ADC                                                                                                                                                             | 92       |

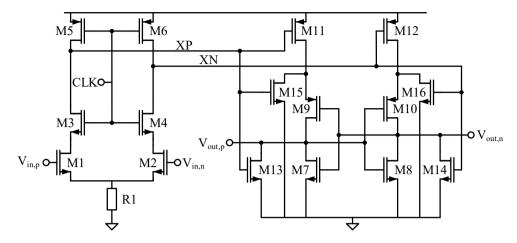

| 6.24        | Schematic for the modified comparator for the second stage SAR ADC                                                                                              | 92       |

| 6.25        | Output of the comparator implemented in the second stage SAR ADC                                                                                                | 93       |

| 6.26        | Layout screenshot of the implemented software-configurable ADC                                                                                                  | 93       |

| 0.20        | Layout sercensifor of the implemented software-configurable ADC                                                                                                 | フ、       |

| 7.1         | Measurement setup for the implemented SAR ADC                                                                                                                   | 95       |

| 7.2  | Measured SNDR and SFDR plotted over the sample rate for the second stage          |

|------|-----------------------------------------------------------------------------------|

|      | 8 bit SAR ADC for the low-power mode                                              |

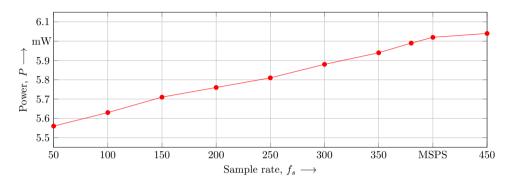

| 7.3  | Measured power consumption plotted over the sample rate of the implemented        |

|      | second stage 8 bit SAR ADC for the low-power mode                                 |

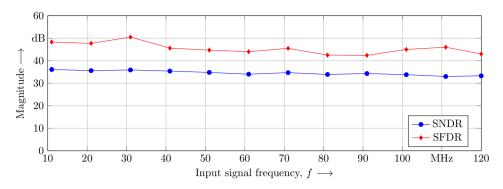

| 7.4  | Measured ENOB and SFDR plotted over the input signal frequency of the second      |

|      | stage 8 bit SAR ADC for the low-power mode                                        |

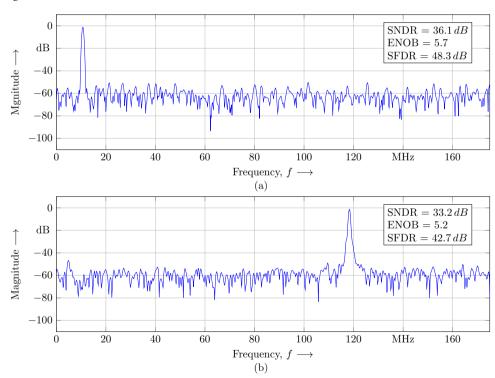

| 7.5  | Measured spectrum of the implemented second stage 8 bit SAR ADC at a sample       |

|      | rate of 350 MSPS. (a) Spectrum for a low frequency input signal of 11 MHz. (b)    |

|      | Spectrum for the maximum available input frequency of 120 MHz 99                  |

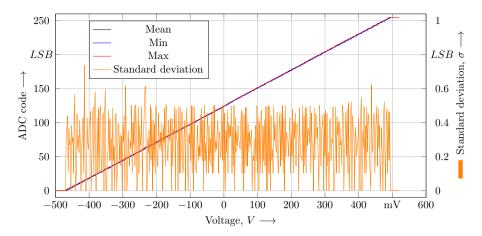

| 7.6  | Measured output characteristic of the implemented second stage 8 bit SAR ADC. 100 |

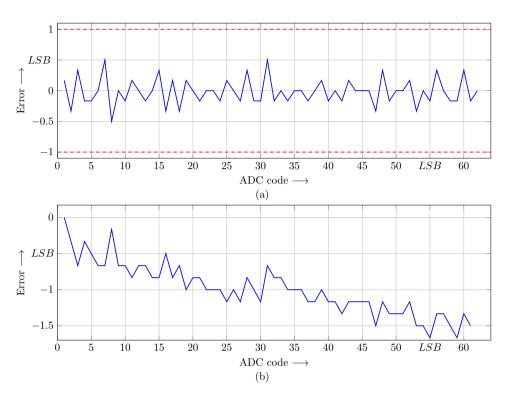

| 7.7  | (a) Measured DNL and (b) measured INL of the implemented second stage 8 bit       |

|      | SAR ADC                                                                           |

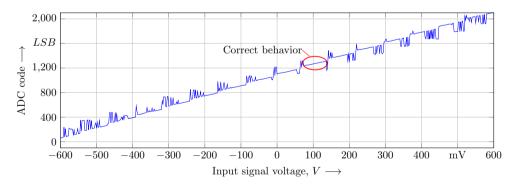

| 7.8  | Measured erroneous output characteristic of the implemented pipelined 11 bit      |

|      | SAR ADC for the high-precision mode with the nominal common-mode voltage          |

|      | of 450 mV                                                                         |

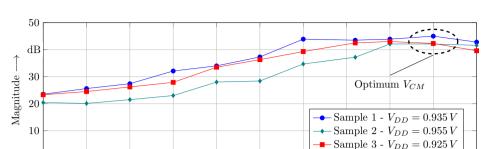

| 7.9  | SNDR plotted over input common-mode voltage of the implemented pipelined          |

|      | 11 bit SAR ADC for three samples                                                  |

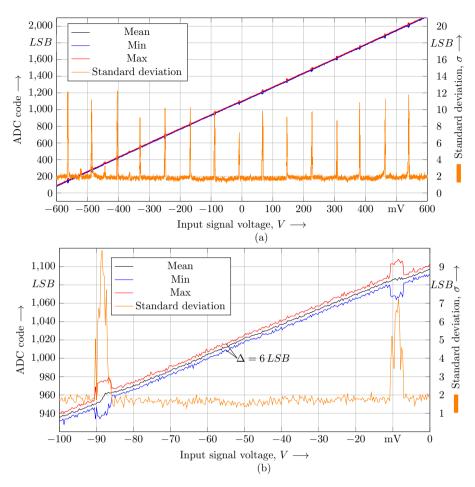

| 7.10 | \' \ 1                                                                            |

|      | ADC for the high-precision mode with an adjusted common-mode voltage              |

|      | of 490 mV. (b) Close up between -100 mV and 0 mV highlighting the large           |

|      | standard deviation every 128 LSBs                                                 |

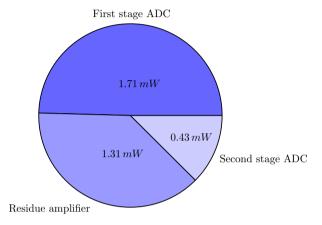

| 7.11 | SNDR plotted over input common-mode voltage of the implemented pipelined          |

|      | 11 bit SAR ADC for three samples. The total power consumption thus sums up        |

|      | to 3.45 mW                                                                        |

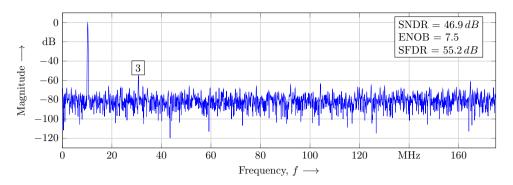

| 7.12 | Measured spectrum of the implemented pipelined 11 bit SAR ADC for the             |

|      | high-precision mode with an input signal frequency of 10.99 MHz 107               |

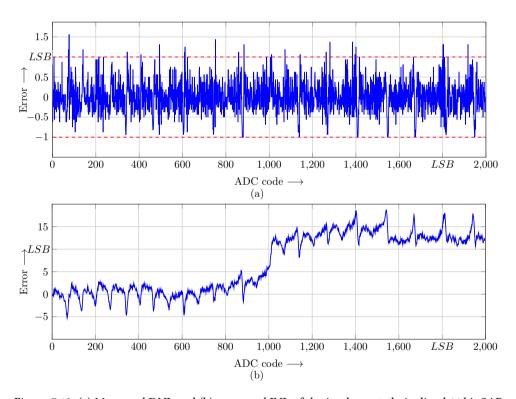

| 7.13 | (a) Measured DNL and (b) measured INL of the implemented pipelined 11 bit         |

|      | SAR ADC for the high-precision mode at a sample rate of 350 MSPS 107              |

# **List of Tables**

| 2.1        | ADCs with best performance in one category among publications in ISSCC and VLSI circuit symposium from 1997 to 2023 [43]                                                                                                                                                                                                                                                | 28  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.1<br>4.2 | Properties of most prominent switching schemes and the switching scheme adopted in this thesis for the CDAC in SAR ADCs. The values given in this table are calculated assuming a 10 bit resolution of the ADC Specifications for the input buffer of the implemented SAR ADC. The high requirements to the gain error are derived from investigations for a future use | 44  |

|            | in a high-resolution, pipelined ADC                                                                                                                                                                                                                                                                                                                                     | 53  |

| 5.1        | Performance summary for the implemented 6 bit SAR ADC                                                                                                                                                                                                                                                                                                                   | 69  |

| 6.1        | Specifications for the residue amplifier.                                                                                                                                                                                                                                                                                                                               | 89  |

| 7.1        | Performance summary for the implemented 8 bit SAR ADC in standalone operation for the low-power mode                                                                                                                                                                                                                                                                    | 101 |

| 7.2        | Performance summary for the implemented pipelined 11 bit SAR ADC for the                                                                                                                                                                                                                                                                                                |     |

|            | high-precision mode.                                                                                                                                                                                                                                                                                                                                                    | 108 |

# **Acronyms**

**AC** Alternating Current

ADC Analog-to-digital Converter BJT Bipolar Junction Transistor

CDAC Capacitive Digital-to-analog Converter

CMOS Complementary Metal-oxide Semiconductor

CPU Central Processing Unit

DAC Digital-to-analog Converter

dBc Decibel Relative To The Carrier

dBFS Decibel Relative To Full Scale

DC Direct Current DFF D Flip-flop

**DNL** Diferential Nonlinearity

**DR** Dynamic Range

**ENOB** Effective Number Of Bits

**FoM** Figure Of Merit

FoMs Schreier Figure Of Merit

FoMw Walden Figure Of Merit

IC Integrated Circuit

INL Integral Nonlinearity

JTAG Joint Test Action Group

LSB Least Significant Bit

**LVDS** Low Voltage Differential Signaling

MOSFET Metal-oxide-semiconductor Field-effect Transistor

MSB Most Significant Bit

**NMOS** N-type Metal-oxide Semiconductor

PCB Printed Circuit Board

**PMOS** P-type Metal-oxide Semiconductor

**PSD** Power Spectral Density

**PVT** Process, Voltage And Temperature

QFN Quad-flat No-leads RMS Root-mean-square

SAR Successive Approximation Register

SFDR Spurious-free Dynamic Range

SNDR Signal-to-noise-and-distortion Ratio

**SNR** Signal-to-noise Ratio

SRAM Static Random-access Memory THD Total Harmonic Distortion

Chapter 1

# Introduction

#### 1.1 Motivation

Since the invention of the first transistor in the Bell Labs in 1947, integrated circuits (ICs) rapidly evolved fitting nowadays triple-digit million transistors on a square millimeter of silicon. The latest complementary metal-oxide semiconductor (CMOS) process node generation at the writing of this thesis is 3 nm, albeit node notations have become only a marketing term and there are no physical structures on the chip, that actually have these dimensions. The steadily growing integration and the performance per power and area, paved the way for microchip's ubiquity, advancing the functionality of applications and enabling the feasibility of complex implementations. But with it also the fabrication methods became highly sophisticated; so much, that manufacturing companies offering the latest process node generation thinned due to the unbearable cost of modern fabrication facilities, leaving only a few. There is not much publicly available information about the current user share of the different technology nodes in the industry and research as manufacturing foundries are very restrictive about their data and most is confidential, but a rough insight can be derived from the user report of EUROPRACTICE [1]. The platform EUROPRACTICE acts as an interface between customer and technology providers for IC design software and manufacturing alleviating the cost by collecting designs from different clients on multi-project wafer runs or use multi level masks. It is mainly used by research facilities in Europe, but also to a lesser degree by startups and businesses with small volume production. Figure. 1.1a illustrates the current state of the process technology distribution. The vast majority is still using 65 nm, introduced in 2005, and larger nodes. This is attributed to the exponential increase of cost as indicated by Fig. 1.1b. It should be noted, that it only shows the manufacturing cost. As complexity increases, the time effort for design, layout and verification also grows exponentially contributing an even higher amount to the overall cost. For more advanced nodes design methods change drastically, which forces new architectures making old intellectual property obsolete. It would mean a start from scratch, which discourages transfer.

Particle detector experiments have a high requirement for spatial resolution necessitating many sensors in a confined space. Additionally, these experiments are exposed to harsh environments hostile to electronics. Off-the-shelf components do not meet these requirements, which is why custom ICs are often developed by the particle detector community. The developments in this thesis are not limited to particle detectors, but as its first target application, derive legitimization from it. This research area reflects the current node distribution shown in Fig. 1.1a well, albeit 65 nm bulk CMOS being the state-of-the-art, while older process nodes are

Figure 1.1: (a) Share of the individual process node on the overall manufactured chips. (b) Manufacturing cost for process nodes in a multi-project wafer run [1].

still heavily used [2]. It was also concluded, that while a transfer for future detector experiments to more advanced nodes is inevitable to achieve new discoveries, the complexity and therewith the cost exceed the capacities of individual research groups. Future developments therefore have to be accomplished in joint efforts, distributing different circuit blocks among research groups. But this also implicates, that future electronics become more generic covering multiple detector experiment requirements [3]. This trend will likely also be seen in other research areas relying on IC design as the overwhelming complexity is a universal problem.

The analog-to-digital converter (ADC) is the bridge between the analog and digital domain. It is therefore needed whenever a signal from the real world is to be investigated and processed computationally. This spans from simple applications like weight displaying on a scale to complex wireless communication modulation enabling high bandwidths. As digital processing capabilities increase, so is the role of ADCs becoming one of the most important building blocks. Coincidentally, it is also among the most complex blocks consisting of many sub circuits both of analog and of digital nature. Its development is a lengthy process that accounts for a major part of the resources and poses a high risk to the success of a whole project. A ready and fully-verified generic ADC especially will therefore reduce the overall time and effort for custom chip design significantly. Prototyping and verification of new concepts can also be facilitated. Furthermore proving, that generic approaches can be implemented successfully and bring overall benefits, if used in combination with modern process nodes, is an important milestone for the assessment of future chip design in research.

### 1.2 Outline of the Thesis

The structure of this thesis is a follows. In chapter two the fundamentals for ADCs as well as fundamental architectures and the state of the art for ADCs are summarized. Chapter three presents the concept for a software-configurable ADC intended to be used in more generic chips,

that cover a broad range of applications. Furthermore, the choice of the process technology node for the implementation is explained. Following, chapter four gives detailed insight in the design of the first chip. It is a pre-development done to get familiar with the new process technology and its characteristics. The chip's main feature is a simple, low-resolution ADC, that serves as the basis for the continued development towards more sophisticated ADCs. Chapter five reports the measurement results of the performance of the ADC and puts them into context in a discussion. Chapter six then covers all aspects of the creation of a first software-configurable ADC which has two resolution modes, a low-power mode and a high-precision mode, and is implemented two times in parallel for read out of two channels. Chapter seven presents the measurement results and discusses the achieved performance. Finally, chapter eight gives a conclusion and outlook for future works.

# Fundamentals of the Analog-To-Digital Converter

# 2.1 Principle Theory of Operation

Figure 2.1: Fundamental elements of an ADC

An ADC translates an analog signal in the form of a voltage or current to a digital representation. It comprises of three core functionalities, it has to accomplish, as illustrated in Fig. 2.1. At first, a sampling block forms the signal to discrete-time by allowing it to only pass on in periodic intervals. Subsequently, a quantizer compares the signal to fixed thresholds transforming it to a discrete value. Finally, an encoder provides a binary bit representation of the analog sample. The physical resolution of an ADC is given in bit. It is a measure for the ideal amount of signal levels that can be differentiated and doubles with every additional bit implemented in the ADC. Mathematically, this relation is expressed as

Detectable signal levels =

$$2^N$$

. (2.1)

Here, N is the resolution in bit. A 12 bit ADC for example therefore has ideally  $2^{12} = 4096$  steps it can resolve.

#### 2.2 Fundamental Limits

#### 2.2.1 Quantization Noise

The quantization interval, measuring the minimum detectable change in a signal magnitude, can be described mathematically as

$$\Delta = \frac{V_{FS}}{2^N}. (2.2)$$

Here,  $V_{FS}$  represents the maximum peak-to-peak voltage an ADC can handle and N is the resolution in bit. An exemplary, ideal output characteristic of an ADC is shown in Fig. 2.2a to illustrate the form and distribution of quantization intervals. In this case the 3 bit ADC has eight quantization intervals with a  $V_{FS}$  of 1 V, depicted also in steps of eighths to make the transitions more clear. Notice, that the maximum digital value "111" represents the analog value 7/8 V full scale. The maximum digital scale is inherently always one least significant bit (LSB) below the analog full scale. Usually, the value representing a digital output is chosen as the mid-point of the quantization interval as illustrated with a linear, red line going through all mid-points in the figure. With this definition a quantization error occurs between the real analog value and its digital representation ranging from -1/2 LSB to +1/2 LSB as shown in Fig. 2.2b.

To get a general understanding of the effect quantization has on alternating current (AC) signals, a mean error is approximated called quantization noise. It can be derived from the sawtooth waveform in Fig. 2.2b having a peak-to-peak amplitude of q. With this the quantization error can be described as

$$e(t) = st, \frac{-q}{2s} < t < \frac{q}{2s}.$$

(2.3)

t represents the time and s the slope of the sawtooth waveform here. Forming the root-mean-square (RMS) will result in

RMS quantization noise =

$$\sqrt{\overline{e^2(t)}} = \sqrt{\frac{s}{q} \int_{-\frac{q}{2s}}^{\frac{q}{2s}} (s\,t)^2 dt} = \frac{q}{\sqrt{12}}$$

. (2.4)

The analysis of quantization noise and its spectrum was investigated in detail by [4]. It shows, that the derivation of the quantization noise from a simple sawtooth shape for the error presented here holds for most signal forms. It is approximately Gaussian and has a uniform spread over the the Nyquist bandwidth. One general assumption is that the quantization noise is uncorrelated with the input signal. If this is not the case, it appears centered around the harmonics deteriorating the signal quality. Strictly, whenever the ratio between the sampling frequency and the input signal frequency is a rational number which is always the case the quantization error is correlated with the input signal, because there is bound to be a periodicity after a certain amount of cycles. In reality, other noise sources alleviate this problem acting as a dither to randomize the quantization noise spectrum. Nonetheless, picking the right sampling frequency to weaken the impact of quantization noise correlation is a crucial step in every application.

Figure 2.2: (a) Ideal output characteristic for a 3 bit ADC and its eight quantization intervals. (b) Resulting quantization error for the individual quantization intervals.

#### 2.2.2 kTC Noise

Thermal noise, discovered by John B. Johnson in 1926 and explained by Harry Nyquist in a paper in 1928 [5], has a RMS voltage for a given bandwidth of

$$v_n = \sqrt{\overline{v_n^2}} \sqrt{\Delta f} = \sqrt{4 k_B T R \Delta f}. \tag{2.5}$$

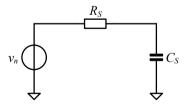

$k_B$  is the Boltzmann constant, T is the temperature in Kelvin, and R is the resistance. In combination with a capacitor which forms the equivalent circuit of a classical sampler of an ADC, the noise coming from the resistor shows a different behavior. Assume the following configuration as shown in Fig. 2.3.  $R_S$  is the equivalent resistance of the sampling switch,  $C_S$  is

Figure 2.3: Equivalent noise circuit of a classical sampler in an ADC.

the sampling capacitance and  $v_n$  is the equivalent noise source for the resistance. The absolute voltage over the sampling capacitor  $C_S$  is calculated as

$$|v_{n,C}| = v_n \frac{1}{\sqrt{1 + (\omega RC)^2}}.$$

(2.6)

This corresponds to the spectral noise voltage at one frequency. Equation 2.5 on the other hand is defined for a bandwidth  $\Delta f$ . To be able to insert it in the equation, an infinitesimal range is used

$$dv_n = \sqrt{4 k_B T R df}. ag{2.7}$$

Now, the equations combines to

$$|dv_{n,C}| = \sqrt{\frac{4 k_B T R df}{1 + (\omega R C)^2}}.$$

(2.8)

It is squared as it eases the subsequent integration over the frequency. The final equation

$$\overline{v_{n,C}^2} = \int_0^\infty \frac{4 \, k_B \, T \, R}{1 + (\omega \, R \, C)^2} df = \frac{k_B \, T}{C} \tag{2.9}$$

reduces to a simple form which is only dependent on the temperature and the capacitance in the circuit. The resistance has no impact on the overall noise anymore. This is due to the fact that an increase in the thermal noise voltage is negated by the reduced cutoff frequency of the lowpass formed by the resistance and the capacitance. As the kTC noise goes to zero only if the capacitance becomes infinitely large or the temperature goes to zero, it is a an unavoidable noise and therefore a fundamental limit for ADCs. As it only depends on  $k_B$ , T and C, it is referred to as kTC noise.

#### 2.2.3 Jitter

For the reconstruction of a signal or further processing it is assumed that every sample is taken in equidistant steps. In real-world scenarios however this is not the case. There are several effects that influence the exact sampling point of a signal. Static effects like slope of the sampling clock, parasitics of the traces off- and on-chip going from the clock to the sampling switch or buffer delays, cause only a static delay by shifting every sample by the same amount. They therefore produce no error in the sampled signal. An exception make time-interleaved ADCs that use multiple ADCs in parallel to convert a signal to the digital domain. Here, the delay of the clock signals leading to the individual ADCs, has to be reduced to sufficient levels either by careful design and layout or mitigated by calibration stages.

Time-varying effects have a much more severe impact on the quality of the signal. They are caused for example directly by the noise coming from circuits like buffers used in the clock path or are picked up by the clock lines from other nearby traces and circuits. The quality of the clock source is also a major contributor to sampling uncertainties. For very high frequencies a mismatch of the clock line going into the chip also causes deterioration and is mitigated by moving from a square wave signal as clock signal to a sinusoidal clock signal instead which is rectified on-chip. All time-varying effects can be summed up to one single term which is referred to as jitter.

To calculate the resulting noise caused by jitter, first a simple sinus function is defined as

$$v(t) = V_0 \sin(2\pi f_{sig} t). \tag{2.10}$$

$V_0$  is here the amplitude of the input signal voltage and  $f_{sig}$  is the input signal frequency. Forming the derivation

$$\frac{d v(t)}{d t} = 2 \pi f_{sig} V_0 \cos(2 \pi f_{sig} t)$$

(2.11)

and taking the RMS of it

$$\left(\frac{dv(t)}{dt}\right)_{rms} = \frac{2\pi f_{sig}V_0}{\sqrt{2}} \tag{2.12}$$

yields the average slope of the sinus. Substituting in,  $\Delta v_{rms}$  is the RMS voltage error which the jitter produces and  $\Delta t_{rms}$  is the RMS time value the sampling point diverges from the ideal value. With this, the term results in

$$\frac{\Delta v_{rms}}{\Delta t_{rms}} = \frac{2\pi f_{sig} V_0}{\sqrt{2}}.$$

(2.13)

Often,  $\Delta t_{rms}$  is represented by  $\sigma_j$ . The final equation for the voltage error through jitter concludes to

$$\Delta v_{rms} = \frac{2 \pi f_{sig} V_0 \sigma_j}{\sqrt{2}}.$$

(2.14)

It should be underlined that the frequency  $f_{Sig}$  here is the signal frequency and not the sampling frequency. Accordingly, the effect of jitter has less effect on low-frequency signals, while at very high frequencies it becomes the limiting factor for the resolution.

## 2.3 Fundamental Characterization Units

### 2.3.1 Signal-to-Noise Ratio

The signal-to-noise ratio (SNR) is the ratio of the power of a signal and the noise that affects the signal quality. Harmonic distortions are not taken into account here. It is defined as

$$SNR = 20 \log_{10} \left( \frac{RMS \text{ value of FS signal wave}}{RMS \text{ value of noise}} \right). \tag{2.15}$$

Its unit is the decibel, dB in short. FS stands for full scale. In the following, the SNR for the previously described main noise sources is calculated and its impact contextualized.

#### 2.3.1.1 SNR for Quantization Noise

The SNR for the quantization noise is calculated assuming a sinus wave input. To arrive at the RMS of a sinus signal, the following equation has to be solved

$$v_{sin,rms} = \sqrt{\frac{1}{T} \int_{t_0}^{t_0 + T} (V_0 \sin(\omega t))^2 dt}.$$

(2.16)

$V_0$  is here the amplitude of the signal. With the help of the relation

$$\sin^2(x) = \frac{1}{2} \left( 1 - \cos(2x) \right) \tag{2.17}$$

the integral can be solved. The equation can now easily be resolved to

$$v_{sin,rms} = \sqrt{V_0^2 \frac{1}{2}} = \frac{V_0}{\sqrt{2}}. (2.18)$$

With the amplitude expressed as a multiple of the quantization interval q in the form of  $V_0 = \frac{q \cdot 2^N}{2}$  the RMS voltage for a sinus signal is finally given as

$$v_{sig,rms} = \frac{q \, 2^N}{2 \, \sqrt{2}}.\tag{2.19}$$

Inserting this and the equation for the RMS quantization noise into 2.15, the expression changes to

$$SNR_{quant} = 20 \log_{10} \left( \frac{\frac{q \, 2^{N}}{2 \, \sqrt{2}}}{\frac{q}{\sqrt{12}}} \right)$$

$$= (6.02 \, N - 9.03 + 10.79) \, dB$$

$$= (6.02 \, N + 1.76) \, dB.$$

(2.20)

6.02 dB stems from the doubling in precision with every bit, -9.03 is the amount subtracted for using a sinus wave as input and 10.79 is added, because the RMS value of the quantization noise  $\frac{q}{\sqrt{12}}$  is much smaller than the static quantization error q compensating for the statistically too pessimistic derivation from  $6.02\,N$  alone. Equation 2.20 can also be used to derive a equation for the effective number of bits (ENOB) as

$$ENOB = \frac{SNR_{dB} - 1.76 \, dB}{6.02 \, N \, dB}.$$

(2.21)

The SNR in this equation includes noise from all sources. Therefore, it measures the difference between the SNR of ideal quantization noise which calculates the amount of physical bits, and the actual SNR to get the reduced amount of bits, called ENOB. The correction factor for the quantization noise is still applied as it accounts for the augmentation from the statistical distribution of the quantization noise which would otherwise lead to a too-high ENOB.

#### 2.3.1.2 SNR for Jitter

The SNR for jitter noise is given by

$$SNR_{jitter} = 20 \log_{10} \left( \frac{v_{sig,rms}}{v_{jitter,rms}} \right).$$

(2.22)

With  $v_{siq,rms} = V_0/\sqrt{2}$  being the RMS voltage of a sinus wave, the equation becomes

$$SNR_{jitter} = 20 \log_{10} \left( \frac{\frac{V_0}{\sqrt{2}}}{\frac{2 \pi f_{sig} V_0 \sigma_j}{\sqrt{2}}} \right) = 20 \log_{10} \left( \frac{1}{2 \pi f_{sig} \sigma_j} \right).$$

(2.23)

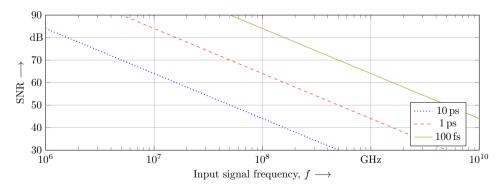

Figure 2.4 illustrates the effect of clock jitter on the SNR of an ADC plotted over the input signal frequency. Three different clock jitter values were chosen as an example in which 10 ps stands for a low-quality reference clock and 100 fs is a value of highest precision. As the trend for high-performance ADCs continues, it is clearly visible that at high signal frequencies, jitter becomes the dominant source of noise. To stay above an ENOB of 10 bit or an SNR above 62 dB which is generally regarded as the lower limit for high resolution, jitter values below 1 ps are necessary for signal frequencies above 100 MHz. These requirements are difficult to achieve and shift a great portion of the design effort towards the clock source and distribution. One should also keep in mind that this is only the SNR attributed to the jitter noise and other noise source reduce the resolution further so that in general the SNR of jitter noise should be higher than the ultimately needed overall SNR.

Figure 2.4: Maximum reachable SNR for different values of jitter plotted over the input signal frequency.

#### 2.3.1.3 SNR for kTC Noise

The SNR for kTC noise is calculated by

$$SNR_{kTC} = 20 \log_{10} \left( \frac{v_{sig,rms}}{v_{kTC,rms}} \right). \tag{2.24}$$

With  $v_{siq,rms} = V_0/\sqrt{2}$  being the RMS voltage of a sinus wave, the equation resolves to

$$SNR_{kTC} = 20 \log_{10} \left( \frac{\frac{V_0}{\sqrt{2}}}{\sqrt{\frac{k_B T}{C}}} \right) = 20 \log_{10} \left( V_0 \sqrt{\frac{C}{2 k_B T}} \right). \tag{2.25}$$

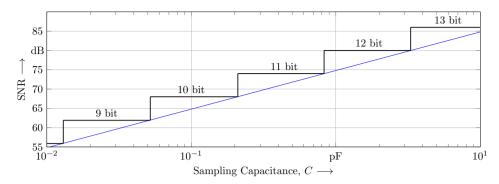

This time, the SNR is also dependent on the magnitude of the input signal. Figure 2.5 shows the limit of the SNR caused by kTC noise plotted over the sampling capacitance of an ADC assuming a signal amplitude of 0.5 V. Additionally, the black stair plot shows the resolution in integer ENOB steps as a rough guideline for the needed capacitance. As a side note, choosing a capacitance close to the lower bound for the respective ENOB leaves less design margin for other noise sources, threatening the intended resolution target. While for lower capacitance values an increase has a large effect on the overall noise generated (mind the logarithmic representation here), it diminishes further when a higher SNR is required. The consequence is a high area consumption on-chip for the sampling capacitor alone and a high power consumption. Therefore, it makes sense after a certain SNR to increase the magnitude of the input signal, although it has a quadratic effect on the power consumption, compared to the linear influence on power consumption of the capacitance. Note that the power consumption to charge a capacitor follows the relation  $P \propto C V^2$ . Unfortunately, in modern process technologies, the maximum available supply voltage is limited to very low levels, typically around 1 V. This dilemma may be circumvented by introducing new design techniques. An upcoming method is omitting the sampling stage altogether by using so called continuous time ADCs [6]. Another method leverages kTC noise cancellation to keep the sampling capacitance size small [7] [8].

#### 2.3.1.4 Combined Overall SNR

To arrive at a term to describe the SNR for all aforementioned noise sources, the power of these has to be combined as follows

$$SNR_{all} = 10 \log_{10} \left( \frac{P_{sig,rms}}{P_{kTC,rms} + P_{quant,rms} + P_{jitter,rms}} \right).$$

(2.26)

As a remark, it is switched back to power here, because only the power for RMS adds, not the voltage. Transforming this equation to align its shape with the others and describe all noise

Figure 2.5: SNR caused by kTC noise plotted over the sampling capacitance of an ADC and a signal amplitude  $V_0$  of 0.5 V. The stair plot shows the resolution in integer ENOB steps as was done in [9].

sources as SNR yields

$$\begin{aligned} & \text{SNR} = 10 \, \log_{10} \left( \frac{P_{sig,rms}}{P_{kTC,rms} + P_{quant,rms} + P_{jitter,rms}} \right) \\ & = -10 \, \log_{10} \left( \frac{P_{kTC,rms} + P_{quant,rms} + P_{jitter,rms}}{P_{sig,rms}} \right) \\ & = -10 \, \log_{10} \left( \left( \frac{v_{kTC,rms}}{v_{sig,rms}} \right)^2 + \left( \frac{v_{quant,rms}}{v_{sig,rms}} \right)^2 \left( \frac{v_{jitter,rms}}{v_{sig,rms}} \right)^2 \right) \\ & = -10 \, \log_{10} \left( 10 \, \frac{-SNR_{kTC}}{10} + \frac{-SNR_{quant}}{10} + \frac{-SNR_{jitter}}{10} \right). \end{aligned} \tag{2.27}$$

#### 2.3.2 Total Harmonic Distortion

The total harmonic distortion (THD) describes the ratio of the sum of the powers of the harmonic components to the power of the fundamental of the input signal. Its equation describes the relation as follows

THD = 20

$$\log_{10} \left( \frac{\sqrt{V_2^2 + V_3^2 + \dots + V_n^2}}{V_1} \right)$$

. (2.28)

$V_1$  is the fundamental and all higher V are harmonics respectively. Harmonics are caused by nonlinearities in a device and are always positive integer multiples of the fundamental frequency which is the original input signal frequency. Harmonics and aliased harmonics are determined by  $|\pm K f_{sample} \pm n f_{sig}|$ , where n is the number of the harmonic and  $K \in \mathbb{N}$ . This is illustrated in Fig. 2.6 showing the fundamental of a signal at 10 MHz and its second, third and fifth harmonic at 20 MHz, 30 MHz and 50 MHz respectively. THD is usually specified in decibel

20

relative to the carrier (dBc), or decibel relative to full scale (dBFS). The first describes the power

Figure 2.6: Spectrum of a signal highlighting the fundamental and harmonics.

80

Frequency,  $f \longrightarrow$

ratio of a signal to a carrier signal, in this case the fundamental. The latter also compares to the power of the fundamental, but assumes that a full-scale signal is applied. As the spectrum is usually normalized to the full-scale signal, dBFS thus always relates to 0 dB.

### 2.3.3 Signal-to-Noise-and-Distortion Ratio

40

60

To arrive at the most complete measure of the dynamic performance of an ADC, the sum of the noise and harmonics, excluding direct current (DC) is considered for the signal-to-noiseand-distortion ratio (SNDR). In mathematical terms, it is described by

$$SNDR = 10 \log_{10} \left( \frac{P_{sig,rms}}{P_{noise,rms} + P_{dist,rms}} \right). \tag{2.29}$$

120

100

MHz

160

SNDR is usually plotted over frequency. For ADCs with very high resolution, the input signal often needs to be refined, for example by a bandpass filter, to not have an effect on the measured performance. This makes a sweep difficult, but at least a number at low frequency and at high frequency, close to the maximum bandwidth of the ADC, should be given.

## 2.3.4 Dynamic Range

The dynamic range (DR) is a measure of the range of the input signal power for which useful outputs can be expected from an ADC. It describes the ratio between a full-scale input signal and the noise floor level in the spectrum. It is therefore specified in decibel. A mathematical expression is given as

$$DR = 10 \log_{10} \left( \frac{P_{sig,rms,max}}{P_{sia,rms,min}} \right). \tag{2.30}$$

Here,  $P_{sig,rms,max}$  is measured for a full-scale input signal and  $P_{sig,rms,min}$  describes the minimum detectable signal. A common used definition is the signal power at the point when SNDR is 0 dB.

It is still used in ADCs that do not have a physical representation of the targeted resolution in bit, like oversampling and noise-shaping ADCs. Otherwise, a more common and useful parameter to define the minimum detectable signal in the frequency domain is given with the adaption described in the following section.

### 2.3.5 Spurious-Free Dynamic Range

The spurious-free dynamic range (SFDR) is an indicator for the smallest detectable signal distinguishable from other spectral components in the bandwidth. It is an important metric in communication applications and describes the ratio of the RMS value of the signal to the largest spectral noise component or harmonic which are called spurs. As equation, it is expressed as follows

$$SFDR = 10 \log_{10} \left( \frac{P_{sig,rms}}{P_{spur,max,rms}} \right). \tag{2.31}$$

Usually, the second or third harmonic is the limiting factor for the SFDR. In more complex applications, like systems on a single chip, other components can create spurs that have a bigger impact than the harmonics itself.

## 2.3.6 Differential Nonlinearity

The differential nonlinearity (DNL) is a DC characteristic and measures the deviation from the ideal step width for one digital code of the ADC between adjacent codes. Mathematically, this is expressed as following

$$DNL(k) = \frac{w(k) - w_{ideal}}{w_{ideal}}, \quad w(k) = X(k+1) - X(k).$$

(2.32)

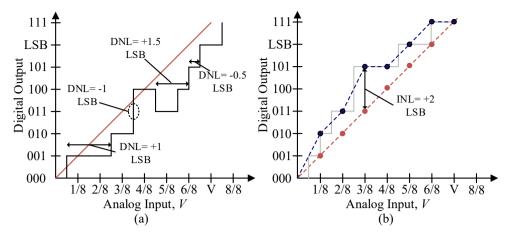

w(k) is the width for the currently investigated digital code. It is defined by the transition point X(k+1) from the current code to the next digital code, minus the transition point X(k) from the last code to the current code.  $w_{ideal}$  represents the ideal code width which is 1 LSB. Figure. 2.7a illustrates different DNL errors. In general, for positive DNL errors the step width increases, for negative DNL errors the step width decreases. At DNL = -1 the step for the current code disappears completely, leading to a missing code in the ADC output. With this definition, the DNL for ADCs cannot decrease lower than -1. A DNL >1 can be an indicator for a non-monotonicity, as seen around the code "100" in Fig. 2.7a. Monotonicity is crucial for some applications, e.g in control loops, where otherwise instabilities can occur. To assure the operation of an ADC without missing codes and non-monotonicities, |DNL| < 1 has to be fulfilled for all values. A diagram showing an example how a measured DNL is usually presented can be seen in Fig. 2.8a. An 8 bit ADC was used here to plot the DNL error in LSBs for every possible ADC code.

Figure 2.7: (a) A DC output characteristic of an ADC showing different DNL errors.

(b) A DC output characteristic of an ADC showing the integral nonlinearity (INL) error of the output in blue compared to the ideal transfer curve shown here in red.

## 2.3.7 Integral Nonlinearity

Another measure of the nonlinearity is the integral nonlinearity (INL). Here, the output transfer characteristic of an ADC is compared to a straight line. In general, there are different methods to define this line. In the first, the unadjusted INL, the ideal output characteristic of the ADC is used. This results in the raw, absolute error produced at every step. A more common approach is the so called endpoint INL. It draws the reference line starting at the origin and ending at the full-scale output of the ADC after it was corrected for gain and offset errors by trimming out the endpoint errors at the zero and full-scale codes. With this the INL at the starting point and the end point is therefore also zero. As virtually all ADCs exhibit offset and gain errors and they are easily correctable, it is a reasonable method. It still shows the true, absolute error that can be expected from the ADC. Best-fit INL is the third method. Here, the straight line is fitted with standard curve fitting techniques in such a way that the overall error for all codes is minimized. With this only the relative error is considered. It highlights the distortion in an ADC at the expense of absolute precision and is therefore more meaningful for AC applications. Figure 2.7b shows an exemplary nonlinear output characteristic. For the analog input voltage "3/8" which ideally responds to the digital output "011" the ADC puts out the code "101" which produces an absolute error of 2 LSB. This can also be expressed with this equation

$$INL(k) = \frac{C_{ADC}(k) - C_{ideal}(k)}{w_{ideal}}, \quad k = 2...N.$$

(2.33)

Here,  $C_{ADC}(k)$  describes the current output code and  $C_{ideal}(k)$  the ideal code of the ADC. An alternative method to obtain the INL is by summing the calculated DNL errors up until the currently investigated code:

$$INL(k) = \sum_{i=1}^{k-1} DNL(i), \quad k = 2...N.$$

(2.34)

Notice, that for the calculation of the INL, the constraints INL(0) = not defined and INL(1) = 0 apply. A diagram showing an example how a measured INL is usually presented can be seen in Fig. 2.8b. An 8 bit ADC was used here to plot the INL error in LSBs for all ADC codes.

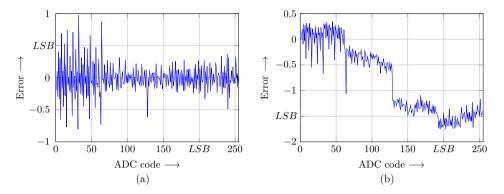

Figure 2.8: (a) Exemplary DNL of a 8 bit ADC. (b) Exemplary INL of a 8 bit ADC.

## 2.3.8 Figure of Merit

In the past various figure of merits (FoMs) have been introduced to easily and compactly compare the performance of an investigated device on the basis of a single number. For analog circuits, and in particular for ADCs, there are many different aspects to consider, when defining performance. Among these are power consumption, resolution, sample rate, area, yield, power supply rejection ration, analog bandwidth and process technology. Processing all these metrics into a single FoM is an impossible challenge. The two FoMs that prevailed and are used nowadays, therefore use only three, arguably the most impactful, parameters, namely power consumption, resolution and sample rate. For the same reason, it is advisable to compare ADCs through FoMs only, if they lie in the same field of requirements. In general, FoMs show their usefulness by indicating a trend in the development of ADCs. For closer comparisons, all characteristics should be considered. The two most popular FoMs are the Walden figure of merit (FoMw) and the Schreier figure of merit (FoMs). In technical reports it has become standard to give both despite their significantly different approach. They are introduced in the following.