Modelling, implementation and characterization of a Bias-DAC in CMOS as a building block for scalable cryogenic control electronics for future quantum comp<u>uters</u>

Patrick Norbert Vliex

Information Band / Volume 74 ISBN 978-3-95806-588-8

Forschungszentrum Jülich GmbH Zentralinstitut für Engineering, Elektronik und Analytik (ZEA) Systeme der Elektronik (ZEA-2)

## Modelling, implementation and characterization of a Bias-DAC in CMOS as a building block for scalable cryogenic control electronics for future quantum computers

Patrick Norbert Vliex

Schriften des Forschungszentrums Jülich Reihe Information / Information

Band / Volume 74

ISSN 1866-1777

ISBN 978-3-95806-588-8

Bibliografische Information der Deutschen Nationalbibliothek. Die Deutsche Nationalbibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliografie; detaillierte Bibliografische Daten sind im Internet über http://dnb.d-nb.de abrufbar.

| Herausgeber<br>und Vertrieb: | Forschungszentrum Jülich GmbH<br>Zentralbibliothek, Verlag<br>52425 Jülich<br>Tel.: +49 2461 61-5368<br>Fax: +49 2461 61-6103<br>zb-publikation@fz-juelich.de<br>www.fz-juelich.de/zb |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Umschlaggestaltung:          | Grafische Medien, Forschungszentrum Jülich GmbH                                                                                                                                       |

Druck: Grafische Medien, Forschungszentrum Jülich GmbH

Copyright: Forschungszentrum Jülich 2021

Schriften des Forschungszentrums Jülich Reihe Information / Information, Band / Volume 74

D 82 (Diss. RWTH Aachen University, 2021)

ISSN 1866-1777 ISBN 978-3-95806-588-8

Vollständig frei verfügbar über das Publikationsportal des Forschungszentrums Jülich (JuSER) unter www.fz-juelich.de/zb/openaccess.

This is an Open Access publication distributed under the terms of the Creative Commons Attribution License 4.0, This is an Open Access publication distributed under the terms of the <u>urbative commons</u> relations in First and foremost, I would like to start by thanking my examiners Prof. Stefan Heinen for supervision of my thesis work and Prof. Stefan van Waasen for giving me the opportunity to work on this truly interesting and motivating project at the Forschungzentrum Jülich. I want to express my deepest gratitude for all of your guidance during the work of this thesis.

Special thanks goes to my day-to-day supervisor Dr. Andre Kruth for offering a lot of his time and help with the thesis and the project, including all the support with the top level design, layout and the setup of design flow.

My deepest gratitude also goes towards my colleague and personal friend Dennis Nielinger. I thank you for suffering with me through long days and late evenings during the tape out. Your input in design, layout and verification as well as your commitment and hard work helped us to get the chip into production before the deadline. I also remember all the stressful, but thanks to you still enjoyable, evenings in the lab.

I would like to express the deepest appreciation to Dr. Carsten Degenhardt who helped me a lot during the course of the project. Your support with the handling of all the peripheral tasks surrounding the project helped me a lot in achieving this thesis.

In addition, I want to thank Anton Artanov and Christian Roth for all the help offered in measurement, verification and testing of the chips. I also thank Dr. Andre Zambanini, Dr. Pavithra Muralidharan and Daniel Liebau for the support on the digital side of things.

I would like to thank all my colleagues, at the Central Institute of Engineering, Electronics and Analytics - Electronic Systems (ZEA-2) who I have worked with, for their kindness and company.

Finally, I want to express a particular personal thank you to my parents, my brother and Jeanette. I could not imagine my life without your unconditional support and never-ending motivation.

Quantum computing is a research field of increasing attention and popularity, which has steadily gained momentum in the recent years. The promises made for universal QC are vast in terms of their predicted impact to science, economy and society. A universal quantum computer will be able to solve specific tasks up to exponentially faster than any modern supercomputer. Applications range from quantum chemistry in catalyst research and protein folding simulations to search algorithms for unordered databases and cryptography.

Quantum bits are typically operated inside a dilution refrigerator at temperatures close to absolute zero, i.e. < 1 K. The majority of the QC scientific research community agrees that an estimated number of  $\geq 10^6$  quantum bits are required to build an universal quantum computer. This number leads to foreseeable connectivity bottlenecks to fed all the required biasing, control and read-out signals into the cryostat.

This work is using a TSMC 65 nm CMOS technology to integrate classical control electronics closer with the quantum bits and thus pave a way for scalability. Other publications showed the feasibility of operating CMOS technologies at deep cryogenic temperatures. Whereas various papers presented implementations of cryogenic electronics for quantum bit control, a scalable solution for quantum bit biasing is missing and is the focus of this work.

A capacitive digital-to-analog converter (DAC) for biasing of quantum bits is modeled, implemented and characterized at cryogenic temperatures. Special emphasis is placed upon achieving a systematically scalable and ultra-low power DAC design. The DAC design includes a reference voltage coarse tuning scheme in order to lower power consumption and increase resolution. Two calibration procedures to mitigate gain error induced output voltage jumps are described and the most promising approach is verified at cryogenic temperatures. Auxiliary circuitry is added to enable DAC characterization, i.e. operational amplifiers and a  $\Sigma\Delta$  modulator. System level considerations as well as implementation details and measurement results for of all these circuit blocks are presented.

The design and implementation of a bandgap reference and a linear regulator, which are investigated as building blocks for cryogenic supply and reference voltage regulation, are also described. Measurement results of these circuit blocks at cryogenic temperatures are also part of this work.

All circuit designs are aimed at optimum robustness and high configurability in order to cope with cryogenic CMOS effects and the lack of valid device models in the temperature regime of interest.

| Ac  | knov               | vledgement                                   | i   |

|-----|--------------------|----------------------------------------------|-----|

| Ab  | ostrac             | t                                            | iii |

| Lis | st of I            | Figures                                      | vii |

| Lis | st of <sup>-</sup> | Tables                                       | xi  |

| Ac  | rony               | ms x                                         | iii |

| 1   | Intr               | oduction                                     | 1   |

|     | 1.1                | Motivation                                   | 1   |

|     | 1.2                | Structure of this work                       | 2   |

| 2   | Арр                | lication and Qubit Fundamentals              | 3   |

|     | 2.1                | Quantum Bits                                 | 3   |

|     |                    | 2.1.1 Dirac Notation                         | 4   |

|     |                    | 2.1.2 Bloch Sphere                           | 5   |

|     |                    | 2.1.3 Quantum Computation                    | 6   |

|     | 2.2                | Quantum Gates                                | 7   |

|     |                    | 2.2.1 Fidelity for Quantum States            | 9   |

|     | 2.3                | Overview of Qubit Topologies                 | 10  |

|     |                    | 2.3.1 Trapped Ion Qubits                     | 10  |

|     |                    | 2.3.2 Superconducting Qubits                 | 11  |

|     |                    | 2.3.3 Spin Qubits                            | 12  |

|     | 2.4                | Cryogenic Electronics                        | 17  |

|     |                    | 2.4.1 Cryogenic CMOS                         | 18  |

|     |                    | 2.4.2 State of the Art                       | 21  |

| 3   |                    |                                              | 25  |

|     | 3.1                | , <u>,</u> , , , , , , , , , , , , , , , , , | 25  |

|     | 3.2                | 1                                            | 28  |

|     | 3.3                |                                              | 29  |

|     | 3.4                |                                              | 31  |

|     | 3.5                | 8 11                                         | 34  |

|     | 3.6                | Supply and Reference Voltage Noise           | 34  |

| 4   |                    | -8-F                                         | 37  |

|     | 4.1                | 8.1                                          | 38  |

|     | 4.2                | Linear Regulator                             | 42  |

| 5  | Bias   | -DAC                               | 49    |

|----|--------|------------------------------------|-------|

|    | 5.1    | Topology                           | 49    |

|    | 5.2    | Iterative Charging                 | 52    |

|    | 5.3    | Reference Voltage Coarse Tuning    | 57    |

|    | 5.4    | Digital control, timing and memory |       |

|    | 5.5    | Auxiliary Measurement Circuitry    |       |

|    |        | 5.5.1 Amplifier                    |       |

|    |        | 5.5.2 $\Sigma\Delta$ -Modulator    |       |

| 6  | Mea    | surement                           | 73    |

|    | 6.1    | Measurement Setup                  | 73    |

|    | 6.2    | Bandgap                            | 74    |

|    | 6.3    | Linear Regulator                   |       |

|    | 6.4    | OpAmp and Unity Gain Buffer        | 86    |

|    | 6.5    | $\Sigma\Delta$ Modulator           |       |

|    |        | 6.5.1 Window Comparator            |       |

|    | 6.6    | Bias-DAC                           | 94    |

| 7  | Disc   | ussion and Outlook                 | 105   |

| 8  | Sum    | mary                               | 107   |

| Bi | bliog  | raphy                              | xv    |

| Сι | irricu | lum Vitae                          | xxv   |

| Pu | blica  | tions and Conferences              | xxvii |

## **List of Figures**

| 2.1  | Quantum bit enables a superposition of the two distinct classical states            |    |  |

|------|-------------------------------------------------------------------------------------|----|--|

|      | of a conventional bit                                                               |    |  |

| 2.2  | Amplitude region for a classical logical bit [4, p. 236 Bild 4.1.a]                 |    |  |

| 2.3  | Bloch sphere [7, p. 15 Fig. 1.3.]                                                   |    |  |

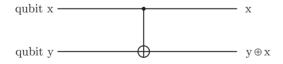

| 2.4  | CNOT notation, qubit 1 "control", qubit 2 "target" [5, p. 581 Fig. 2]               | 8  |  |

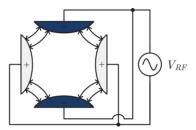

| 2.5  | RF Paul trap [29, Fig. 2a]                                                          | 11 |  |

| 2.6  | Superconducting charge qubit [30, Fig. 1]                                           | 12 |  |

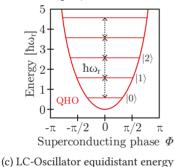

|      | a LC-Oscillator (Quantum Harmonic Oscilator , QHC)                                  | 12 |  |

|      | b Josephson qubit circuit                                                           | 12 |  |

|      | c LC-Oscillator equidistant energy level spacing.                                   | 12 |  |

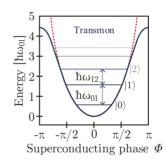

|      | d Transmon noneuqidistant energy level spacing                                      | 12 |  |

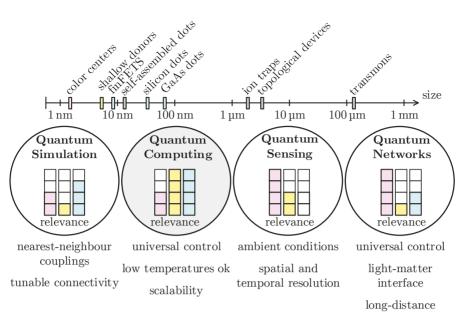

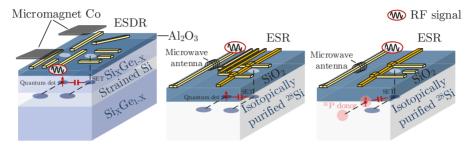

| 2.7  | Comparison of semiconductor qubits adopted from [35, Fig. 1]                        | 14 |  |

| 2.8  | GaAs structure for single qubit and read-out. Fig. adopted from [3, Fig. 2.1].      | 15 |  |

| 2.9  | S-T $_0$ qubit energy diagram and states on the Bloch sphere. Fig. adopted          |    |  |

|      | from [39, Fig. 1] and [51, Fig. 1].                                                 | 16 |  |

| 2.10 | S-T_0 qubit read-out by spin to charge conversion. $\hdots$                         | 16 |  |

| 2.11 | Si/SiGe qubit topologies. Fig. adopted from [19, Fig. 1]                            | 17 |  |

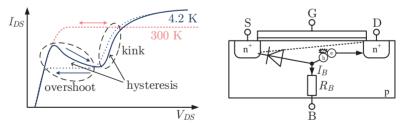

| 2.12 | Cryogenic anomalies in CMOS MOSFETs                                                 | 18 |  |

|      | a Kink, overshoot and hysteresis anomalies in 0.7 $\mu m$ CMOS. As                  |    |  |

|      | reported in and adopted from [63, Fig. 1].                                          | 18 |  |

|      | b Schematical cause of kink effekt. Adopted from [61, Fig. 11]                      | 18 |  |

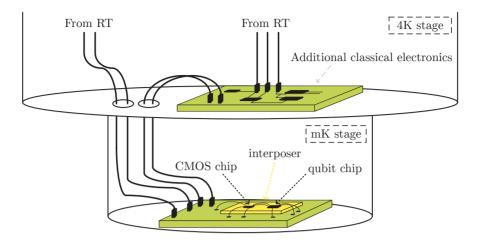

| 3.1  | Inner setup of a dilution refrigerator.                                             | 26 |  |

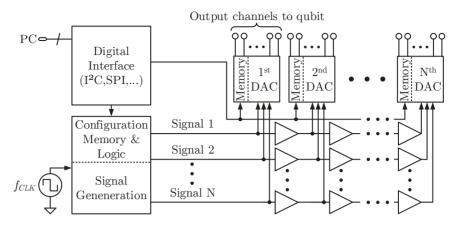

| 3.2  | Schematic setup of classical cryogenic electronics and custom CMOS chip             | 20 |  |

| 5.2  | for qubit control. Both chips are placed on an interposer and connected             |    |  |

|      | via interconnect technologies like, e.g. wire bonding.                              | 27 |  |

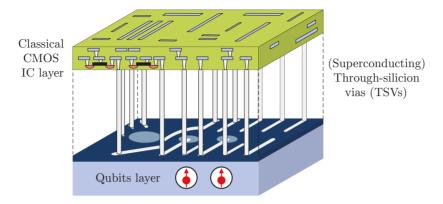

| 3.3  | Vision of classical cryogenic electronics and custom CMOS chip for qubit            | 27 |  |

| 5.5  | control building a fully scalable general purpose quantum computer                  | 28 |  |

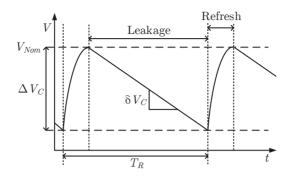

| 3.4  |                                                                                     |    |  |

| 5.1  | stored charge on a capacitor $C_S$ . This example has a leakage to $GND$            |    |  |

|      | with a slope of $\delta V_C = \frac{dV_C}{dt} = I_L/C_S$ .                          | 32 |  |

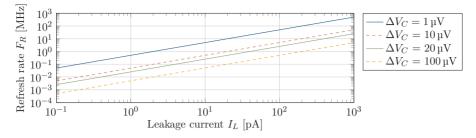

| 3.5  | Refresh rate $f_R$ required to limit the voltage ripple $\Delta V_C$ on the storage | 01 |  |

| 010  | capacitor $C_S = 2 \text{ pF}$ due to a leakage current $I_L$                       | 33 |  |

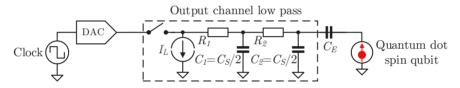

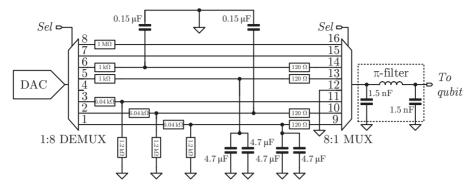

| 3.6  | Low pass filtering each output stage to suppress clock spur                         | 33 |  |

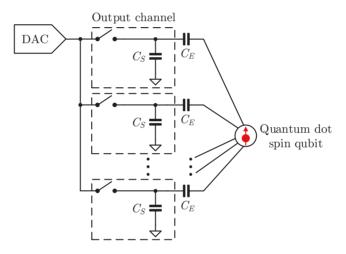

| 3.7  | A single DAC supplying multiple channels by demultiplexing.                         | 34 |  |

| 3.8  | Distribution of signals to multiple DACs and their local memory                     | 35 |  |

| 3.9  | Filtering Setup for DC lines in the RT breakbox in the qubit experiment             |    |  |

|      | setup at RWTH Aachen University, as shown in [3, Fig. A.1.]                         | 36 |  |

|      |                                                                                     |    |  |

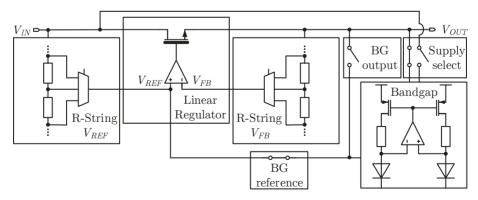

| 4.1  | Block level overview of LR and bandgap.                                             | 37 |  |

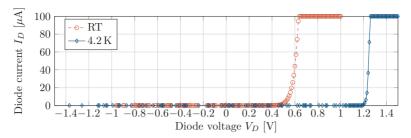

| 4.2  | Measurement of 65 nm CMOS diode in liquid helium at 4.2 K                           | 39 |  |

|      |                                                                                     |    |  |

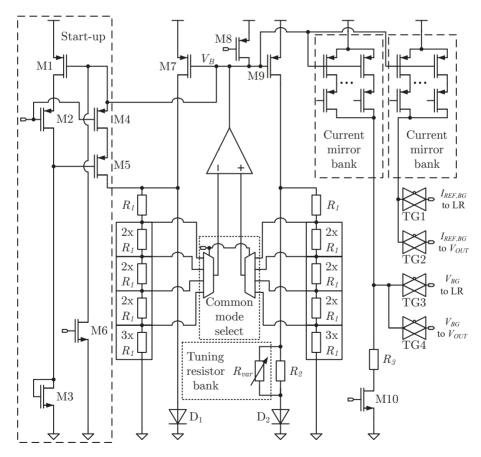

| 4.3        | Bandgap design.                                                                       | 39   |  |

|------------|---------------------------------------------------------------------------------------|------|--|

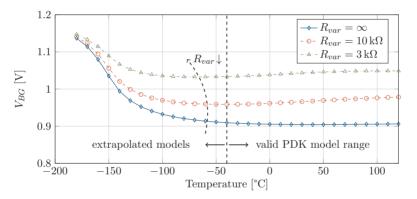

| 4.4        | Bandgap simulated reference voltage $V_{BG}$ tunable by $R_{var}$                     |      |  |

| 4.5        | Bandgap simulated with additional ideal voltage sources ( $V_{DC} = 0.6$ V) to        |      |  |

|            | model cryogenic $V_{TH,D}$ shift (ref. to Fig. 4.2). Supply voltage increased         |      |  |

|            | from 1.2 V to $V_{DD} = 1.8$ V                                                        | 41   |  |

|            | a Added $V_{DC}$ sources.                                                             | 41   |  |

|            | b Bandgap output $V_{BG}$ .                                                           |      |  |

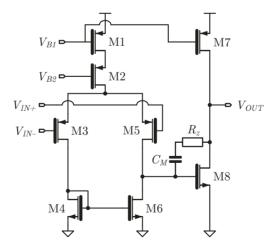

| 4.6        | Folded cascode OpAmp design.                                                          |      |  |

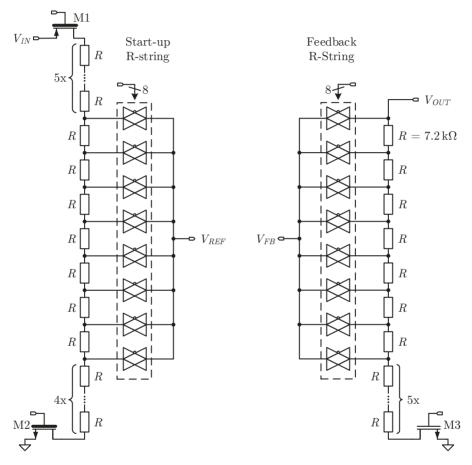

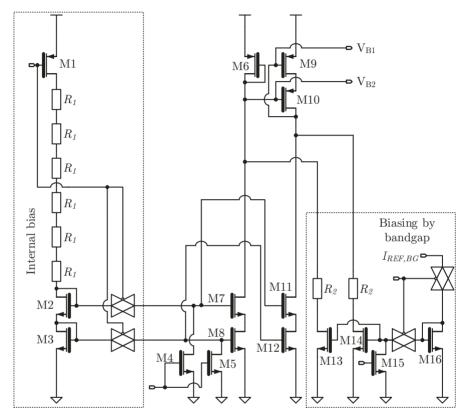

| 4.7        | Start-up reference voltage R-String and feedback R-string design                      |      |  |

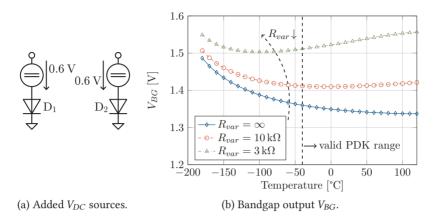

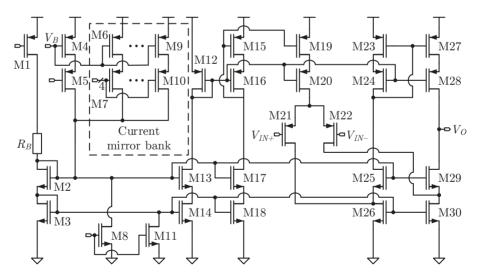

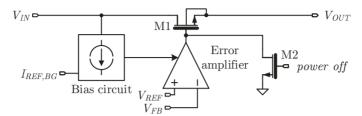

| 4.8        | Linear regulator design.                                                              |      |  |

| 4.9        | LR error amplifier design                                                             |      |  |

| 4.10       | LR error amplifier biasing network.                                                   |      |  |

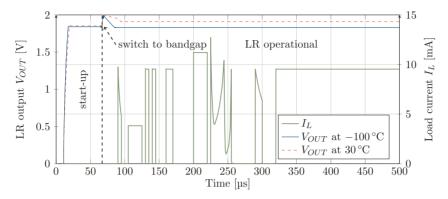

| 4.11       | LR simulated with start-up and switch to internal bandgap supplying                   |      |  |

|            | $V_{REF}$ and $I_{REF,BG}$ . Output voltage $V_{OUT}$ is stable when simulating rapid |      |  |

|            | varying load currents $I_L$ .                                                         | 46   |  |

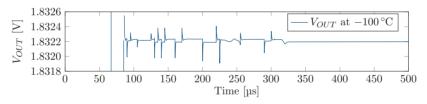

| 4.12       | Zoom-in on simulated output voltage <i>V</i> <sub>OUT</sub>                           | 46   |  |

| 4.13       | PSRR of LR simulated with operating point at the end of transient analysis,           |      |  |

|            | shown in Fig. 4.11                                                                    | 47   |  |

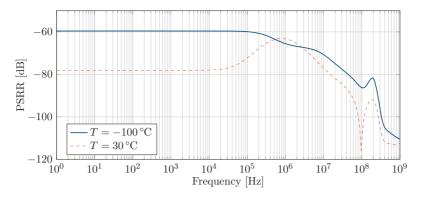

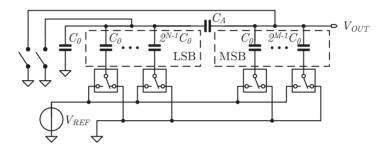

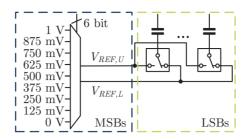

| 5.1        | Conventional charge-redistribution DAC                                                | E 1  |  |

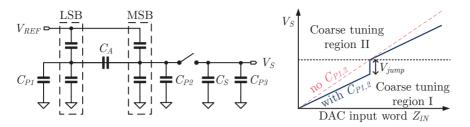

| 5.1<br>5.2 | Conventional charge-redistribution DAC                                                |      |  |

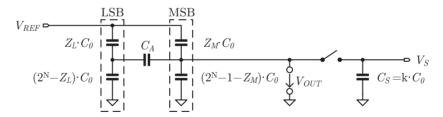

| 5.2<br>5.3 | Charge-redistribution DAC with altendation capacitor $C_A$                            | 51   |  |

| 5.5        | charging behavior.                                                                    | 52   |  |

| 5.4        | Charge-redistribution DAC schematic for MSBs part.                                    |      |  |

| 5.5        | Charge-redistribution DAC schematic for LSBs part.                                    |      |  |

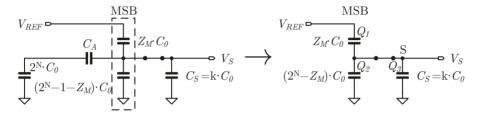

| 5.6        | Calculated effect of loading the charge-redistribution DAC with an S&H                | 54   |  |

| 5.0        | capacitor $C_s$                                                                       | 56   |  |

|            | a Iterative charging of $V_S$ .                                                       |      |  |

|            | b Voltage drop $V_{Drop,m}$ .                                                         |      |  |

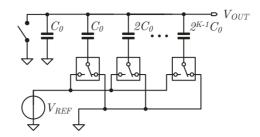

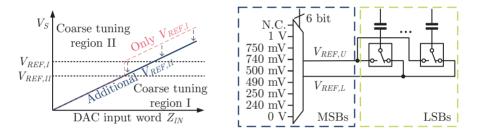

| 5.7        | Coarse tuning upper $V_{REF,U}$ and lower $V_{REF,L}$ reference voltages of the       | 50   |  |

| 5.7        | Bias-DAC.                                                                             | 58   |  |

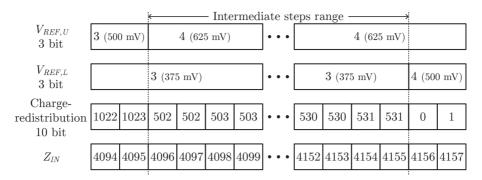

| 5.8        | DAC input word $Z_{IN}$ composition.                                                  |      |  |

| 5.9        | DAC gain error caused by parasitic capacitance $C_{P1}$ and $C_{P2}$ leading to a     | 00   |  |

| 017        | voltage jump $V_{jump}$ at crossings of coarse tuning regions                         | 59   |  |

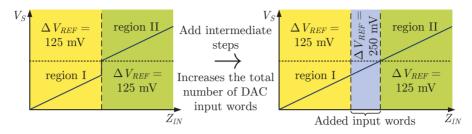

| 5.10       | Avoid voltage jump $V_{jump}$ by using two slightly shifted reference voltages        |      |  |

|            | $V_{REF,I}$ and $V_{REF,II}$ per coarse tuning crossing.                              | 59   |  |

| 5.11       | Avoid voltage jump $V_{jump}$ by adding intermediate steps between region I           |      |  |

|            | and region II                                                                         | 60   |  |

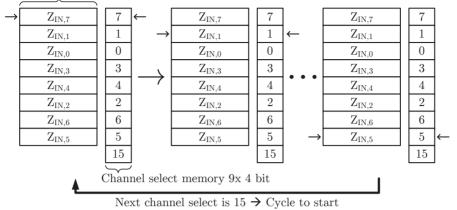

| 5.12       | Local DAC memory saving up to 8 input words $Z_{IN}$ and corresponding                |      |  |

|            | output channel. Memory is cycling if next channel select entry is 15.                 | 61   |  |

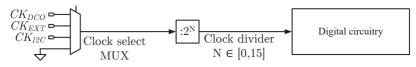

| 5.13       | Clock select MUX and clock divider.                                                   | 62   |  |

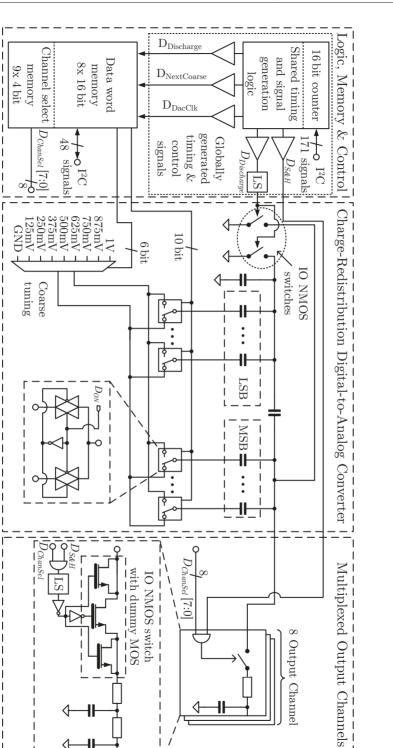

| 5.14       | Overview of implemented Bias-DAC.                                                     | 63   |  |

| 5.15       | Dublicate of the Bias-DAC connected to auxiliary measurement circuitry                | . 64 |  |

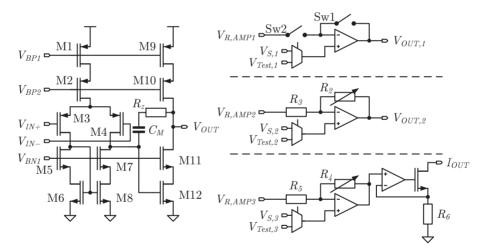

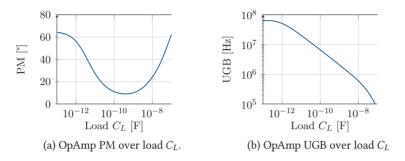

| 5.16       |                                                                                       |      |  |

| 5.17       | Simulated PM and UGB of used OpAmp in the auxiliary measurement                       |      |  |

|            | amplifier                                                                             |      |  |

|            | a OpAmp PM over load $C_L$ .                                                          | 65   |  |

|            | b OpAmp UGB over load $C_L$                                                                                                    | 65       |

|------------|--------------------------------------------------------------------------------------------------------------------------------|----------|

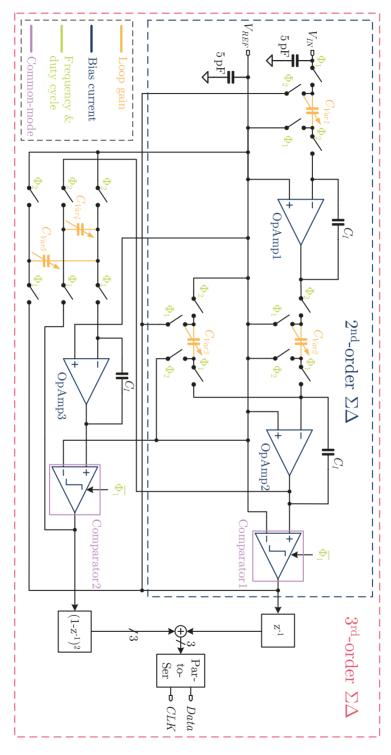

| 5.18       | Third-order 2-1 MASH $\Sigma\Delta$ modulator                                                                                  | 67       |

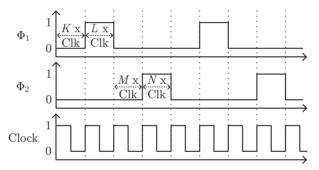

| 5.19       | Generation of two configurable non-overlapping clocks $\Phi_1$ and $\Phi_2$                                                    | 68       |

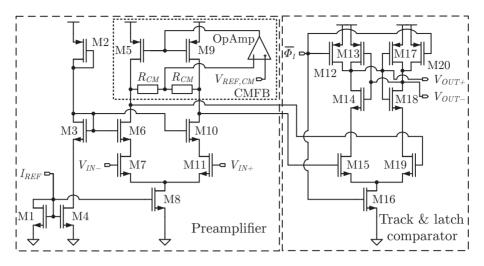

| 5.20       | Track & latch comparator with pre-amplifier.                                                                                   | 69       |

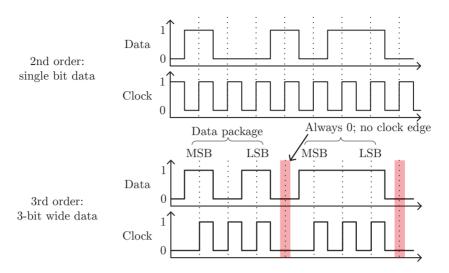

| 5.21       | Second and third-order $\Sigma\Delta$ modulator bitstream data transmission                                                    | 70       |

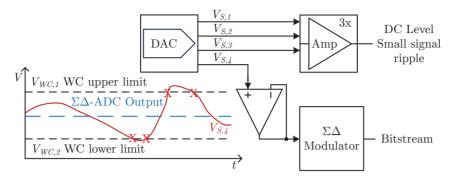

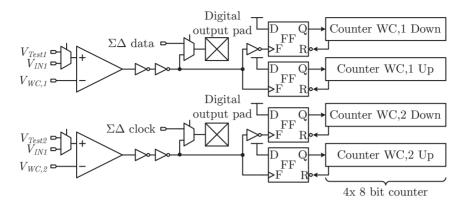

| 5.22       | Window comparator used in combination with the $\Sigma\Delta$ modulator                                                        | 71       |

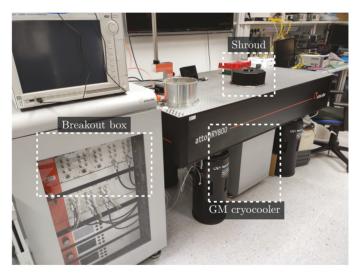

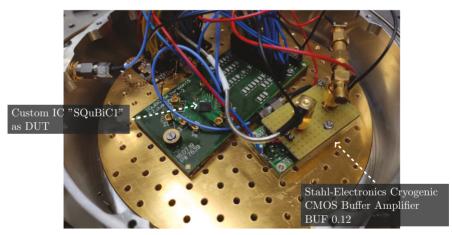

| 6.1        | Attocube attoDRY800 closed-cycle helium cryostat.                                                                              | 73       |

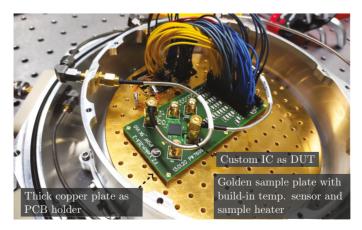

| 6.2<br>6.3 | Bandgap and LR measurement setup inside the cryostat shroud Example of bandgap being functional or failing depending on supply | 74       |

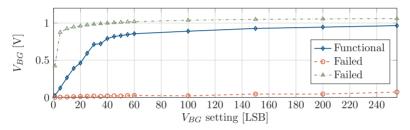

| 6.4        | voltage, bias and CM settings at 7 K                                                                                           | 75       |

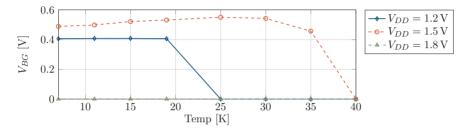

| 6.5        | is depending on $V_{DD}$ and temperature                                                                                       | 76       |

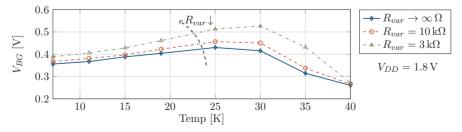

|            | bandgap current.                                                                                                               | 76       |

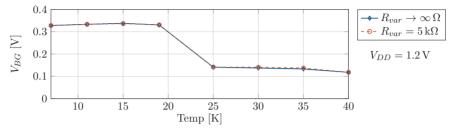

| 6.6        | Tuning $R_{var}$ with no effect for $V_{DD} = 1.2$ V                                                                           | 77       |

| 6.7        | Effect of tuning CM level on bandgap output voltage $V_{BG}$ for different                                                     |          |

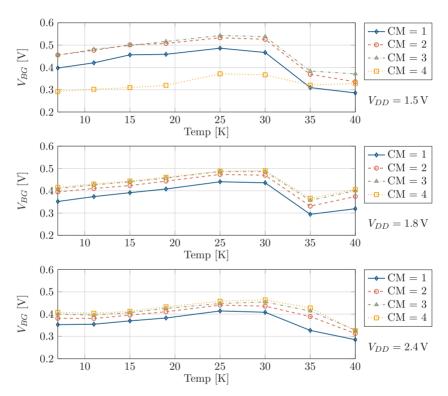

|            | supply voltages $V_{DD} = 1.5 \text{ V}$ , 1.8 V and 2.4 V                                                                     | 78       |

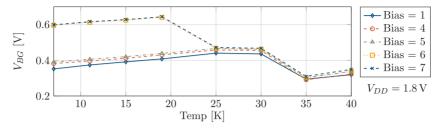

| 6.8        | Effect of tuning bias level on bandgap output voltage $V_{BG}$                                                                 | 79       |

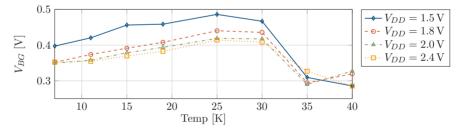

| 6.9        | Bandgap output voltage $V_{BG}$ vs. temperature for different supply voltage                                                   |          |

|            | levels.                                                                                                                        | 79       |

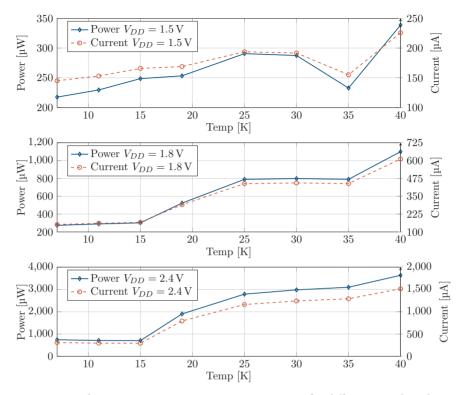

| 6.10       | Bandgap power consumption vs. temperature for different supply volt-                                                           |          |

|            | ages $V_{DD} = 1.5 \text{ V}$ , 1.8 V and 2.4 V                                                                                | 80       |

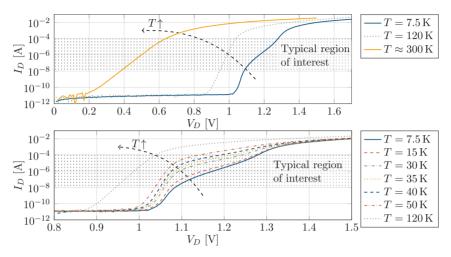

| 6.11       | Cryogenic I-V measurements of diode type used in the bandgap.                                                                  | 81       |

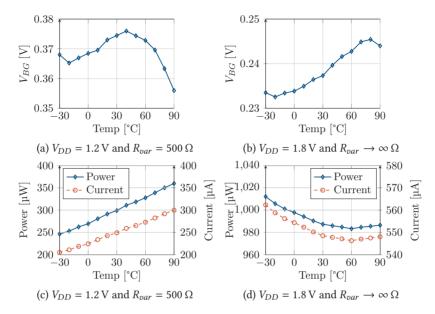

| 6.12       | Bandgap measurement results in the range from $-30$ °C to $90$ °C                                                              | 82       |

|            | a $V_{DD} = 1.2 \text{ V} \text{ and } R_{var} = 500 \Omega$                                                                   | 82       |

|            | b $V_{DD} = 1.8 \text{ V} \text{ and } R_{var} \rightarrow \infty \Omega$                                                      | 82       |

|            | c $V_{DD} = 1.2 \text{ V} \text{ and } R_{var} = 500 \Omega$                                                                   | 82       |

|            | d $V_{DD} = 1.8 \text{ V} \text{ and } R_{var} \rightarrow \infty \Omega$                                                      | 82       |

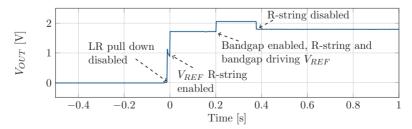

| 6.13       | LR start-up at 7 K.                                                                                                            | 83       |

| 6.14       | *                                                                                                                              | 00       |

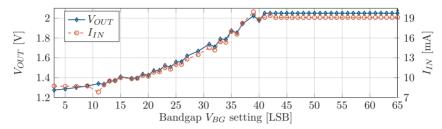

| 0111       | reference voltage $V_{BG}$ setting at 7 K                                                                                      | 84       |

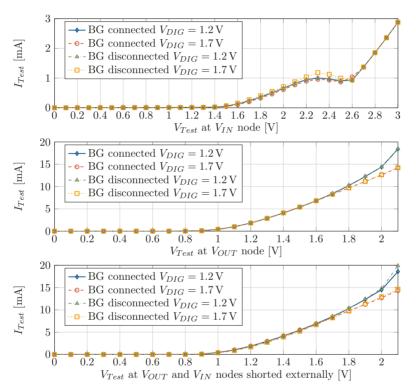

| 6.15       |                                                                                                                                | 85       |

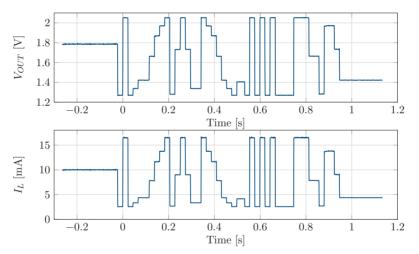

|            | LR measurement of varied load current $I_L$ and output voltage $V_{OUT}$ at 7 K.                                               | 86       |

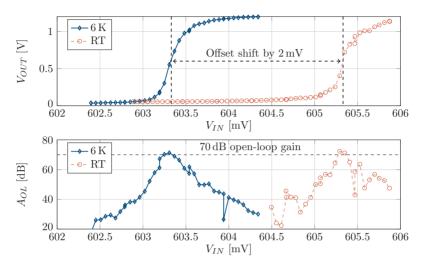

| 6.17       |                                                                                                                                | 87       |

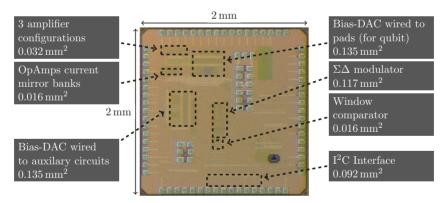

|            | Die photograph of prototype chip SQuBiC1.                                                                                      | 87       |

| 6.19       | Measurement of amplifier output voltage $V_{OUT}$ and open-loop gain $A_{OL}$                                                  | 07       |

| 0.17       | for swept input voltage $V_{IN}$ and $V_{REF} = 600 \text{ mV}$ .                                                              | 88       |

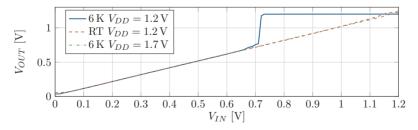

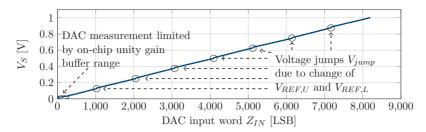

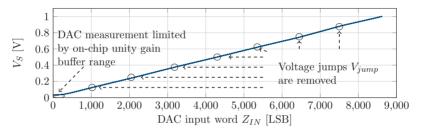

| 6.20       | Unity gain buffer output clipping to $V_{DD}$ for input CM > 0.7 V at 6 K                                                      | 88       |

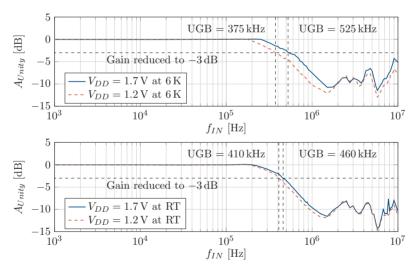

|            | UGB measured for $V_{DD} = 1.2$ V and $V_{DD} = 1.7$ V at 6 K and at RT                                                        | 89       |

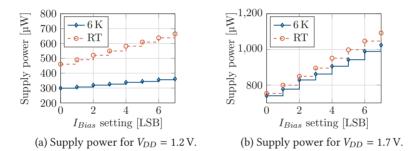

|            | Measured power consumption for the complete supply net connected to                                                            | 07       |

| 0.22       | the amplifier under test.                                                                                                      | 90       |

|            | a Supply power for $V_{DD} = 1.2$ V.                                                                                           | 90<br>90 |

|            | b Supply power for $V_{DD} = 1.2$ V.                                                                                           | 90<br>90 |

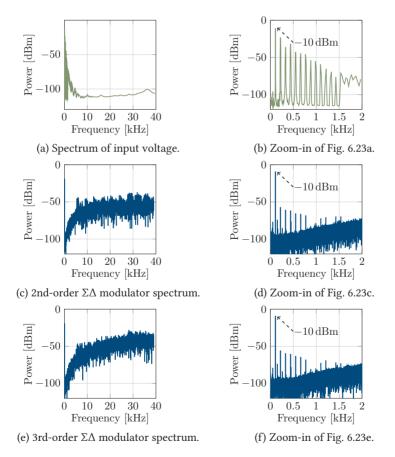

| 6.23       | Supply power for $v_{DD} = 1.7$ v                                                                                              | 90<br>91 |

| 0.45       | a Spectrum of input voltage.                                                                                                   | 91<br>91 |

|            | b Zoom-in of Fig. 6.23a.                                                                                                       | 91<br>91 |

|            | D 20011-111 01 Fig. 0.23a                                                                                                      | 71       |

|       | c 2nd-order $\Sigma\Delta$ modulator spectrum.                                                                                                                                  | 91  |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|

|       | d Zoom-in of Fig. 6.23c.                                                                                                                                                        | 91  |  |

|       | e $3rd$ -order $\Sigma\Delta$ modulator spectrum                                                                                                                                | 91  |  |

|       | f Zoom-in of Fig. 6.23e.                                                                                                                                                        | 91  |  |

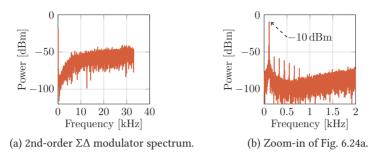

| 6.24  | Unfiltered $\Sigma\Delta$ modulator output spectrum at RT                                                                                                                       | 92  |  |

|       | a 2nd-order $\Sigma\Delta$ modulator spectrum.                                                                                                                                  | 92  |  |

|       | b Zoom-in of Fig. 6.24a.                                                                                                                                                        | 92  |  |

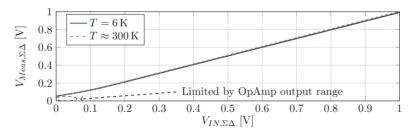

| 6.25  | DC input voltage sweep $V_{IN,\Sigma\Delta}$ measured via $\Sigma\Delta$ modulator at 6 K                                                                                       | 92  |  |

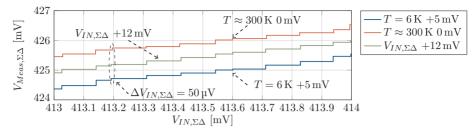

| 6.26  | Zoom-in on measurements of Fig. 6.25 at 6 K. Signals are shifted by +x                                                                                                          |     |  |

|       | mV $x \in \{0,5,12\}$ to fit inside the plot                                                                                                                                    | 93  |  |

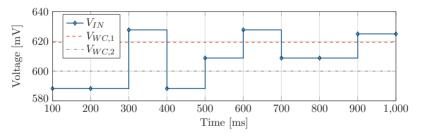

| 6.27  | Window comparator functional at 6 K.                                                                                                                                            | 93  |  |

| 6.28  | 1 ,                                                                                                                                                                             | 94  |  |

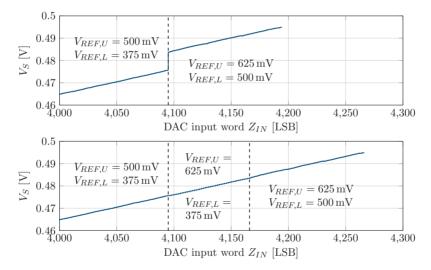

| 6.29  | 1 ,0                                                                                                                                                                            | 95  |  |

| 6.30  |                                                                                                                                                                                 |     |  |

|       | by operating the Bias-DAC with a doubled reference voltage difference                                                                                                           |     |  |

|       | $\Delta V_{REF} = 250 \text{ mV at } 6 \text{ K.} \qquad \dots \qquad $ | 95  |  |

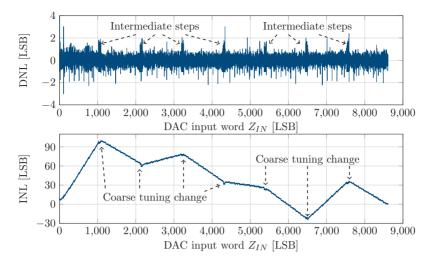

| 6.31  | 1 1                                                                                                                                                                             | 96  |  |

| 6.32  | All $V_{jump}$ occurrences removed by addition of intermediate steps between                                                                                                    |     |  |

|       | coarse tuning transitions at 6 K.                                                                                                                                               | 96  |  |

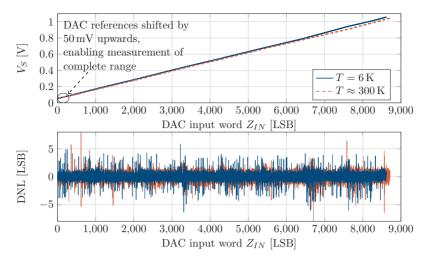

| 6.33  | Bias-DAC DNL (output via unity gain buffer) at 6 K. Legend applies to                                                                                                           |     |  |

|       | both graphs.                                                                                                                                                                    | 97  |  |

| 6.34  | 1 1                                                                                                                                                                             | 98  |  |

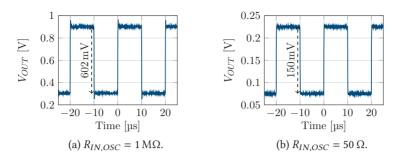

|       | a $R_{IN,OSC} = 1 \mathrm{M}\Omega$ .                                                                                                                                           |     |  |

|       | b $R_{IN,OSC} = 50 \ \Omega.$                                                                                                                                                   | 98  |  |

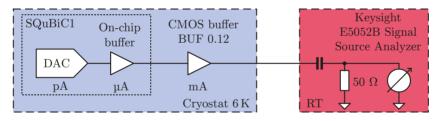

|       | Buffer chain enabling Bias-DAC measurement into 50 $\Omega$ port                                                                                                                | 98  |  |

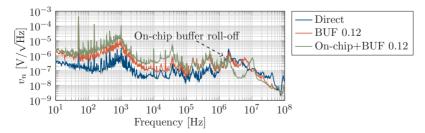

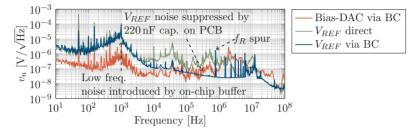

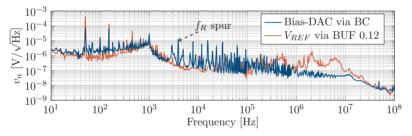

|       | Noise measurement of buffer chain at 6 K                                                                                                                                        | 98  |  |

| 6.37  | 1 JA                                                                                                                                                                            | 99  |  |

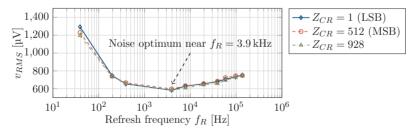

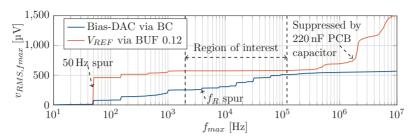

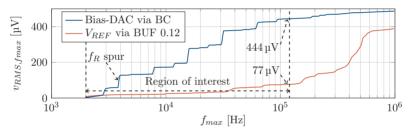

| 6.38  | Total integrated noise of whole spectrum from 10 Hz to 100 MHz depend-                                                                                                          |     |  |

|       | ing on refresh frequency $f_R$                                                                                                                                                  |     |  |

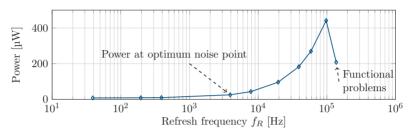

| 6.39  | Total Bias-DAC power consumption depending on refresh frequency $f_R$ .                                                                                                         | 100 |  |

| 6.40  | JR                                                                                                                                                                              |     |  |

| 6.41  | JI                                                                                                                                                                              | 101 |  |

| 6.42  | Jit Jiinii                                                                                                                                                                      |     |  |

| 6 10  | 2 kHz at 6 K.                                                                                                                                                                   | 101 |  |

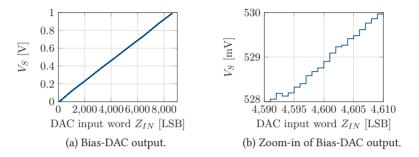

| 6.43  | Bias-DAC output voltage $V_S$ over whole range for refresh frequency                                                                                                            | 100 |  |

|       | $f_R = 3.9 \text{ kHz}$ at 6 K.                                                                                                                                                 |     |  |

|       | a Bias-DAC output.                                                                                                                                                              |     |  |

| 6 4 4 | b Zoom-in of Bias-DAC output                                                                                                                                                    |     |  |

| 6.44  | Bias-DAC DNL and INL for refresh frequency $f_R = 3.9$ kHz at 6 K                                                                                                               | 103 |  |

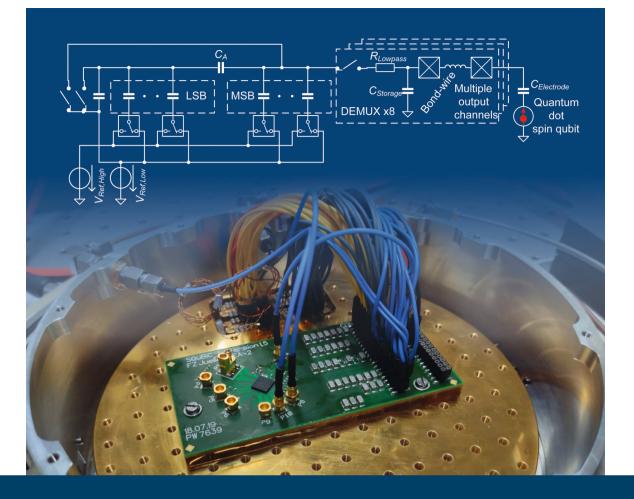

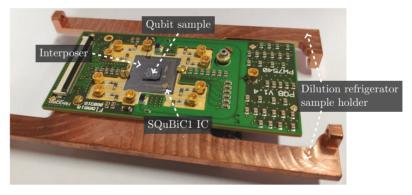

| 7.1   | SQuBiC1 mounted on interposer and wired to a qubit                                                                                                                              | 105 |  |

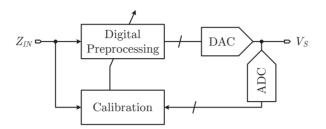

| 7.2   | Using digital assistance circuitry to improve Bias-DAC performance. $\dots$                                                                                                     |     |  |

|       |                                                                                                                                                                                 |     |  |

| 2.1 | Achievable spin qubit gate fidelities according to [40]                   | 13  |

|-----|---------------------------------------------------------------------------|-----|

| 2.2 | Comparison of cryogenic bulk CMOS characteristics at 4 K (RT)             | 20  |

| 2.3 | Comparison of 40 nm bulk CMOS characteristics at RT and 50 mK. As         |     |

|     | reported in [68, Table I]                                                 | 20  |

| 2.4 | Overview to state of the art of cryogenic IC blocks. *This work           | 22  |

| 2.5 | Overview of state of the art of cryogenic IC systems for qubits. *This    |     |

|     | work, full system yet to be characterized at targeted 100 mK              | 23  |

| 2.6 | Cryogenic CMOS circuitry: challenges and opportunities. As discussed      |     |

|     | in [83]                                                                   | 24  |

| 3.1 | Bias DAC Specification obtained from discussions with RWTH Aachen         |     |

|     | University physics department.                                            | 29  |

|     |                                                                           |     |

| 4.1 | LR R-strings voltage tuning ranges.                                       | 42  |

| 6.1 | First bandgap functionality test results.                                 | 75  |

| 6.2 | Summary of bandgap results for operation.                                 | 81  |

| 6.3 | Summary of bandgap measurement results                                    | 83  |

| 6.4 | Summary of unity gain buffer measurement results                          | 90  |

| 6.5 | Read counter values after measurement (Fig 6.27)                          | 93  |

| 6.6 | Characteristics of Stahl-Electronics Cryogenic CMOS Buffer Amplifier      |     |

|     | BUF 0.12 [126]                                                            | 97  |

| 6.7 | Bias-DAC power consumption for $f_R = 3.9$ kHz at 6 K. Adopted from [97]. | 103 |

| 6.8 | Comparison of cryogenic DACs. Adopted from [97]                           | 104 |

|     |                                                                           |     |

## Acronyms

| 2DEG  | two-dimensional electron gas     |

|-------|----------------------------------|

| ADC   | analog-to-digital converter      |

| BG    | bandgap reference                |

| CB    | conduction band                  |

| СМ    | common-mode                      |

| CMFB  | common-mode feedback             |

| DAC   | digital-to-analog converter      |

| DNL   | differential non-linearity       |

| DNP   | dynamic nuclear polarization     |

| DUT   | device under test                |

| ESDR  | electron dipole spin resonance   |

| ESR   | electron spin resonance          |

| FF    | flip-flop                        |

| GM    | Gifford-McMahon                  |

| IC    | integrated circuit               |

| ILD   | inter-layer dielectric           |

| INL   | integral non-linearity           |

| LDO   | low drop-out                     |

| LR    | linear regulator                 |

| LS    | level shifter                    |

| LVT   | low-threshold voltage            |

| MASH  | multistage noise shaping         |

| NISQ  | noisy intermediate scale quantum |

| OpAmp | operational amplifier            |

| OSR   | oversampling ratio               |

| PDK   | process design kit               |

| PM    | phase margin                     |

| PSRR  | power supply rejection-ratio     |

| PVT   | process, voltage and temperature |

| PWM   | pulse width modulation           |

| QC    | quantum computing                |

| QPC   | quantum point contact            |

| qubit | quantum bit                      |

| RT    | room temperature                 |

| s.i.  | strong inversion                 |

| SET   | single-electron transistor       |

| SSA   | signal source analyzer           |

| T&L   | track & latch                    |

| TG    | transmission gate                |

| TSV   | through-silicon-via              |

|       |                                  |

- UGB unity gain bandwidth

- **w.i.** weak inversion

- WC window comparator

## Chapter

### Introduction

#### 1.1 Motivation

Quantum computing (QC) is a research field of increasing attention and popularity, which is steadily gaining momentum in the recent years. The promises made for universal QC are vast in terms of their predicted impact on science, economy and society. The term *universal* refers to no constrains to the computational task a quantum computer should be able to solve. Multiple use cases for a universal quantum computer are already known today and one can expect more applications to be opened up in the coming years, as research on quantum algorithms is a prominent topic in this field. Most of these promises are based on a predicted speed-up compared to its classical computing equivalent. A universal quantum computer will be able to solve specific tasks up to exponentially faster than any modern supercomputer. Quantum supremacy to its classical counterpart has been published based on experimental results by F. Arute et al. [1]. 53 quantum bits completed a task in about 200 s, which would take ≈10.000 years on a modern supercomputer.

Typical examples of applications benefiting of this performance gain are: quantum chemistry in catalyst research and protein folding simulations, search algorithms for unordered databases and cryptography, e.g. prime factorization [2]. For the industrial production of ammonia, which is used as fertilizer, about 1 % of the world's energy consumption is spent, because high pressure and temperature are required in the process. QC could provide insights in process improvements by enabling quantum simulations and unveil how a biological catalyst is able to produce ammonia at ambient temperatures. [3]

However, considerable challenges have to be overcome before the first universal quantum computer can be build. Among these challenges is the sheer number of required quantum bits, that will be needed for universal QC. A publication by L.M.K. Vandersypen et al. [2] predicts about  $10^6$  to  $10^8$  required quantum bits. Quantum bits are typically operated at deep cryogenic temperatures < 100 mK inside of a dilution refrigerator. Feeding all biasing, control and read-out signals from external into the cryostat appears unpractical at best. A proposed solution is local cryogenic classical electronics, bringing control and read-out closer to the quantum bits themselves. However, an implementation for local qubit biasing is still missing.

This work is taking up the idea of using modern CMOS technologies for this task, due to their low area footprint, low power consumption and natural synergy with semiconductor quantum bits. The focus is the implementation of an integrated digital-to-analog converter (DAC) for the generation of static biasing voltages in a 65 nm CMOS technology, which is named *Bias-DAC* in this work. The biasing voltages are used to tune quantum dots for semiconductor spin-based quantum bits and are generated in close proximity at deep cryogenic temperatures of 100 mK. Taking the required number of qubits and the low cooling power budget of a dilution refrigerator, i.e.  $\approx 1 \text{ mW}$  [2], into account, the Bias-DAC design must be ultra-low power, highly scalable and able to cope with the extreme environmental conditions, e.g. an ambient temperature of 100 mK.

#### 1.2 Structure of this work

Following this introduction chapter, chapter 2 introduces QC and describes the underlying physical properties of quantum bits. Furthermore, often used terms in QC research like quantum gate fidelity and the Bloch sphere are explained. Alongside an overview to the various qubit implementation types, cryogenic CMOS effects are explained and a record of current state of the art (integrated) cryogenic electronics is presented. In chapter 3, system level considerations for power and noise are discussed and special emphasis is placed upon systematic scalable approaches in order to scale the number of Bias-DACs most efficiently. Chapter 4 presents the design of an implemented bandgap reference and linear regulator, which are investigated as building blocks for cryogenic supply and reference voltage regulation. Chapter 5 discusses the Bias-DAC design in detail and shows some additional circuitry in order to enable measurement of the Bias-DAC. Measurement results of all these circuit blocks down to cryogenic temperatures of 6 K to 7 K are presented in chapter 6. An outlook to future research activities is given in chapter 7. Chapter 8 concludes this work with a summary of the achieved results.

# Chapter **2**

## **Application and Qubit Fundamentals**

#### 2.1 Quantum Bits

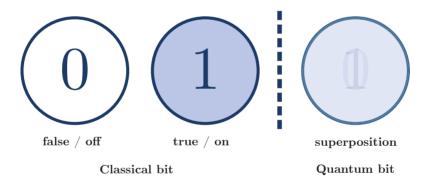

Quantum bits (qubits) are the quantum mechanical equivalent of a classical bit, which describes information in a binary numeral system. As its classical counterpart, the qubit is the basic unit of information with two distinct states. The major difference between a qubit and a classical bit is that the qubit can be in a superposition state of both basis states at the same time, i.e. "1" and "0", due to its quantum mechanical nature, which is graphically elucidated in Fig. 2.1.

Figure 2.1: Quantum bit enables a superposition of the two distinct classical states of a conventional bit

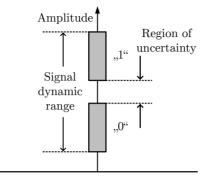

In classical computer systems, a bit is represented by a voltage level. A logical "1" is a high voltage level, and consequently a logical "0" is a low voltage level. These two logical states are normally represented by a large span of physical states, i.e. the signal voltage level, which are grouped together as one of the states. As described in [4, pp. 235-236] and shown in Fig. 2.2 the available signal range, which is 0V to 1.2V for the 65 nm CMOS technology used in this work, can be divided into 3 regions: logical high "1" state, logical low "0" state and a region of uncertainty. Every physical state grouped together in one of these regions holds the same logical level and information. This is done in order to minimize the effects of noise and distortion in the system and to maximize the noise margin of the signals [4, pp. 236-237]. This is to some extent inapplicable when encoding

a continuous superposition state in a qubit and leads to a definition of operation fidelity as a figure of merit (see section 2.2.1).

Figure 2.2: Amplitude region for a classical logical bit [4, p. 236 Bild 4.1.a]

As described above, in most cases of classical computing a bit is propagated, processed and stored by a voltage level. However, other physical representations are also realized for example a bit value can also be stored by the presence or absence of charge (on a capacitor). This storing method of a bit is employed in almost every modern computer in a DRAM. Furthermore, also magnetic flux can be used to store bits, e.g. in hard disk drives. This shows that the bit itself is just a unit of information and not bound to a fixed physical quantity. Likewise, a qubit as "an abstract, information-theoretic concept, which is best not equated with any particular physical object which may embody it" [5, p. 578], can be utilized in many quite drastically different implementation typologies (see section 2.3).

#### 2.1.1 Dirac Notation

For the mathematical descriptions of quantum states, the so-called *Dirac notation* is commonly used in quantum physics, also referred to as "bra-ket" notation. This work will give only a brief introduction and takes no aim for completeness. The following explanation is based on [6, pp. 10-12]. The notation describes vectors in a complex vector space, more precisely a complex Hilbert space. A "ket" denotes a vector in the vector space and is written as follows:

$$|V\rangle \to \begin{bmatrix} v_1 \\ v_2 \\ \vdots \\ v_n \end{bmatrix}$$

(2.1)

This ket vector can also be written as a column vector [6, p. 10], allowing for the definition of the inner product of two quantum states  $|V\rangle$  and  $|W\rangle$  as  $\langle V|W\rangle$  and this "is given by the matrix product of the transpose conjugate of the column vector representing  $|V\rangle$

with the column vector representing  $|W\rangle$ "[6, p. 11]:

$$\langle V|W\rangle = \begin{bmatrix} v_1^* & v_2^* & \cdots & v_n^* \end{bmatrix} \begin{vmatrix} w_1 \\ w_2 \\ \vdots \\ w_n \end{vmatrix}$$

(2.2)

This conversion from row to column vector is mathematically achieved by the definition of two vector spaces, the "space of kets" and the "dual space of bras". A "bra" vector  $\langle V |$  is the adjoint of the associated ket vector  $\langle V | \leftrightarrow |V \rangle^{\dagger}$ , which is then used to calculate the matrix product. This can be summarized as [6, p.12]:

$$|V\rangle \leftrightarrow \begin{vmatrix} v_1 \\ v_2 \\ \vdots \\ v_n \end{vmatrix} \leftrightarrow \begin{bmatrix} v_1^* & v_2^* & \cdots & v_n^* \end{bmatrix} \leftrightarrow \langle V|$$

(2.3)

A quantum mechanical particle is described by the corresponding wavefunction  $\psi(\vec{r}, t)$  in space  $\vec{r}$  and time *t* which can be determined by the Schrödinger equation [5, p. 67]:

$$j\hbar\frac{\partial}{\partial t}\psi(\vec{r},t) = \left[-\frac{\hbar^2}{2m}\Delta + V(\vec{r})\right]\psi(\vec{r},t)$$

(2.4)

Now the wavefunction  $|\psi\rangle$  of a qubit with its two orthogonal basis vectors  $|0\rangle$  and  $|1\rangle$  (also named micro-states [5]) can be described in Dirac notation as [5, p. 578]:

$$|\psi\rangle = c_0 |0\rangle + c_1 ||1\rangle \tag{2.5}$$

With  $c_0$  and  $c_1$  being any complex coefficients, which satisfy the condition  $|c_0|^2 + |c_1|^2 = 1$ . As described further by [5, p. 578], the squared coefficients can be interpreted as probability of the qubit being projected into one of the corresponding micro-states  $|0\rangle$  or  $|1\rangle$  when measured [5, p. 578]. The complex coefficients  $c_0$  and  $c_1$  are also referred to as "probability amplitude" [6, pp. 111, 121].

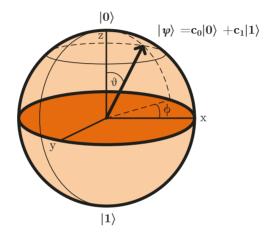

#### 2.1.2 Bloch Sphere

A common way to visualize the physical state of a single qubit is the so-called "Bloch sphere". The Bloch sphere can be derived by rewriting (2.5) under the condition that  $|c_0|^2 + |c_1|^2 = 1$ , which is leading to [7, p. 15]:

$$|\psi\rangle = e^{j\gamma}(\cos\frac{\theta}{2}|0\rangle + e^{j\phi}\sin\frac{\theta}{2}|1\rangle)$$

(2.6)

with  $\theta$ ,  $\phi$  and  $\gamma$  being real numbers. However, as [7] points out,  $e^{j\gamma}$  has no observable effects and is neglected. [5, p. 578] further adds to this point that "the common phase of  $c_0$  and  $c_1$  does not have physical significance, and can be chosen accordingly to an

arbitrary convention". Therefore, it is:

$$|\psi\rangle = \cos\frac{\theta}{2}|0\rangle + e^{j\phi}\sin\frac{\theta}{2}|1\rangle$$

(2.7)

It is then shown in [7] that the real numbers  $\theta$  and  $\phi$  define a point on the unit threedimensional sphere, see Fig. 2.3. Thus, a physical state of an ideal single qubit is somewhere on the surface of the Bloch sphere. However, there are some limitations to this geometric representation: First there is no straightforward generalization for a multiple qubit system [7], secondly the two micro-states are orthogonal basis states but are not represented as those in the Bloch sphere. Nevertheless, the Bloch sphere provides an useful way for understanding and visualization of single qubit operation.

Figure 2.3: Bloch sphere [7, p. 15 Fig. 1.3.]

#### 2.1.3 Quantum Computation

Quantum computation promises an up to exponential speedup calculation for certain tasks when compared to classical computation. This is due to two quantum mechanical effects. First, the superposition of states, which was already described in this chapter and secondly the entanglement of wavefunctions. Entanglement is required for generating one wavefunction consisting of multiple qubits and is described as: "[...] a state that cannot be written as a product of individual qubit wavefunctions. In fact, the states of individual qubits are highly correlated, possessing the type of correlation that is special to quantum systems and is referred to as 'entanglement'. Entanglement is actually a form of statistical correlation that is stronger than is possible, even in principle, in classical systems." [5, p. 579]

A classical two-bit sized word can be in 4 states: 00, 01, 10 and 11. The wavefunction of two entangled qubits can be written as [5, p. 578]:

$$|\psi\rangle = c_{00} |00\rangle + c_{01} |01\rangle + c_{10} |10\rangle + c_{11} |11\rangle$$

(2.8)

The squared complex coefficients  $c_{ik}$  can still be understood as the probability for the system to be projected into the corresponding micro-state (orthogonal basis vector). Thus, the sum of the squared coefficients has to be one [5, p. 578]:

$$\sum_{i=0}^{1} \sum_{k=0}^{1} |c_{ik}|^2 = 1$$

(2.9)

This can now be analogously expanded to an arbitrary word size of entangled qubits. The same number of qubits as classical bits are required to construct a certain word size. However, the difference between quantum mechanical and classical nature is visible when performing a mathematical operation on a qubit register. The following example is based on [5, p. 579]. Assuming a three-qubit register with  $|x\rangle$  that describes the equivalent decimal value  $x \in [0, 7]$  saved in a qubit register, e.g.  $|101\rangle \leftrightarrow |5\rangle$ . Thus, the wavefunction of the state "equal superposition of all odd values" can be written as:

$$|\psi_{odd}\rangle = \frac{1}{\sqrt{4}}(|1\rangle + |3\rangle + |5\rangle + |7\rangle) \tag{2.10}$$

Now the operation "add 3" is performed on the qubit register:

$$add3 |\psi_{odd}\rangle \Rightarrow |\psi_{odd+3}\rangle = \frac{1}{\sqrt{4}}(|4\rangle + |6\rangle + |0\rangle + |2\rangle)$$

(2.11)

This example gives a first impression of the promising advantages quantum computation is offering. By performing one instruction on a single qubit register we calculated the result of what would require 4 classical operations and registers, i.e. 1 + 3 = 4; 3 + 3 = 6; 5 + 3 = 0; 7 + 3 = 2 (integer overflow in the last two). Thus, a maximum of  $2^N$ , where *N* is the word size of the register, classical instructions can be conducted in parallel by a qubit register. Yet, when measuring/reading the qubit we will get only one result as the physical qubit state is projected onto the orthogonal basis vectors (each qubit can only be  $|1\rangle$  or  $|0\rangle$ ) and only one word is read from the qubit register. It is therefore required to develop "quantum algorithms" to utilize the possible gain one can achieve by the quantum mechanical superposition of states [5, p. 579]. However, detailed explanation to quantum algorithms is beyond the scope of this work and further information is available in [8].

#### 2.2 Quantum Gates

Quantum gates can be thought of as an analogy to the logic gates of classical computing, used to perform computation on the qubits. In classical computing only the NAND (or NOR) gate and the logical inversion are required to enable construction of every logical function. A similar approach can be taken with qubits, referred to as a universal set of quantum gates, which is one of the five requirements for the implantation of quantum computing, the so-called "DiVincenzo Criteria" with two additional requirements for quantum communication [9]:

1. A scalable physical system with well characterized qubits

2. The ability to initialize the state of the qubits to a simple fiducial state, such as  $|000\ldots\rangle$

3. Long relevant decoherence times, much longer than the gate operation time

- 4. A "universal" set of quantum gates

- 5. A qubit-specific measurement capability

- 6. The ability to interconvert stationary and flying qubits

- 7. The ability to faithfully transmit flying qubits between specified locations

Those criteria are commonly accepted as requirements for a quantum information processor or quantum communication [10].

Quantum algorithms are sequential sequences of quantum gates, which is again similar to classical logic operations. However, one major distinction of quantum gates from classical logic gates is the possibility to perform fractions of gates, e.g. when changing the phase of the qubit. Quantum gates are divided into groups representing the number of qubits involved, e.g. one-qubit gates, two-qubits gates, etc. One example for an one-qubit gate would be an inversion "NOT gate". Analogous to classical logic it should invert the physical state of the qubit. This leads to the definition of the evolution U(t) for a NOT gate: [5, p. 580]

$$U_{NOT}(c_0 |0\rangle + c_1 |1\rangle) = c_1 |0\rangle + c_0 |1\rangle$$

(2.12)

Alternatively, written as vectors and matrices:

$$U_{NOT}\begin{pmatrix} c_0\\ c_1 \end{pmatrix} = \begin{pmatrix} 0 & 1\\ 1 & 0 \end{pmatrix} \begin{pmatrix} c_0\\ c_1 \end{pmatrix} = \begin{pmatrix} c_1\\ c_0 \end{pmatrix}$$

(2.13)

A prominent example for a two-qubit gate is the "controlled NOT" or short "CNOT" which is inverting the state of qubit y depending on the state of qubit x, resulting in an logical equivalent XOR operation for qubit y and x. The notation for a CNOT gate is:

Figure 2.4: CNOT notation, qubit 1 "control", qubit 2 "target" [5, p. 581 Fig. 2]

With one and two-qubit gates, it is possible to generate a universal set of quantum gates. Furthermore, one additional characteristic of quantum computing can be noticed when looking at Fig. 2.4, i.e. qubit x is still saved after the CNOT gate was performed. This is due to the circumstance that "reversibility is required by quantum mechanics; quantum transformations are always invertible, so in a quantum computation, it must always be possible to recover the input from the knowledge of the output" [5, pp. 579-580]. This means by keeping the qubit x we can restore the input from the output by applying another CNOT on the output of qubit y:  $(y \oplus x) \oplus x = y$ .

#### 2.2.1 Fidelity for Quantum States

One important measure of the quality of a qubit is the so-called *fidelity* of quantum states, defining a way to measure distance between two quantum states [7, pp. 399-401]. This enables a method to evaluate the distance of the wanted or ideal quantum state to the measured disturbed state with errors being induced by e.g. noise. The work "Fidelity for mixed quantum states" by Richard Jozsa [11] was the first to use this term for mixed quantum states, being based on a general quantum analog of Shannon's noiseless coding theorem [12], also being called "Schuhmacher's theorem".

First, to give a brief explanation on the following terms for quantum states: *pure state* and *mixed state*. A pure state is known exactly and can be described by a single ket vector  $|\psi\rangle$ . A mixed state is a statistical distribution of different pure states described by the density operator (density matrix)  $\rho$ , e.g. for entangled multi-qubit systems.  $\rho$  is defined in eq. 2.14, with index *i*, probabilities  $p_i$  and the ensemble of pure states  $\{p_i, |\psi_i\rangle\}$ . The density operator for a pure state is  $\rho = |\psi\rangle \langle \psi|$ . Hence, mixed states include pure states and are the more general case. For a single qubit a pure state is placed on the surface of the Bloch sphere, whereas a mixed state lies within the Bloch sphere with a so-called *Bloch vector*  $||\vec{r}|| \leq 1$  for the state  $\rho$ . [7, pp. 98-105][8, p. 18]

$$\rho \equiv \sum_{i} p_{i} |\psi_{i}\rangle \langle\psi_{i}|$$

(2.14)

It was derived by [11] using the work of [13] starting from the fidelity *F* as a measure of distance of two pure states  $\psi_1$  and  $\psi_2$

$$F(|\psi_1\rangle \langle \psi_2|, |\psi_2\rangle \langle \psi_2|) = |\langle \psi_1|\psi_2\rangle|^2$$

(2.15)

that the so-called *Uhlmann–Jozsa fidelity*  $F_1$  of two mixed quantum states  $\rho_1$  and  $\rho_2$ , with tr() being the trace of the matrix, can be calculated as:

$$F_1(\rho_1, \rho_2) = \left[ tr\left(\sqrt{\sqrt{\rho_1}\rho_2\sqrt{\rho_1}}\right) \right]^2$$

(2.16)

An alternative way is to start from  $|\langle \psi_1 | \psi_2 \rangle|$  as done in [7, p. 409], resulting in a fidelity *F*'.

$$F'(\rho_1, \rho_2) = tr\left(\sqrt{\sqrt{\rho_1}\rho_2\sqrt{\rho_1}}\right) \tag{2.17}$$

This already shows that multiple fidelity definitions are possible and a recent overview is given in a 2019 publication [14]. For 2.16 a metric, based on Bures metric, can be defined for the distance, the so-called *Bures distance* [11] based on the work of [15]:

$$d_B(\rho_1, \rho_2) = \sqrt{2 - 2\sqrt{F(\rho_1, \rho_2)}}$$

(2.18)

9

and from 2.17 for the Bures angle [7, pp. 412-413][14]:

$$d_A(\rho_1, \rho_2) = \arccos\left(\sqrt{F'(\rho_1, \rho_2)}\right) \tag{2.19}$$

The fidelity of quantum gates, describing how precise the gate operations were performed and which magnitude of noise is present, is one important mean to compare different qubit implementations. The quantum threshold theorem or quantum fault-tolerance theorem as proven by [16] shows that with quantum error correction a universal quantum computer is feasible even in the presence of physical error rates. Current error-correction schemes require a fidelity of about > 99.9 % which is generally considered as required to limit the number extra physical qubits to approx. 1000 to 10000 per logical qubit [17]. Fidelity is most of the time tested with *randomized benchmarking* proposed by [18].

The fidelity of quantum gates is described by Schreiber and Bluhm [19] as: "Roughly speaking, it [the fidelity of quantum gates] specifies the success probability of a single gate operation."

#### 2.3 Overview of Qubit Topologies

As described in section 2.1 a qubit is an information-theoretic concept and thus every multi-level quantum mechanical system can be employed as a qubit, but typically only two-level systems are used. This leads to a great variety of dissimilar physical qubit implementations, ranging from trapped ions over superconducting circuits and solid-state implementations to topological qubits. Every implementation has its own distinct set of properties, advantages and disadvantages.

Whereas topological qubits could be referred to as the most exotic, due to them being *Anyons*, a quasiparticle whose statistics is neither fermionic nor bosonic [20] and exists only in two-dimensional space [21, 22]. No physically working topological qubit has been experimentally proven up to now to the best of the author's knowledge [23, 24]. Therefore, this work will not go into detailed explanation of topological qubits.

#### 2.3.1 Trapped Ion Qubits

The following section about trapped ion qubits is based on a recent review paper on "Trapped-Ion Quantum Computing: Progress and Challenges" from the Massachusetts Institute of Technology published April 2019 [10]. One way to create trapped ion qubits is to utilize RF Paul traps, which have been used since 1980 [25], to confine single ions in a high vacuum, see Fig. 2.5. The ions are trapped by applying an RF voltage  $V_{RF}$  on a set of (parabolic) electrodes. Many more different geometries are possible but they are all based on the principle of an oscillating electric field confining charged particles. Trapped ion qubits promise "robust trap lifetimes, long internal-state coherence, strong ion-ion interactions, [...]" which makes them in general one of the most robust and long-living qubits summarized in this work [10]. One concern is the scalability to millions or billions

of qubits, as this challenge might be not as straightforward as for solid-state qubits which can rely on modern semiconductor industry processes.

Gate fidelities of trapped ion qubits are reported among the top of all qubit types. For single qubit gates T. P. Harty [26] shows a fidelity of 99.9999%, which "surpass the performance of any other modality" [10], alongside long coherence times of 50 s. Two years later a paper including further research results of [27] was published, showing two-qubit logic gate operation and achieving a Bell state fidelity of 99.7% and [28] reports on 99.9(1)% two qubit gate fidelity, being "significantly above the  $\approx$  99% minimum threshold level required for fault-tolerant quantum computation".

Figure 2.5: RF Paul trap [29, Fig. 2a]

RF Paul traps are the main focus for researchers in quantum computing using trapped ions and these traps are operated with RF voltage amplitudes of 10 V to 1000 V at 10 MHz to 100 MHz [10].

#### 2.3.2 Superconducting Qubits

Another way to implement qubits is to utilize superconducting materials. Two prominent examples for superconducting qubits are the research work at IBM and Google both relying on this type of qubit, with Google recently showing the operation of 53 qubits [1]. Recent review papers for superconducting qubits are given by [30] and [31]. Superconducting qubits can be understood by looking at a basic LC-oscillator as shown in Fig. 2.6a, due to the nonexistent losses (superconducting materials) no damping is present. By using the time dependent magnetic flux present in the oscillator, [30] derived a quantum harmonic oscillator behavior for this setup with equidistant energy level spacing, i.e.  $\hbar\omega_r$ . However, this is not fitting to create a qubit as the same energy would be required for each energy level transition, rendering a distinct selection of only two specific energy levels impossible, i.e. a "leakage" to higher levels is possible.

A solution is to replace the inductance with a so-called *josephson junction* [7, 32, 33], which can be viewed as a non-linear inductance and consists of two superconducting materials separated by a thin isolating barrier, which allows for tunneling of Cooper pairs [31]. This non-linearity leads to non-equidistant energy level spacing and thus allows driving specific and distinct energy level transitions and finally selecting single energy levels for the ground  $|0\rangle$  and the excited  $|1\rangle$  state of the qubit. [30] Giaever1973

One of the challenges for this type of qubits may be scalability as superconducting qubits rely on the fact that a macroscopic structure exhibits quantum effect properties, which are normally taking effect in elementary particles and sub-nanometer sizes. Even though advantages in material properties could improve on this, today's superconducting qubits typically require a few hundred micrometer large superconducting wires, see Fig. 2.7.

Today superconducting qubits are regularly achieving single qubit gate fidelities  $\ge 0.99$  and also two qubit gate fidelities > 0.99 have been demonstrated. Superconducting qubits are a promising candidate to use in *noisy intermediate scale quantum* (NISQ) technologies and subject to ongoing research for usage in universal quantum computers. [31]

(b) Josephson qubit circuit

(a) LC-Oscillator (Quantum Harmonic Oscilator , QHC)

(d) Transmon noneuqidistant energy level spacing.

Figure 2.6: Superconducting charge qubit [30, Fig. 1]

According to Kjaergaard et al. [31] the predominant method to control single qubit operations is via microwave signals and the authors name an exemplary qubit level spacing of 5 GHz for the transmon, which is stated to be currently the most widely used type of superconducting qubit.

#### 2.3.3 Spin Qubits

level spacing.

The last discussed type of qubits in this work are spin-based qubits, referring to the use of the quantum mechanical spin to create a qubit, e.g. nuclear or electron spin. This work will focus mostly on electron spins used to encode the state of qubits. One of the major selling points of this type of qubit is the similarity to structures used in the modern semiconductor industry, managing to implement billions of MOS transistors in integrated circuit chips, whose dimensions are in the centimeter range. Therefore, semiconductor spin-based qubits are one of the promising qubit types when talking about implementation of long-term large-scale quantum circuits. [2]

Even though superconducting qubits are considered more mature today, the current trend of solid-state qubits catching up with superconducting qubits in terms of coherence time performance is shown in Fig. 2 of [34]. Whereas superconducting qubits' requirement for cryogenic temperatures is obvious due to their need to be operated below the critical temperature of their material, operating spin qubits requires a cryogenic temperature, too. Spin qubit implementations are placed in temperatures of below 100mK to reduce the thermal energy below the Zeeman energy splitting in reasonable magnetic fields. This enables an easy way to initialize qubits into the ground state by waiting for the thermal equilibrium state. Nuclear spins would require three orders of magnitude less temperature due to their about 100 times smaller magnetic momentum compared to electrons. [5, p. 591]

A comparison of semiconductor qubits alongside other types like ion traps and transmons is shown in Fig. 2.7. The size of a transmon is depicted greater than 100  $\mu$ m and the size of ion traps bigger than 1  $\mu$ m, both being considerably larger than silicon and GaAs quantum dots. FinFET based qubits are even another magnitude smaller in size. Showing the potential advantage in scaling the number of qubits in comparison. Moreover, the big relevance of semiconductor dots (Silicon, GaAs) and FinFET qubits to quantum computing is depicted below the size comparison. However, Fig. 2.7 is not evaluating the relevance of superconducting and ion qubits for these applications. In [35] the reasoning for each ranking in relevance is given. For FinFETs, silicon and GaAs dots, the major relevance in quantum computing applications, alongside superconducting qubits, is reasoned with the advanced development in "coherence, scalability and the ability to make small-scale quantum processors". The synergy of silicon based qubits and semiconductor process technologies is described as demonstration for the scalability of these qubits, being fabricated by modern semiconductor foundries.

Fidelities > 99.9 % have been reported for many types of semiconductor spin qubits, P-Donors [36], Si-MOS [37] and Si/SiGe [38]. Furthermore, also GaAs qubits are reported to show fidelities of 99.5 % [39]. Demonstrated two-qubit gates are achieving fidelities of 70 % to 90 %, which are below current state of the art two qubit fidelities of trapped ion and superconducting qubits. Increasing the fidelity to above error correction threshold is in the focus of ongoing research. The authors of [40] showed the values listed in Table 2.1 are achievable for GaAs and Si spin qubits.

|              | GaAs     | Si       |

|--------------|----------|----------|

| Single-qubit | ≥99.69 % | ≥99.95 % |

| Two-qubit    | 99.90 %  | 99.99 %  |

Table 2.1: Achievable spin qubit gate fidelities according to [40]

This work focuses on GaAs spin qubits as well as giving an outlook to integration for Si/SiGe ones. Thus, the following chapters give further details to both types of spin qubits.

Figure 2.7: Comparison of semiconductor qubits adopted from [35, Fig. 1]

#### 2.3.3.1 GaAs Qubits

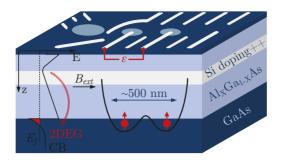

Semiconductor spin qubits were first pioneered with (Al,Ga)As quantum dots [41-43], which are in the following referred to as GaAs qubits for ease of reading. This choice was made due to some specific advantages of using these materials, i.e. larger feature sizes of the devices compared with silicon due to a smaller effective electron mass enabling easier fabrication of first research samples in order to demonstrate all key requirements for QC [44]. Additional advantages are the ability to fabricate these with high crystal quality [19] and the capability for optical coupling due to its direct bandgap nature [44]. The general structure of a GaAs quantum dot is schematically shown in Fig 2.8. A single qubit composed of two electron spins trapped in a double-well potential alongside a sensor dot for read-out of the charge state is shown. The location of these dots is highlighted on the surface. In addition, the band structure is depicted to show the two-dimensional electron gas (2DEG) in the conduction band (CB) confining the dots in the z-axis. X and y-axis of the dots are confined by applying negative voltages (referenced to ground) on the metal electrodes placed on the surface, thus locally depleting the 2DEG. Confinement in all three dimensions allows for placement of single electrons in the quantum dots. Whereas differences may be present in the hetero-structure, the overlying working principle will be the same also for Si-based qubits. The gate voltage  $\epsilon$  can be used to apply quantum gates to the qubit. An optional external magnetic field  $B_{ext}$  may be present depending on the experiment. [3, p. 7]

One not depicted effect in Fig. 2.8 is the hyperfine interaction of electron spins coupling to nuclear spins. Fluctuations in this hyperfine field are known as a possible source for decoherence [45, 46]. However, by utilizing the interaction Foletti et al. [47] showed

Figure 2.8: GaAs structure for single qubit and read-out. Fig. adopted from [3, Fig. 2.1].

a way to generate a required magnetic-field gradient between the two quantum dots through the usage of dynamic nuclear polarization (DNP). The created gradient was demonstrated for times longer than 30 min, considerably exceeding the fluctuation times. This technique was further enhanced by utilizing the qubit as feedback loop to polarize the nuclear spin bath and increased qubit dephasing times  $T_2^*$  nearly tenfold [48].

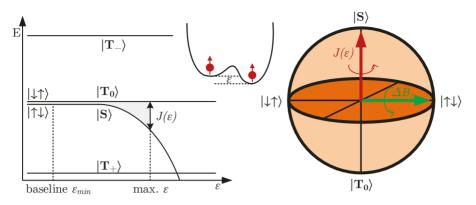

As one qubit is constructed out of two individual electron spins, various qubit encodings are possible. One method of encoding which is showing the best current gate-fidelity rates is the so-called *singlet-triplet qubit*, which also allows for sub-GHz baseband control [40]. This encoding scheme was also utilized in the work of Foletti et al. [47], which demonstrated dynamic nuclear polarization. The authors of [39, 47] denote the singlet state  $|S\rangle$  and desired triplet state  $|T_0\rangle$ , with arrows representing the direction of the electron spin, as:

$$|S\rangle = \frac{|\uparrow\downarrow\rangle - |\downarrow\uparrow\rangle}{\sqrt{2}} \tag{2.20}$$

$$|T_0\rangle = \frac{|\uparrow\downarrow\rangle + |\downarrow\uparrow\rangle}{\sqrt{2}}$$

(2.21)

and the undesirable tripled states (leakage states) as  $|T_+\rangle = |\uparrow\uparrow\rangle$  and  $|T_-\rangle = |\downarrow\downarrow\rangle$ , creating the so-called S-T<sub>0</sub> spin qubit [49].

Manipulation of the qubit is done via control of the exchange coupling  $J(\epsilon)$  between the two quantum dots, as is shown in Fig. 2.9. One reason to operate this type of qubits in cryogenic temperatures is to ensure that the "exchange interaction is the dominating energy scale compared to the electron temperature  $J(\epsilon) \gg T_e$ " [50]. Voltage pulses changing the detuning  $\epsilon$  and therefore  $J(\epsilon)$  are used to drive rotations around one axis on the Bloch sphere, whereas the second rotation around the orthogonal axis is driven by the magnetic field gradient  $\Delta B_z$ , which is generated by DNP, across the two quantum dots [39]. With these two degrees of freedom all points on the surface of the Bloch sphere can be reached.

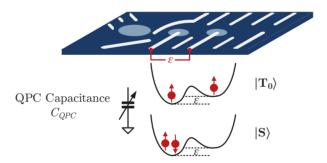

Read-out can be realized by spin to charge conversion [42]. This read-out scheme relies on the Pauli spin blockade to enable measurement of electron spins. Fig. 2.10 shows the

Figure 2.9: S-T<sub>0</sub> qubit energy diagram and states on the Bloch sphere. Fig. adopted from [39, Fig. 1] and [51, Fig. 1].

concept of changing the capacitance of the quantum point contact (QPC)  $C_{QPC}$  depending on the qubit states  $|S\rangle$  and  $|T_0\rangle$ . The electric field of either one or two electrons in the left quantum dot is influencing  $C_{QPC}$ . These variations can then be measured by RF reflectometry like done in [50] and [3]. Details of how the qubit state either allows or disallows for both electrons to move to the left QPC is given in [50].

Figure 2.10: S-T<sub>0</sub> qubit read-out by spin to charge conversion.

Concerning the requirements for DC voltages to form the potential well and tune the qubit into operation following requirements were conducted from a research cooperation with Prof. Hendrik Bluhm, who holds – together with his research group – a long track-record of (GaAs) qubit research [2, 3, 19, 39, 40, 44, 48, 50–53]. For a single GaAs qubit consisting of two quantum dots up to eight independently controllable bias voltages with an output range of –1 V to 0 V and a step size of 250 µV are required. Meanwhile, noise should be minimized as much as possible down to around a root-mean-square value of  $v_{RMS} \leq 20 \,\mu$ V. These design goals for the later discussed cryogenic integrated circuit (IC) are also summarized in Table 3.1.

#### 2.3.3.2 Si/SiGe Qubits