## Digital Signal Processing and Mixed Signal Control of Receiver Circuitry for Large-Scale Particle Detectors

Pavithra Muralidharan

Information

Band / Volume 61

ISBN 978-3-95806-489-8

Forschungszentrum Jülich GmbH Zentralinstitut für Engineering, Elektronik und Analytik (ZEA) Systeme der Elektronik (ZEA-2)

# Digital Signal Processing and Mixed Signal Control of Receiver Circuitry for Large-Scale Particle Detectors

Pavithra Muralidharan

Schriften des Forschungszentrums Jülich Reihe Information / Information

Bibliografische Information der Deutschen Nationalbibliothek. Die Deutsche Nationalbibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliografie; detaillierte Bibliografische Daten sind im Internet über http://dnb.d-nb.de abrufbar.

Herausgeber Forschungszentrum Jülich GmbH

und Vertrieb: Zentralbibliothek, Verlag

52425 Jülich

Tel.: +49 2461 61-5368 Fax: +49 2461 61-6103 zb-publikation@fz-juelich.de

www.fz-juelich.de/zb

Umschlaggestaltung: Grafische Medien, Forschungszentrum Jülich GmbH

Druck: Grafische Medien, Forschungszentrum Jülich GmbH

Copyright: Forschungszentrum Jülich 2020

Schriften des Forschungszentrums Jülich Reihe Information / Information, Band / Volume 61

D 464 (Diss. Duisburg, Univ., 2019)

ISSN 1866-1777 ISBN 978-3-95806-489-8

Vollständig frei verfügbar über das Publikationsportal des Forschungszentrums Jülich (JuSER) unter www.fz-juelich.de/zb/openaccess.

This is an Open Access publication distributed under the terms of the <u>Creative Commons Attribution License 4.0</u>, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

## **Contents**

| Lis | st of I | Figures                                          | vii  |

|-----|---------|--------------------------------------------------|------|

| Lis | st of T | Tables                                           | xii  |

| Zu  | samr    | nenfassung                                       | xiii |

| Aŀ  | strac   | t                                                | xv   |

| 1   | Intr    | oduction                                         | 1    |

|     | 1.1     | Motivation                                       | 1    |

|     | 1.2     | Structure of this work                           | 2    |

| 2   | Jian    | gmen Underground Neutrino Observatory            | 3    |

|     | 2.1     | Physics Background                               | 3    |

|     |         | 2.1.1 Neutrino Mass Hierarchy                    | 3    |

|     |         | 2.1.2 Supernova Event                            | 4    |

|     | 2.2     | Neutrino Observatory                             | 4    |

|     |         | 2.2.1 Detection Principle                        | 4    |

|     |         | 2.2.2 Energy Resolution and Key Features         | 5    |

|     |         | 2.2.3 Photomultiplier Tubes                      | 6    |

|     |         | 2.2.4 Intelligent Photomultiplier Tubes for JUNO | 7    |

|     | 2.3     | Requirements for the Electronics Readout         | 9    |

| 3   | Read    | dout Solution for JUNO                           | 11   |

|     | 3.1     | Input Stage                                      | 11   |

|     |         | 3.1.1 Transimpedance Amplifier                   | 11   |

|     |         | 3.1.2 Phase-Locked Loop                          | 13   |

|     |         | 3.1.3 Analog to Digital Converter                | 13   |

|     | 3.2     | Control Unit                                     | 15   |

|     | 3.3     | Configuration Setup                              | 15   |

| 4   | Syst    | em Model                                         | 19   |

|     | 4.1     | Top-Down Methodology                             | 19   |

|     | 4.2     | Overview of the System Model                     | 21   |

CONTENTS v

|   | 4.3   | Non-Id  | ealities in Analog Signal Processing           | 2 |

|---|-------|---------|------------------------------------------------|---|

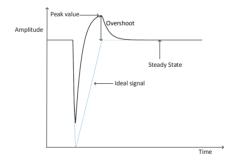

|   |       | 4.3.1   | Overshoot                                      | 3 |

|   |       | 4.3.2   | Impact of Overshoot in JUNO                    | 3 |

|   |       | 4.3.3   | Transfer Function of Combined Systems          | 5 |

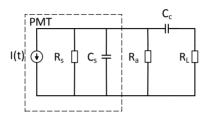

|   | 4.4   | Parasit | ic Effects of the RC Time Constant             | 5 |

|   | 4.5   | Mixed   | Signal Modeling                                | 5 |

|   | 4.6   |         | of the System in MATLAB                        | 7 |

|   | 4.7   |         | oot Compensation                               | ) |

|   | 4.8   | Residu  | al Overshoot                                   | 3 |

|   |       | 4.8.1   | Impact of Mismatches in Overshoot Compensator  | 3 |

|   |       | 4.8.2   | Mitigation Strategy                            | 3 |

|   |       | 4.8.3   | Simulation                                     | 1 |

|   | 4.9   | Baselir | ne Shift                                       | 5 |

|   |       | 4.9.1   | Effect of AC Coupling on the Baseline          | 5 |

|   |       | 4.9.2   | Effect of the RC Time Constant on the Baseline | 5 |

|   |       | 4.9.3   | Effect of High Event Rates on the Baseline     | 5 |

|   |       | 4.9.4   | Passive Baseline Restorer                      |   |

|   | 4.10  |         | ADC Baseline Regulation                        |   |

|   |       |         | ary                                            |   |

|   |       |         |                                                |   |

| 5 | Integ | gration | of The Data Processor 43                       | 3 |

|   | 5.1   | Requir  | ements                                         | 3 |

|   |       | 5.1.1   | Data Rate of Events                            | 3 |

|   |       | 5.1.2   | Supernova Event                                | 1 |

|   |       | 5.1.3   | Clock                                          | 1 |

|   | 5.2   | Data P  | rocessor                                       | 5 |

|   |       | 5.2.1   | ADC Encoder and Designator                     | 5 |

|   |       | 5.2.2   | ADC Analyzer                                   | 5 |

|   |       | 5.2.3   | Bus Mode                                       | 7 |

|   |       | 5.2.4   | Decision Process                               | 3 |

|   |       | 5.2.5   | Counters                                       | ) |

|   |       | 5.2.6   | Trigger Generator                              | L |

|   |       | 5.2.7   | Ring Buffer                                    | L |

|   | 5.3   | Heade   | r Data                                         | 3 |

|   |       | 5.3.1   | Data Transmission Format                       | 1 |

|   |       | 5.3.2   | Data Transmission Block                        | 1 |

|   | 5.4   |         | e Data Rate                                    |   |

|   | 5.5   |         | ary                                            |   |

|   |       |         |                                                |   |

| 6 | Syste | em Inte | gration of Vulcan's Digital Circuits 61        | l |

|   | 6.1   | Faults  |                                                | 2 |

|   |       | 6.1.1   | Terminology and Introduction                   | 2 |

|   |       | 6.1.2   | Fault Models                                   | 3 |

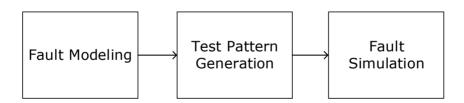

|   | 6.2   | The Te  | sting Process                                  | 1 |

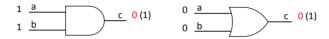

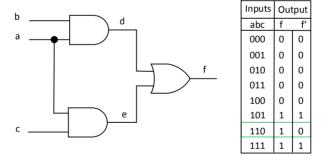

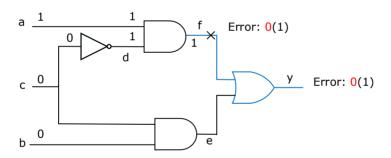

|   |       | 6.2.1   | Examples Test Pattern Generation 64            | 1 |

|   |       | 6.2.2   | Fault Propagation                              |   |

|   |       |         |                                                |   |

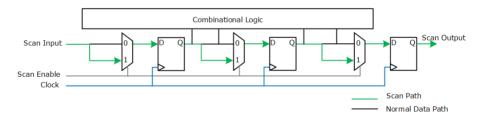

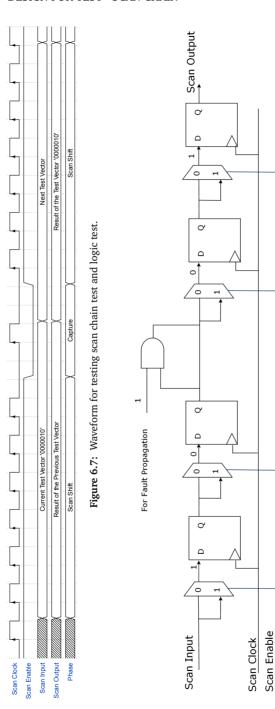

vi CONTENTS

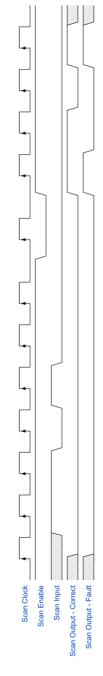

|     | 6.3<br>6.4<br>6.5<br>6.6<br>6.7 | Design for Test - Scan Chain  6.3.1 Scan Chain  6.3.2 Waveforms of Scan Chains for Stuck at Faults  6.3.3 Waveforms of Scan Chain for Transition Faults  6.3.4 Test Pattern Generation Using EDA Tool  Scan Chain Architecture in Vulcan  Scan Chain Results  Area and Timing of the Digital Control Unit  Summary | 67<br>68<br>71<br>71<br>73<br>73<br>75<br>76 |

|-----|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

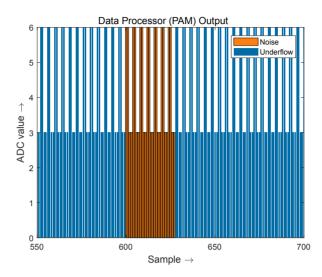

| 7   | Syste<br>7.1                    | em Validation Pre-Silicon Verification of the Data Processor                                                                                                                                                                                                                                                       | <b>77</b><br>77<br>77                        |

|     |                                 | 7.1.2 Noise Compression                                                                                                                                                                                                                                                                                            | 78<br>79                                     |

|     | 7.2                             | 7.1.4 Underflow                                                                                                                                                                                                                                                                                                    | 79<br>80<br>80                               |

|     | 7.3<br>7.4                      | 7.2.2 Configuration of Registers                                                                                                                                                                                                                                                                                   | 81<br>82<br>88                               |

| 8   | <b>Sum</b> 8.1 8.2              | Summary and Outlook Summary                                                                                                                                                                                                                                                                                        | <b>91</b><br>91<br>92                        |

| Α   | Appe                            | endix                                                                                                                                                                                                                                                                                                              | 93                                           |

| В   | Appe                            | endix                                                                                                                                                                                                                                                                                                              | 99                                           |

| Bil | oliogr                          | raphy                                                                                                                                                                                                                                                                                                              | 101                                          |

| Pu  | blicat                          | tions                                                                                                                                                                                                                                                                                                              | 105                                          |

| Gl  | ossar                           | y                                                                                                                                                                                                                                                                                                                  | 107                                          |

| Ac  | know                            | rledgments                                                                                                                                                                                                                                                                                                         | 109                                          |

## **List of Figures**

| 2.1        | Normal and inverse hierarchy of neutrino mass eigenstates [6]                                                                                                                                                                                                                                                                                                                                          | 4        |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.2        | A sketch of the Jiangmen Underground Neutrino Observatory (JUNO) detector, showing the acrylic sphere of 35.4 m diameter holding scintillation liquid of 20 kt.                                                                                                                                                                                                                                        | _        |

| 2.3        | The central detector is surrounded by 18,000 20" PMTs and ~34,000 3" PMTs [12]. The probability distribution of events for normal and inverse neutrino mass hierarchy. The y-axis indicates the probability of neutrino events. On the x-axis, L is the distance between the reactor and the point where the neutrinos are observed and E is the energy of the neutrino generated by the reactors [15] | 5<br>6   |

| 2.4        | An illustration of components inside a generic Photo Multiplier Tube (PMT). When a photon hits the photocathode, an electron is emitted by photoelectric effect. The emitted electron is multiplied at each stage of dynode by the process of secondary emission [16]                                                                                                                                  | 7        |

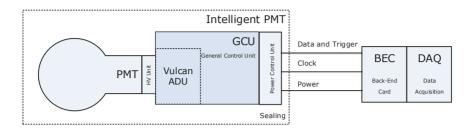

| 2.5        | Overview of the intelligent PMT for the underwater scheme for JUNO. The high voltage unit (HV), analog to digital conversion unit (ADU), general control unit (GCU) and a power control unit are potted along with the PMT and kept under water. Data is transmitted to the data acquisition unit outside the water through a                                                                          |          |

|            | 100 m cable via the back-end card                                                                                                                                                                                                                                                                                                                                                                      | 8        |

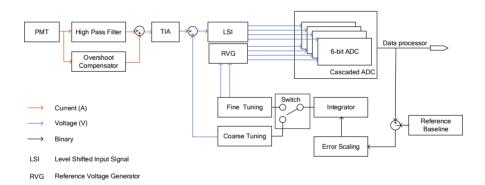

| 3.1        | Overview of the Vulcan chip architecture and the position of the Vulcan chip in the front-end electronics signal chain.                                                                                                                                                                                                                                                                                | 12       |

| 3.2        | Overview of the three signal tracks in Vulcan chip and the common control unit for the tracks.                                                                                                                                                                                                                                                                                                         | 13       |

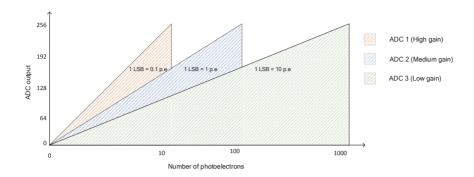

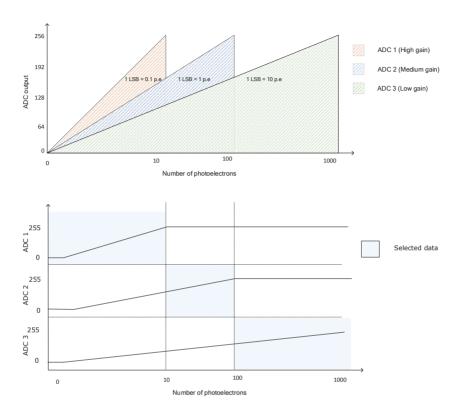

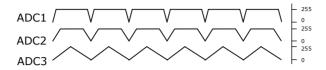

| 3.3        | Different dynamic range of the ADCs                                                                                                                                                                                                                                                                                                                                                                    | 14       |

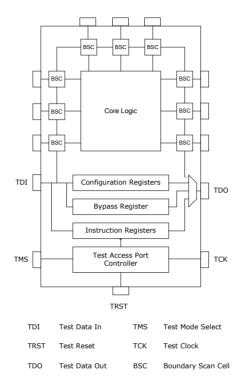

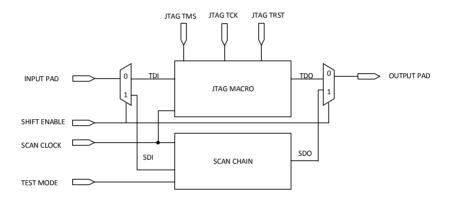

| 3.4        | Overview of the JTAG macro [21], [22]                                                                                                                                                                                                                                                                                                                                                                  | 17       |

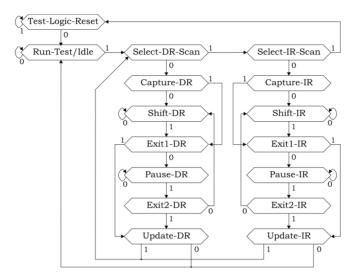

| 3.5        | State machine of the test access port (TAP) controller [22]                                                                                                                                                                                                                                                                                                                                            | 18       |

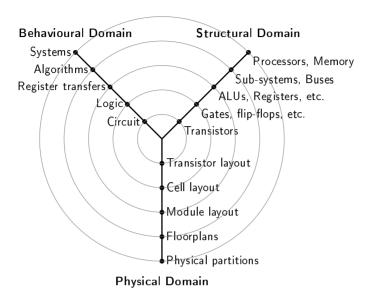

| 4.1        | Gajski-Kuhn Y-chart [25]                                                                                                                                                                                                                                                                                                                                                                               | 20       |

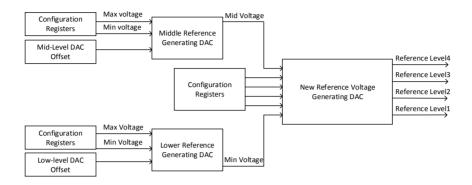

| 4.2<br>4.3 | Overview of the modeled system in Simulink                                                                                                                                                                                                                                                                                                                                                             | 21       |

| 4.4        | configuration registers                                                                                                                                                                                                                                                                                                                                                                                | 22<br>23 |

|            |                                                                                                                                                                                                                                                                                                                                                                                                        |          |

viii List of Figures

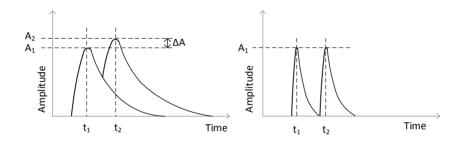

| 4.5         | The circuit equivalent of a PMT is enclosed inside the box marked with dashed lines. Along with the anode load resistance ( $R_a$ ), a decoupling capacitor ( $C_c$ ) and a load resistor or input resistance of trans-impedance amplifier ( $R_L$ ) is shown                                                                                                                             | 24 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

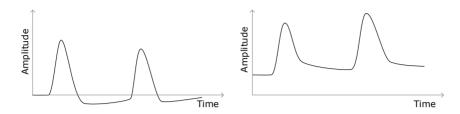

| 4.6         | [Left] Illustration of pulse pile-up on the overshoot of the signals. [Right] Illustration                                                                                                                                                                                                                                                                                                |    |

|             | of pulse pile-up on the long tail of the signal [17]                                                                                                                                                                                                                                                                                                                                      | 26 |

| 4.7         | [Left] Illustration of an increase in amplitude when two pulses pile-up. [Right] The plot illustrates the effect of reducing the time constant. The first pulse returns to the baseline before the second pulse arrives, therefore, avoiding pile-up [31]                                                                                                                                 | 26 |

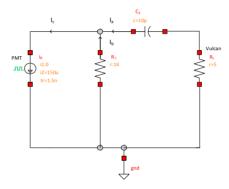

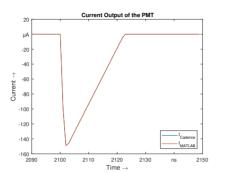

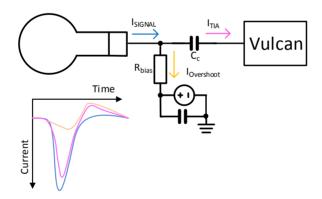

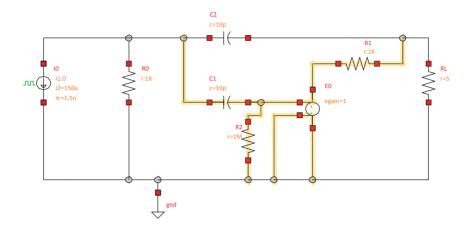

| 4.8         | The high pass filter model creating overshoot on the signal being fed to the readout circuit. Here $I_0$ =150 $\mu$ A, $t_r$ =1.5 ns, $R_0$ =1k $\Omega$ , $R_L$ =5 $\Omega$ and $C_2$ =10 pF. The current source is a pulse with an exponential decay, $R_0$ the load resistance of the anode, $C_c$ is the coupling capacitance, and the current is measured across the load resistance | 27 |

|             | $R_L$ .                                                                                                                                                                                                                                                                                                                                                                                   | 27 |

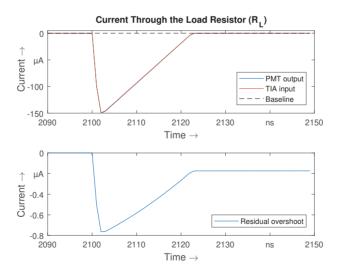

| 4.9         | A comparison of the output of the PMT [Left] and the signal at the input of the transimpedance amplifier (TIA) after passing through the high pass filter [Right].                                                                                                                                                                                                                        | 29 |

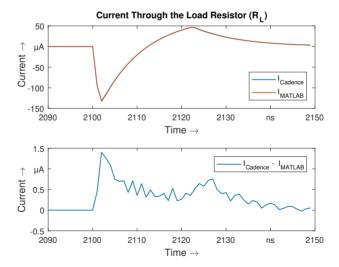

| 4.10        | The shape of the current signal after passing through the high pass filter is highly distorted and suffers an overshoot. Additionally, the MATLAB model is compared to the a computer aided design software for electronic circuit design (Cadence)                                                                                                                                       | 20 |

| 1 11        | simulation results in the upper plot with the lower one showing the residue                                                                                                                                                                                                                                                                                                               | 29 |

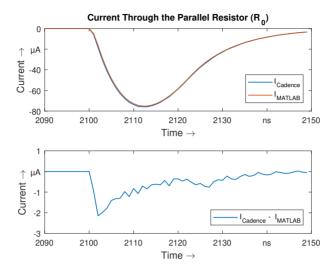

| 4.11        | Comparison of the MATLAB model and the Cadence simulation of the current flowing through the parallel resistor $R_0$                                                                                                                                                                                                                                                                      | 30 |

| <i>1</i> 19 | Illustration of the current division among the electronic components together with                                                                                                                                                                                                                                                                                                        | 30 |

| 7.12        | their corresponding waveforms on the bottom left                                                                                                                                                                                                                                                                                                                                          | 31 |

| 4.13        | Schematic of the circuit containing PMT, high pass filter, overshoot compensator and the input stage of the TIA. The components of the overshoot compensator are highlighted in orange. The parameters are set to $I_0$ =150 $\mu$ A, $t_r$ =1.5 ns, $R_0$ =1 K $\Omega$ , $R_L$ =5 $\Omega$ , $R_1$ =1 K $\Omega$ , $R_2$ =1 M $\Omega$ , $R_2$ =10 pF and $R_2$ =10 pF                  | 32 |

| 4.14        | [Top] Overlay of the overshoot compensated signal on the PMT output signal. [Bottom] Difference between the PMT output signal and the overshoot compensator output.                                                                                                                                                                                                                       | 32 |

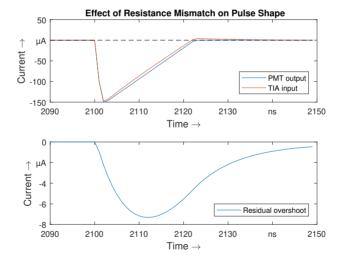

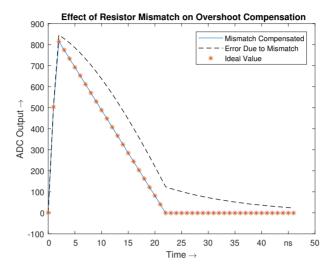

| <i>1</i> 15 | The effect of an overshoot compensator with 10% resistor mismatch.                                                                                                                                                                                                                                                                                                                        | 33 |

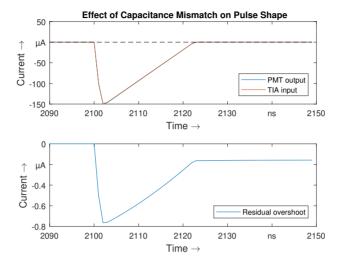

|             | The effect of an overshoot compensator with 10% capacitor mismatch                                                                                                                                                                                                                                                                                                                        | 34 |

|             | The effect of a residual overshoot compensator with 10 % capacitor inisinateri                                                                                                                                                                                                                                                                                                            | 35 |

|             | A slow baseline shift after each pulse. The baseline shift is added up for the preceding                                                                                                                                                                                                                                                                                                  | 33 |

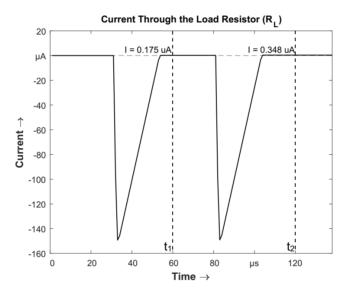

| 4.10        | pulse hence the increment in the baseline. At time $t_1$ the baseline shift of 175 nA and at time $t_2$ the baseline shift of 348 nA is measured                                                                                                                                                                                                                                          | 36 |

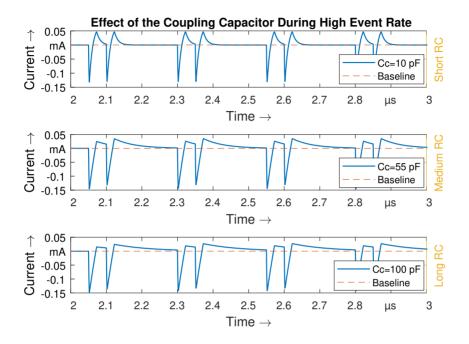

| 4.19        | The Effect of <i>RC</i> on a high event rate signal. Observing the peaks of the signal above 0 A, it can be seen that the system with smaller capacitance [Top] produces a larger overshoot but settles to 0 A faster in comparison to the signals produced by the                                                                                                                        |    |

|             | system with higher capacitance value [Bottom]                                                                                                                                                                                                                                                                                                                                             | 37 |

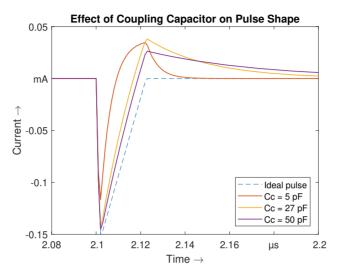

|             | The effect of the coupling capacitance $C_c$ on the pulse shape                                                                                                                                                                                                                                                                                                                           | 38 |

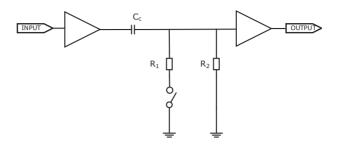

|             | The schematic of a switch-based baseline restorer [36]                                                                                                                                                                                                                                                                                                                                    | 39 |

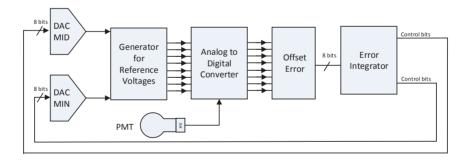

| 4.22        | ADC baseline regulator based on a sigma delta modulator [40]                                                                                                                                                                                                                                                                                                                              | 39 |

List of Figures ix

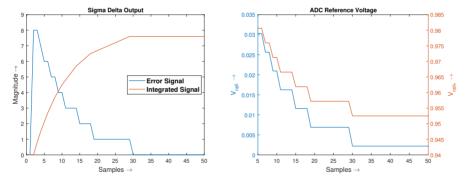

| 4.23       | [Left] Instantaneous (black) and integrated (blue) error signals of the error integrator block. [Right] Changes in the reference voltages of the ADC, blue line marks the lower voltage level adaptation and the orange line marks the higher voltage level adaptation to the regulator output                                                                                                                                                                                                        | 40  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

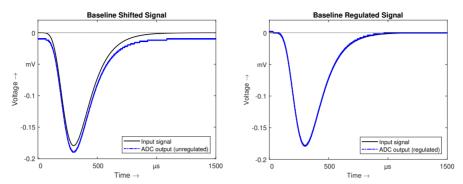

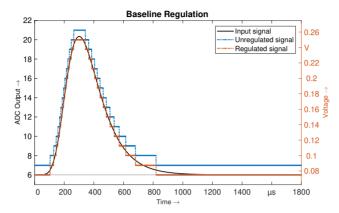

|            | [Left] Input signal (black) and unregulated ADC output signal (blue) with a baseline shift. [Right] Input signal (black) and ADC output (blue) after the baseline shift has been compensated by the baseline regulator                                                                                                                                                                                                                                                                                | 41  |

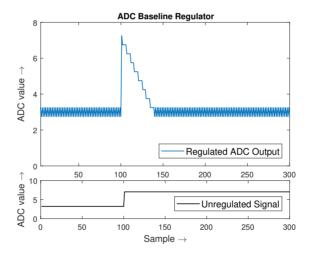

| 4.25       | The plot shows the regulation of the ADC output. The average of the regulated ADC reaches the desired baseline of 3, even after introducing an artificial error (at sample 100). The unregulated ADC output in the lower plot is presented for comparison.                                                                                                                                                                                                                                            | 41  |

| 4.26       | The offset after a pulse (blue) was measured. The offset correction was applied to the successive pulse by the regulator (orange).                                                                                                                                                                                                                                                                                                                                                                    | 42  |

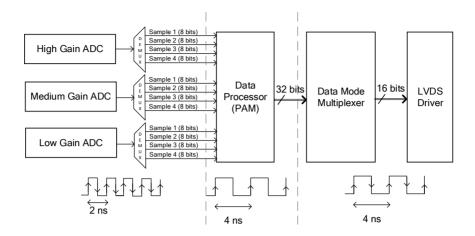

| 5.1        | Sub-modules operating at different clock frequencies are presented. Upsampling and downsampling of data to match the frequency of operation are marked in the diagram.                                                                                                                                                                                                                                                                                                                                | 45  |

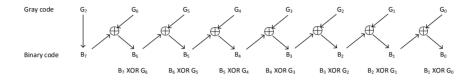

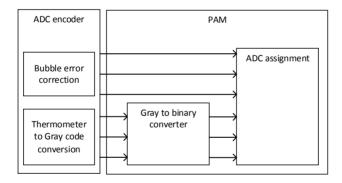

| 5.2        | Visualization of Gray to Binary conversion as used in PAM processor                                                                                                                                                                                                                                                                                                                                                                                                                                   | 46  |

| 5.3        | The ADC designator block as an entry stage for the signal entering the Programmable                                                                                                                                                                                                                                                                                                                                                                                                                   | , , |

|            | Adaptive Memory (PAM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 46  |

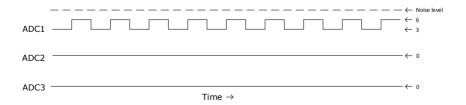

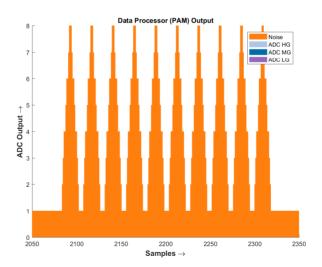

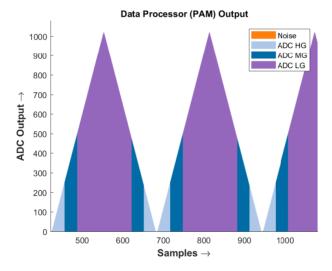

| 5.4        | Exemplary data selection by the ADC analyzer. [Top] The dynamic ranges of Analog to Digital Converters (ADCs) are shown. [Bottom] The output of the ADCs are shown for a linearly increasing ramp signal. The slope of the output signals are different owing to the ADC's gain. The highlight blue region indicates the data saved based on the selection process.                                                                                                                                   | 48  |

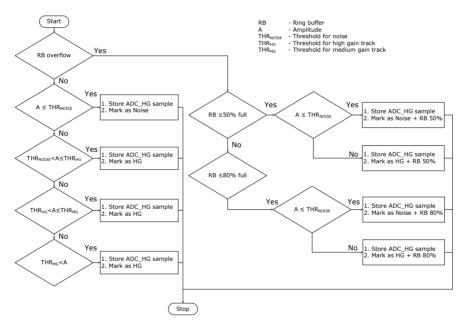

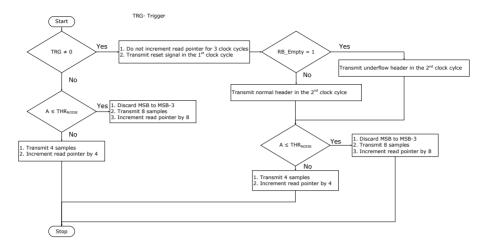

| 5.5        | Flow chart for mode selection in PAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 50  |

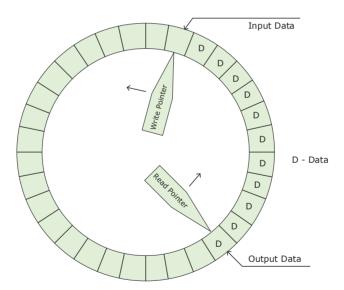

| 5.6        | Ring buffer read and write pointer wrapping around in circular fashion [42]                                                                                                                                                                                                                                                                                                                                                                                                                           | 51  |

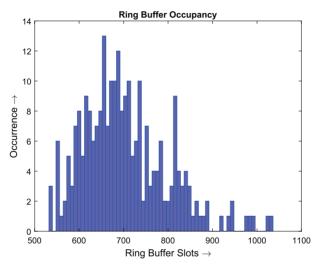

| 5.7        | A histogram of simulation showing the filling of ring buffer slots during events generating high event rates like supernova [43]                                                                                                                                                                                                                                                                                                                                                                      | 52  |

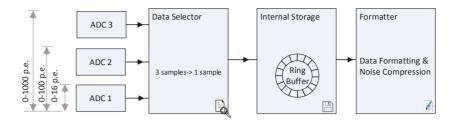

| 5.8<br>5.9 | Decision process for ring buffer full and empty flag generation [42] Overview of the programmable adaptive memory displaying the three stages of the data processor. In the first block data from one of the three ADCs are selected. In the second stage, the data is appended with the header information and stored in the ring buffer. In the final data transmission block, in addition to the generation of the reset signal and header information, compression of noise samples are performed | 53  |

| F 10       | based on the trigger information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 54  |

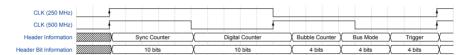

|            | Composition of the header data in PAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 54  |

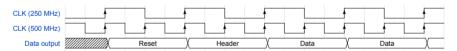

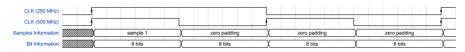

| 3.11       | output data of the Vulcan chip is transmitted with 500 MHz clock. To initiate the data transmission a reset signal is generated followed by the header information. Until a trigger occurs in the data processor, data samples are continuously transmitted                                                                                                                                                                                                                                           |     |

| E 10       | following the header                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 55  |

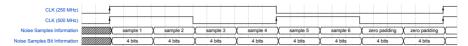

| 3.12       | samples are transmitted for every 250 MHz clock, while during noise mode the samples are compressed and 8 samples are transmitted every 4 clock cycle                                                                                                                                                                                                                                                                                                                                                 | 56  |

x List of Figures

|            | Zero padding when mode changes occur in between one of the four samples. The waveform shows the zero padding while transmitting noise data                                      | 57       |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 5.14       | Zero padding when mode changes occur in between one of the four samples. The waveform shows the zero padding while transmitting noise data                                      | 57       |

| 5.15       | Flow chart for header selection and noise compression in PAM                                                                                                                    | 58       |

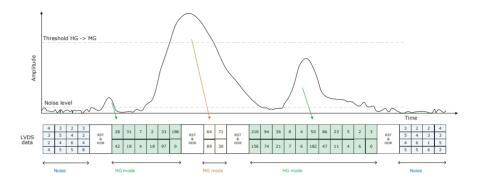

| 5.16       | Illustration of mode selection in PAM. Disclaimer: The plot and data stream are not                                                                                             |          |

|            | to scale.                                                                                                                                                                       | 59       |

| 6.1<br>6.2 | Major steps in the test process                                                                                                                                                 | 64       |

| 6.3        | Generation of stuck at 0 for the "net d" using the truth table. "f" is the correct output and "f" is the faulty output when the net d is stuck at zero (s-a-0). The test vector |          |

| <i>C</i> 1 | which produces complementary values for "f" and "f" is selected for testing                                                                                                     | 65       |

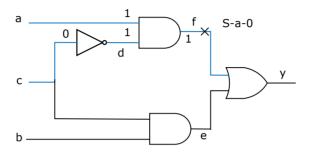

| 6.4<br>6.5 | Illustration of fault excitation in a circuit                                                                                                                                   | 66       |

|            | inputs along the path so as to propagate the effect of the fault [49]                                                                                                           | 66       |

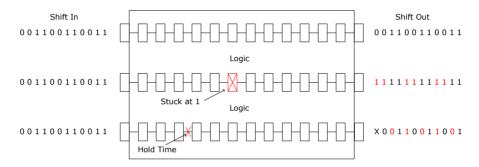

| 6.6        | Illustration of scan chain concept.                                                                                                                                             | 67       |

| 6.7        | Waveform for testing scan chain test and logic test                                                                                                                             | 69       |

| 6.8<br>6.9 | Waveform for testing transition and delay faults                                                                                                                                | 69       |

|            |                                                                                                                                                                                 | 70       |

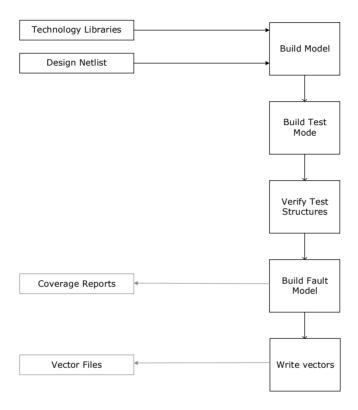

|            | Major steps in the test pattern generation using the Cadence tool chain [52]                                                                                                    | 72       |

|            | Scan chain connections                                                                                                                                                          | 73<br>75 |

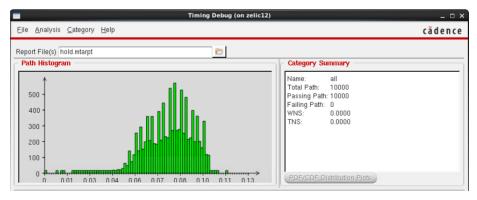

|            | Hold timing graph.                                                                                                                                                              | 75       |

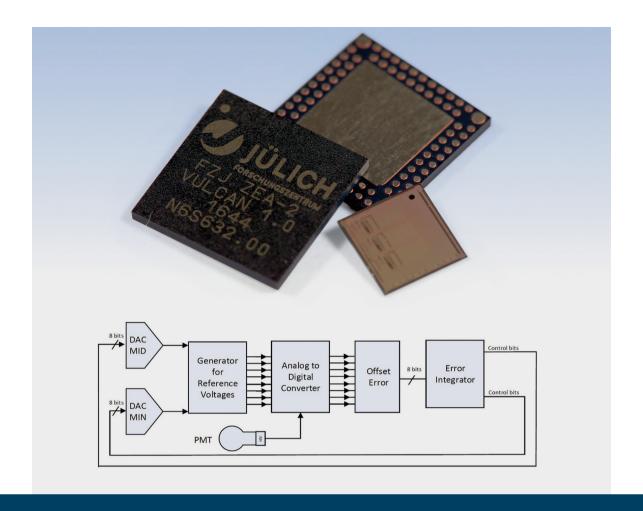

|            | [Left] Layout of the Vulcan chip sent for fabrication. [Right] Bare die and packaged                                                                                            |          |

|            | chips after fabrication.                                                                                                                                                        | 76       |

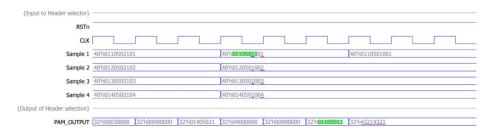

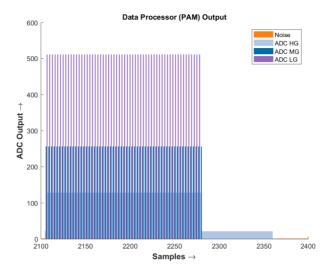

| 7.1        | A simulation result of the ADC analyzer demonstrating switching of ADC source based on the specification.                                                                       | 78       |

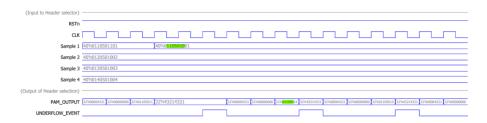

| 7.2        | Simulation results demonstrating the truncation of samples in noise mode                                                                                                        | 78       |

| 7.3        | Simulation result showing the data format change in response to the generated                                                                                                   |          |

| 7.4        | trigger signal.                                                                                                                                                                 | 79       |

| 7.4        | Simulation results demonstrating underflow event detection and the corresponding change in the output data format.                                                              | 80       |

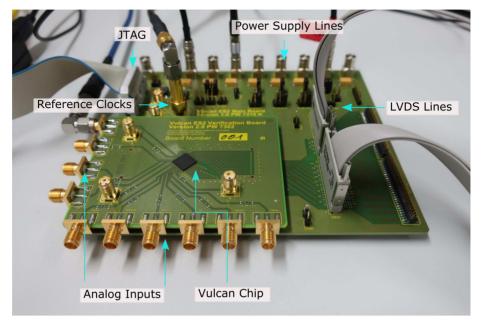

| 7.5        | Test board with the Vulcan chip embedded on it.                                                                                                                                 | 81       |

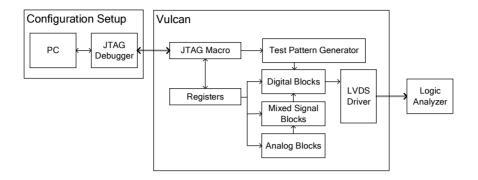

| 7.6        | Overview of the basic test setup.                                                                                                                                               | 82       |

| 7.7        | Logic analyzer output in bit stream data format with bits 0-7 shown on top and                                                                                                  |          |

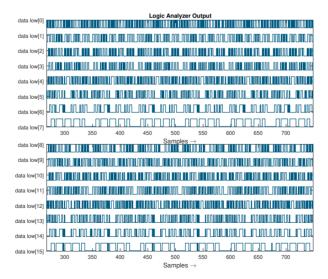

|            | 8-15 below                                                                                                                                                                      | 82       |

List of Figures xi

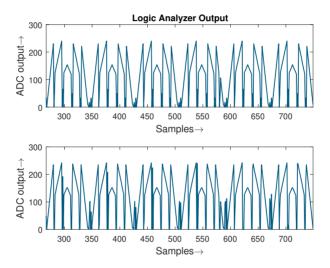

| 7.8  | Logic analyzer output of bit stream data in analog form, with inputs from Low                                                                                   |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | Voltage Differential Signaling (LVDS) bits 0-7 shown on top and 8-15 below                                                                                      | 83 |

| 7.9  | Test setup for PAM                                                                                                                                              | 84 |

| 7.10 | Waveform pattern for testing noise compression, with amplitude indicated on the                                                                                 |    |

|      | right                                                                                                                                                           | 84 |

| 7.11 | Waveform for testing noise compression and underflow                                                                                                            | 85 |

| 7.12 | Waveform for testing noise compression and underflow                                                                                                            | 85 |

| 7.13 | Waveform patterns for testing continuous mode change                                                                                                            | 86 |

| 7.14 | Reconstructed data processor output for continuous mode change input signal                                                                                     | 86 |

| 7.15 | Reconstructed data processor output for continuous mode change input signal [60].                                                                               | 87 |

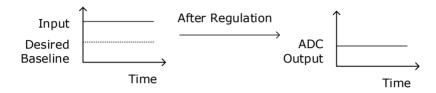

| 7.16 | Illustration demonstrating the expected behavior of ADC baseline regulator                                                                                      | 88 |

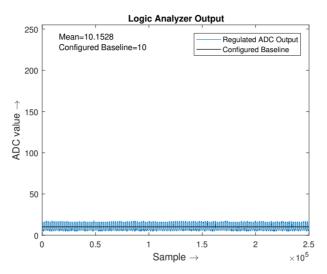

| 7.17 | ADC regulator measurement result (coarse tuning). The required baseline is set at                                                                               |    |

|      | 10 and the regulated baseline measures an average of 10.1528                                                                                                    | 89 |

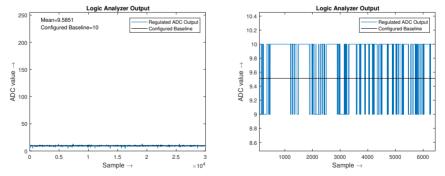

| 7.18 | [Left] ADC baseline regulation measurement result (fine tuning). The required                                                                                   |    |

|      | baseline is set at 10 and the regulated baseline measures an average of 9.5851.                                                                                 |    |

|      | [Right] ADC baseline regulation measurement result - zoomed in (fine tuning)                                                                                    | 89 |

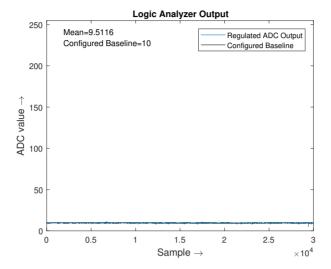

| 7.19 | Baseline retained after regulation. ADC baseline for the signal range from 0 to 255.                                                                            | 90 |

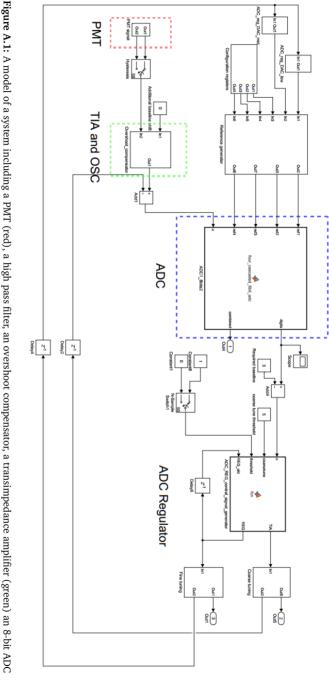

| ۸ 1  | A model of a system including a DMT (red) a high page filter on average act                                                                                     |    |

| A.1  | A model of a system including a PMT (red), a high pass filter, an overshoot compensator, a transimpedance amplifier (green) an 8-bit ADC (blue), and a baseline |    |

|      |                                                                                                                                                                 | 94 |

| ۸. ۵ | regulator                                                                                                                                                       |    |

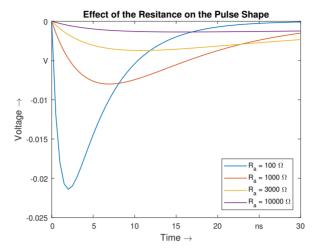

| A.2  | The effect of the resistance $R_a$ on the pulse shape.                                                                                                          | 95 |

| A.3  | Overview of the intelligent PMT for the underwater scheme for JUNO                                                                                              | 96 |

## **List of Tables**

| 3.1 | Range and precision of the ADCs in the Vulcan chip                                                                                                                    | 14  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.1 | Bus mode description and its corresponding code                                                                                                                       | 54  |

| 5.2 | Combinational bus mode description and their corresponding codes                                                                                                      | 55  |

| 5.3 | Trigger description and their corresponding codes                                                                                                                     | 55  |

| 5.4 | Combinational trigger description and their corresponding codes                                                                                                       | 56  |

| 6.1 | A reference table for fault type recognition. Error bits are color coded in red [55].                                                                                 | 70  |

| 6.2 | Synthesis result of the scan chain insertion in the digital design                                                                                                    | 74  |

| 6.3 | Test coverage of the scan chain reported by the Automatic test pattern generator tool. Here, TCov is the total coverage and ATCov is the adjusted test coverage which |     |

|     | is calculated by excluding the redundant faults                                                                                                                       | 74  |

| 6.4 | Simulation result of the scan chain with test pattern generated by the ATPG tool .                                                                                    | 74  |

| 6.5 | Area table for comparison of area the ring buffer consumes                                                                                                            | 76  |

| B.1 | Description of pads used by the digital circuits                                                                                                                      | 100 |

## Zusammenfassung

Das Jiangmen Underground Neutrino Observatory (JUNO) ist ein Vielzweckexperiment basierend auf einem 20 000 Tonnen Flüssigszintillator dessen Hauptziel die Bestimmung der Neutrino-Massenhierarchy ist. Die Signalerkennung wird durch Photonenvervielfacher (PMT) und integrierten Ausleseschaltkreisen durchgeführt. Die zentrale Komponente für den Digitalisierungsprozess ist ein Empfänger-Chip mit einem stromsparenden Analog-zu-Digital-Wandler System-on-Chip (SoC) mit einem großen Dynamikbereich. Um diesen großen Dynamikbereich effizient verarbeiten zu können sind ein Datenprozessor und ein Regelkreis im Chip integriert. In dieser Dissertation wird das Design, die Entwicklung und die Prototypenmessungen des Datenprozessors sowie des Regelkreises beschrieben, die in dem SoC integriert sind. Der Prozessor analysiert die Daten und führt eine Datenreduktion durch, um die verfügbare Ausgangsbandbreite effizient zu nutzen. Basierend auf den System- und Ereignisinformationen, die durch den Prozessor zusammen mit den Daten übertragen werden, wurde die Signalrekonstruktion erfolgreich durchgeführt. Die Regelschleife reduziert das Rauschniveau und erhöht damit die effektive Anzahl der Bits, die für die Auflösung des Signals zur Verfügung stehen. Durch die Komplexität der PMT-Integration ist ein Austausch von fehlerhaften Komponenten während der Experimentlaufzeit schwierig. Daher ist eine Design-for-Test-Struktur in den Empfängerchip integriert, mit der Intention nur fehlerfreie Exemplare nach der Massenproduktion zu erhalten. Durch das Einführen von Teststrukturen in das Design wurde die generelle Testabdeckung erfolgreich erhöht. Abschließend werden die Erkenntnisse des entwickelten Modells der Empfangskette präsentiert.

### **Abstract**

The Jiangmen Underground Neutrino Observatory (JUNO) is a multi-purpose underground experiment based on a 20,000 ton liquid scintillator with the primary objective of determining the neutrino mass hierarchy. The signal detection is performed by photomultipliers PMT and integrated readout electronics. The central component for the digitization process is a receiver chip with a low power analog to digital conversion unit of large dynamic range. In order to efficiently utilize the conversion unit's dynamic range, a custom data processor and a regulation circuit were included in the chip. In this thesis, the design, development and prototype measurements of the data processing unit and a regulation circuit included in the analog to digital conversion unit are presented. The processor analyzes the data and performs data reduction resulting in efficient utilization of output bandwidth. Based on the system and event information transmitted by the processor along with the data, successful signal reconstruction was carried out. The regulation circuit reduces the noise level thereby increasing the effective number of bits available for the signal. The complexity of the PMT installation poses difficulty to replace faulty electronics during runtime of the experiment. A design for test structure included in the receiver chip with the intention to extract defect free electronics during testing of the mass-produced chips is also described. The introduction of test structures in the design successfully increased the overall test coverage. Finally, the insights from the developed model of the receiver chain are presented.

Introduction

#### 1.1 Motivation

In recent years the demand for precise signal extraction in high energy physics experiments is dramatically increasing. Generally, in physics experiments sub-atomic particles are studied by observing their interactions and measuring the by-products like gamma rays which lie in the high-frequency range of the electromagnetic spectrum (above 10<sup>18</sup>Hz). These high energy and high-frequency signals require different processing techniques in comparison to the commonly used radio wayes.

Among the various sub-atomic particles in the standard model, characteristics of neutrinos such as neutral electric charge and low mass lead to low interaction rates further complicating their detection and measurement [1]. Dedicated experiments have been constructed to study the properties of neutrinos. Although several traits of neutrinos have been understood by the previous experiments, features like the mass hierarchy of neutrinos, flavor transformations, mixing angles, etc. are yet to be understood. A new generation of experiments has been developed to understand these open questions by constructing detectors with high accuracy in the spectrum of interest handed over from the previous experiments.

Jiangmen Underground Neutrino Observatory (JUNO) is an upcoming neutrino detector experiment aiming for high precision measurement to determine the neutrino mass hierarchy. For increasing detection efficiency and accuracy in a narrow bandwidth of the energy spectrum, a highly configurable System-on-Chip (SoC) solution (Vulcan) was developed to readout the signals from the PMT used for detection.

In order to improve the signal integrity and reduce signal loss during transmission, a new intelligent PMT concept was developed with Vulcan in which the readout electronics is placed in proximity to the PMT and enclosed in a casing along with other supporting electronics and kept underwater. The Vulcan readout chip is currently customized for this specific concept. The readout electronics has been designed to meet the specific requirements of the neutrino detector.

Among the various sub-modules of the Vulcan readout chip, architecture, implementation, measurements of the main data processing unit and a baseline regulator are presented in this

thesis. A model of the front-end electronics generating overshoot and a model of the developed overshoot compensator is also presented. Besides the developed model, a new regulation technique to preserve the pulse shape of the signal is proposed.

Due to the complexity of the PMT installation, tight reliability requirements were set on the readout electronics. In order to comply with the reliability requirements, a Design for Test (DFT) feature is included in the receiver chip. The methodology, development, implementation, and verification of the design for test structure is included in this thesis.

#### 1.2 Structure of this work

The scope of this thesis is divided into three major parts:

- Modeling and analysis of overshoot effects and baseline shift on the pulse in the mixed signal domain.

- 2. Development of a main data processing unit and a baseline regulator in the digital domain.

- 3. Inclusion of a design for test structure the scan chain.

Chapter 2 provides a brief description of the JUNO experiment and is followed by a short summary of the chain of events starting from neutrino interactions until the generation of the current signal by the PMT. The requirements for the readout electronics derived from the requirements of the experiment are also summarized.

In chapter 3, the architecture of the Vulcan chip and sub-components are briefly described as a primer to understand the baseline regulator, the main data processing unit, the proposed residual overshoot compensator and other topics described in this thesis.

In chapter 4, the system model developed to analyze the effect of overshoot and the developed overshoot compensation are presented. This is followed by the baseline regulator model, implementation and simulation results.

Chapter 5 provides an overview of the parallel signal chain in the Vulcan readout chip. A detailed description of the sub-modules of the main data processing unit of the Vulcan chip along with its simulation results are presented.

Chapter 6 describes the necessity to introduce a design for test structure in the complex integrated circuit. A design for test structure scan chain was included to increase the test points in the design and thereby improving the testability for designs in sub-micrometer technology. Along with the design for test feature, the sub-modules surrounding the data processor that facilitate in successful chip configuration are discussed.

In chapter 7, the verification and measurement of results of the data processor and the baseline regulator from two Vulcan design step prototypes are presented. A description of the measurement setup is also included.

Chapter 8 concludes this thesis with a brief summary of the model, design and development of the blocks presented in the previous chapters.

## Jiangmen Underground Neutrino Observatory

2

The Jiangmen Underground Neutrino Observatory (JUNO) is a neutrino detection experiment under construction in Jiangmen, China, based on a liquid scintillator. The experiment's main goal is to determine the neutrino mass hierarchy by detecting reactor anti-neutrinos from the Yangjiang and Taishan nuclear power plants [2]. The measurement of signal in JUNO is expected to begin from the year 2022.

Among various unapprehended topics, the JUNO experiment aims to investigate the neutrino mass hierarchy, mixing parameters of neutrino oscillations and measurements of neutrino bursts from the next nearby supernova [3]. By precise measurements of reactor anti-neutrino oscillations and by measuring interactions from other neutrino sources (solar neutrinos, atmospheric neutrinos, geo-neutrinos, nucleon decay) the experiment is aiming to resolve the unknowns mentioned above. A brief description of the physics behind the JUNO experiment and the constraints that led to the specification of the Vulcan chip are described in the sections below.

#### 2.1 Physics Background

Neutrinos belong to the lepton group in the standard model of particle physics. Leptons are further classified into electrically charged and neutral leptons. For every charged lepton (electron (e), mu ( $\mu$ ), tau ( $\tau$ )) there is a corresponding neutral lepton called neutrino (electron neutrino ( $\nu_e$ ), mu neutrino ( $\nu_\mu$ ), tau neutrino ( $\nu_\tau$ )). Since neutrinos are electrically neutral and leptons, therefore, they neither undergo electromagnetic nor strong interactions. Sub-atomic particles are observed by their interaction with other particles. The only relevant remaining force is a weak interaction, therefore they rarely interact with other particles or among themselves, hence they are hard to observe [1].

#### 2.1.1 Neutrino Mass Hierarchy

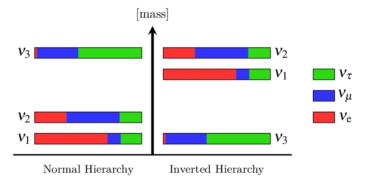

Neutrinos have flavor eigenstates ( $\nu_e$ ,  $\nu_\mu$ ,  $\nu_\tau$ ) and mass eigenstates ( $\nu_1$ ,  $\nu_2$ ,  $\nu_3$ ). The complete mass hierarchy of the neutrino eigenstates have not been determined. Results from the previous neutrino experiments [4] have concluded the mass of  $\nu_2 > \nu_1$ , while the mass hierarchy of  $\nu_3$

in comparison to  $v_1$  and  $v_2$  is still unknown [5]. This results in two possible scenarios with a normal and an inverted mass hierarchy. The normal and inverted hierarchy shown in the Figure 2.1 demonstrates the two possible mass hierarchy of the neutrino mass eigenstates which is targeted to be determined by JUNO. In normal hierarchy, the mass eigen state  $v_3$  will be higher than  $v_2$  and  $v_1$ , while in inverted hierarchy the mass eigen state  $v_3$  will be less than  $v_2$  and  $v_1$ .

Figure 2.1: Normal and inverse hierarchy of neutrino mass eigenstates [6].

#### 2.1.2 Supernova Event

"Supernovae are violent explosions of stars in our universe producing very high luminosity. Supernovae can be one of the largest explosion that can occur in our universe" [7], [8]. During a supernova, high energy radiations are expected to occur. A supernova radiates almost all of its binding energy in the form of neutrinos, most of which have energies in the range 10-30 MeV [8]. These neutrinos come in all flavors and are emitted over a timescale of several tens of seconds" [9], [10]. In the event of a supernova, the data rate in a neutrino sensitive detector will increase tremendously. In JUNO, the electronics is required to handle such high data rates on a supernova event [3], [11].

#### 2.2 Neutrino Observatory

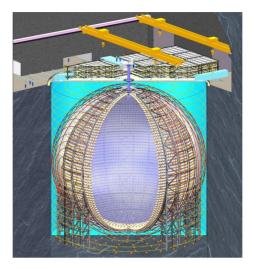

The central detector of JUNO is a liquid scintillator with a mass of roughly 20,000 tons and is situated with 700 meters rock overburden as shown in Figure 2.2. It is surrounded by 18,000 20-inch photomultipliers (PMTs) that are designed to detect the produced light by the scintillator with high timing and energy resolutions while being submerged in water [3].

#### 2.2.1 Detection Principle

Anti-electron neutrinos ( $\bar{v_e}$ ) generated from nuclear reactors are the primary source of neutrinos in JUNO, similar to many other neutrino experiments [4]. In JUNO, anti-neutrinos are detected by inverse beta decay reactions as shown in Equation 2.1.

$$\bar{\nu}_e + p \to e^+ + n \tag{2.1}$$

Figure 2.2: A sketch of the JUNO detector, showing the acrylic sphere of 35.4m diameter holding scintillation liquid of 20 kt. The central detector is surrounded by 18,000 20" PMTs and ~34,000 3" PMTs [12].

The reactor anti-neutrino interacts with a proton (p), creating a positron ( $e^+$ ) and a neutron (n). The generated positron annihilates with an electron and produces two gamma particles ( $\gamma$ ) that can be detected [13] as shown in Equation 2.2.

$$e + e^+ \rightarrow \gamma + \gamma$$

(2.2)

The generated gamma rays interact with the scintillator emitting light (photons). Liquid scintillators are organic solutions, which emit light on interaction with ionizing particles [14]. For large volume detectors, liquid scintillators are used together with PMTs to "translate the movement of an ionizing particle in the scintillator into an interpretable electronic pulse [14]". A linear alkyl benzene (LAB) based liquid scintillator is used in JUNO [3].

Both  $\bar{\nu_e}$  and  $\nu_e$  could alternatively interact with scintillators as shown in Equation 2.3 and Equation 2.4 to generate free positrons or electrons together with the radioactive isotopes <sup>12</sup>N and <sup>12</sup>B.

$$v_a + {}^{12}\text{C} \to e^- + {}^{12}\text{N}$$

(2.3)

$$\bar{v_e} + {}^{12}\text{C} \rightarrow e^+ + {}^{12}\text{B}$$

(2.4)

#### 2.2.2 Energy Resolution and Key Features

The determination of the mass hierarchy is difficult owing to the high energy resolution requirement. Based on calculations [3] it was determined that an energy resolution of  $\leq 3\%$  at 1MeV will be necessary to determine the mass hierarchy. In terms of photoelectrons, an

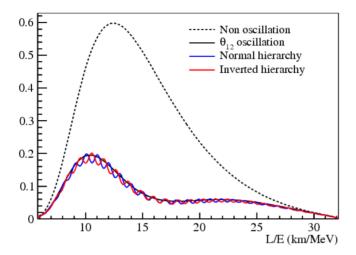

**Figure 2.3:** The probability distribution of events for normal and inverse neutrino mass hierarchy. The y-axis indicates the probability of neutrino events. On the x-axis, L is the distance between the reactor and the point where the neutrinos are observed and E is the energy of the neutrino generated by the reactors [15].

energy resolution of 3% at 1 MeV means for an event of 1 MeV (energy) a minimum sum of 1100 photons must be detected in the detector. Figure 2.3 shows the probability distribution of neutrino events for normal (blue) and inverse (red) hierarchy, calculated based on the standard model of elementary particles.

The detector of the JUNO experiment has a relatively large diameter (35.4 m). While the large diameter of the detector has the advantage of increasing the probability of neutrino interactions, it poses the problem of invisibility of the events occurring at the core of the detector. For counteracting this problem, PPO (2,5- diphenyloxazole) is added into the scintillator to increase the scintillation light yield and bis-MSB (1,4-bis[2-(2-methylphenyl)ethenyl]-benzene) with wavelength shifting property is added to the liquid scintillators (LAB). Among various measures for a higher energy resolution, PMTs with an improved targeted quantum efficiency ( $\approx$  30%) will be used in JUNO [3].

#### 2.2.3 Photomultiplier Tubes

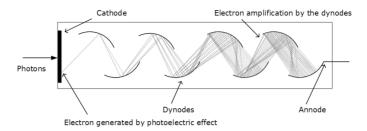

Photomultiplier tubes are highly sensitive detectors, which produce a charge (current) pulse when stimulated by a photon. When a photon hits the photo-emissive surface (photocathode) of the PMT, an electron can be emitted due to photo-absorption. The conversion rate of photons to electrons is determined by the quantum efficiency of the PMT. Typically, 1-3 photons out of 10 are converted to electrons [16].

The ejected electron from the cathode is directed towards dynodes, which are maintained at higher voltage potential than the cathode. Successive dynodes are biased at incremental voltage

**Figure 2.4:** An illustration of components inside a generic PMT. When a photon hits the photocathode, an electron is emitted by photoelectric effect. The emitted electron is multiplied at each stage of dynode by the process of secondary emission [16].

potential to focus the generated electrons towards the anode and to amplify the number of electrons. When an electron hits the dynode, it produces secondary electrons, which are focused towards the next higher potential dynode as shown in Figure 2.4. The electron multiplication factor depends on the number of dynode plates and the potential at which the dynode plates are biased. Usually, the potential difference between the dynode plates ranges between 100 V-150 V [17].

A PMT with 10 dynodes and the first dynode biased at 300 V as well as a potential difference of 100 V between successive dynodes results in the last dynode to be biased at 1300 V. This biasing requirement of the PMT requires a dedicated high voltage module. Since the electron multiplication is proportional to the dynode voltage, it is necessary to have stable high-voltage during measurement [18].

The signal produced at the anode of the PMT by a single photoelectron generated at the cathode is called single photoelectron response and is measured as 1 p.e.. The amplitude of the signal produced by one photoelectron at the anode highly depends on the gain and biasing of the individual PMT.

#### 2.2.4 Intelligent Photomultiplier Tubes for JUNO

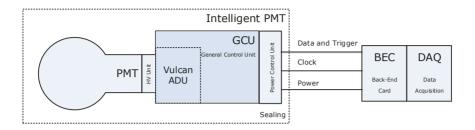

Among the various PMT installation schemes proposed for JUNO, Figure 2.5 portrays the underwater electronics scheme where the front-end electronics and the high voltage module are potted along with the PMT and kept underwater. With this particular arrangement of front-end electronics, the electrical pulses are digitized before being transmitted via a 100 m cable to the local computer farm. The digitized signals are robust against noise in comparison to analog signals. By placing the readout electronics next to the PMT, signal integrity is maximized as it is inversely proportional to the cable length used for signal transmission [3].

In this scheme of underwater electronics, the electronics are arranged in three stacked Printed Circuit Boards (PCBs) inside a water tight housing at the end of each PMT. The top PCB, which is in proximity to the PMT, contains the high voltage unit providing the voltages for the dynodes of the PMT. It is followed by the General Control Unit (GCU), which contains the Vulcan chip, a Double Data Rate (DDR) memory of 2 GB and an FPGA. The GCU performs data processing and

**Figure 2.5:** Overview of the intelligent PMT for the underwater scheme for JUNO. The high voltage unit (HV), analog to digital conversion unit (ADU), general control unit (GCU) and a power control unit are potted along with the PMT and kept under water. Data is transmitted to the data acquisition unit outside the water through a 100 m cable via the back-end card.

provides control signals for the Vulcan chip and the high voltage unit. The final PCB contains the power supply for the high voltage and all components of the GCU.

In this underwater system, a level discriminator is used to trigger the readout of a single PMT. When the integrated signal of the PMT crosses the configured threshold, a local trigger is generated indicating the occurrence of an event of interest. For an intelligent PMT (iPMT), the trigger threshold can be set just above noise level (for example 0.3 photoelectron (p.e.)). On generation, this local trigger is sent to the data acquisition unit above water. When a sufficient number of PMTs have generated trigger signals and when the event is qualified as a non-background event, the data acquisition unit generates a global trigger to extract signal data from all iPMTs.

The main tasks of the Vulcan readout chip are the conversion of the current signal to a voltage, digitization of analog voltage and transmission of the digital data. The data acquisition unit analyzes the triggers from the PMTs for a defined time frame (around 300 ns) or until a defined number of photoelectrons are generated by all PMTs combined before choosing to send commands to either overwrite the data or transmit the data. During this time period, the GCU buffers the digitized data in the local DDR3 RAM. The memory in the GCU also aids in buffering the data during a supernova event, which produces events at higher rates than normal.

The duration of data readout after a global trigger depends on the length of a pulse generated from a single photoelectron generated at the cathode of the PMT. In JUNO, the readout window is estimated to be around 32 ns. In case of background events, many photons can be detected by the PMT. In such cases, the signal might not return below the threshold and the logic will read for another 32 ns. The readout logic will continue to perform read operations until the signal falls below the threshold [3].

The back-end card splits the signal from the iPMT to different sub-modules of the data acquisition unit. One of the major requirement of the back-end cable is to ensure high speed

data transfer through the 100 m cable. The power for the PMT and electronics is also provided through the Ethernet cable using Power-over-Ethernet (PoE).

#### 2.3 Requirements for the Electronics Readout

The requirements of the Vulcan chip are directly derived from the requirements of the JUNO experiment itself. Some of the requirements and the corresponding design decision for the blocks of interest are listed below.

- Transit time spread is the variation in time due to the different trajectories taken by the electrons inside a PMT. This time spread affects the time of flight and also broadens the pulse [3], [16]. Inaccuracies due to the finite time width of photon emission and transient time spread sets the limit on the sampling frequency. Based on the performed simulations, a time resolution of 1 ns is required for the digitization of the signal to avoid loss of information [3].

- The bandwidth of the amplification circuit must match the bandwidth of the PMT to minimize the loss due to shaping. The TIA in Vulcan the bandwidth is targeted to 500 MHz to avoid this loss.

- The signal generated by the PMTs is quantified by the number of photoelectrons generated at the photo-cathode and is measured in p.e.. For the signal range of 1-100 p.e., the charge resolution is expected to change linearly from 0.1 p.e. to 1 p.e.. For a 100 p.e. signal, the resolution must be sufficient to distinguish single photoelectron. The ADC dynamic range should range from 1 p.e. to 4000 p.e. [3].

- The cooling system of the JUNO experiment sets the power budget for the complete electronics at ≈20 W per iPMT.

- Dead time is defined as the duration during which the electronics is unable to measure a signal between events. For JUNO, the readout electronics has the requirement of zero dead time. This requirement sets the necessity for a local buffer unit to buffer the data.

- The submerged structure of the detector rules out the possibility to replace faulty electronics during the course of operation. Since the experiment can only tolerate a Failure in Time (FIT) of 95 for all the electronics [19] in the iPMTs, it is necessary to install modules that are extensively tested and have a higher reliability quotient. A FIT value is thereby defined as the failure of 1 device per billion hours of operation [20].

The following chapters narrate the translation of the system requirements into specifications of the sub-modules.

## **Readout Solution for JUNO**

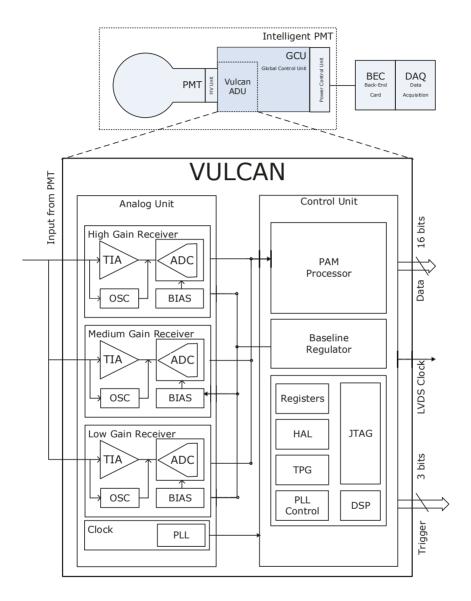

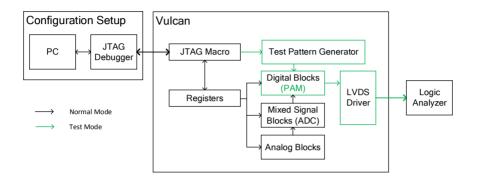

Based on the requirements for JUNO, the architecture of the Vulcan readout chip was designed. Figure 3.1 shows the major functional blocks of the Vulcan chip. The analog unit of the chip consists of the transimpedance amplifier (TIA), Analog to Digital Converter (ADC), Low Voltage Differential Signaling (IVDS) drivers, an internal clock generator and their biasing components. In this chapter, the overview of the Vulcan chip along with a brief description of the components and setup required for understanding the data processor and ADC regulator explained in Chapter 4 and 5 are presented.

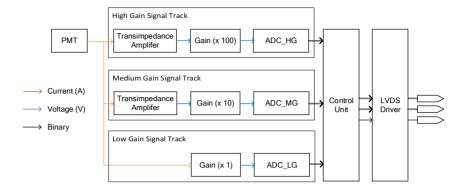

#### 3.1 Input Stage

The Vulcan chip contains three parallel signal tracks. Each track contains a transimpedance amplifier, a gain stage, an 8-bit analog to digital converter, buffers, a thermometer to gray encoder and biasing electronics. The Figure 3.2 shows the three parallel signal tracks of the Vulcan chip, with their respective ADCs: ADC for the high gain track (ADC HG), ADC for the medium gain track (ADC MG), ADC for the low gain track (ADC LG). The predominant difference among the signal tracks is the amplification factor of the signal by the transimpedance amplifier.

#### 3.1.1 Transimpedance Amplifier

The first signal conditioning block in the readout chip is the TIA. The TIA of the Vulcan chip has been specifically designed to have a very low input impedance ( $5\Omega$ ) to load the source significantly. The low input impedance of the TIA assures high sensitivity to the current generated by the PMT. The TIA performs current (I) to voltage conversion (V) in the first stage and amplification suitable for three signals chains (refer Section 3.1) of the ADC in the second stage.

**Overshoot Compensator (OSC):** A feed-forward-based overshoot compensation block is placed in parallel to the transimpedance amplifier to compensate for the overshoot produced by the coupling capacitor placed between the PMT and the transimpedance amplifier for high voltage protection (refer Section 4.7).

**Figure 3.1:** Overview of the Vulcan chip architecture and the position of the Vulcan chip in the front-end electronics signal chain.

3.1. INPUT STAGE

**Figure 3.2:** Overview of the three signal tracks in Vulcan chip and the common control unit for the tracks.

#### 3.1.2 Phase-Locked Loop