### Investigation of GeSn as Novel Group IV Semiconductor for Electronic Applications

**Christian Schulte-Braucks**

Schlüsseltechnologien / Key Technologies Band / Volume 168 ISBN 978-3-95806-312-9

Forschungszentrum Jülich GmbH Peter Grünberg Institut Halbleiter-Nanoelektronik (PGI-9)

### Investigation of GeSn as Novel Group IV Semiconductor for Electronic Applications

Christian Schulte-Braucks

Schriften des Forschungszentrums Jülich Reihe Schlüsseltechnologien / Key Technologies

Band / Volume 168

ISSN 1866-1807

ISBN 978-3-95806-312-9

Bibliografische Information der Deutschen Nationalbibliothek. Die Deutsche Nationalbibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliografie; detaillierte Bibliografische Daten sind im Internet über http://dnb.d-nb.de abrufbar.

| Herausgeber         | Forschungszentrum Jülich GmbH                   |

|---------------------|-------------------------------------------------|

| und Vertrieb:       | Zentralbibliothek, Verlag                       |

|                     | 52425 Jülich                                    |

|                     | Tel.: +49 2461 61-5368                          |

|                     | Fax: +49 2461 61-6103                           |

|                     | zb-publikation@fz-juelich.de                    |

|                     | www.fz-juelich.de/zb                            |

| Umschlaggestaltung: | Grafische Medien, Forschungszentrum Jülich GmbH |

|                     |                                                 |

Druck: Grafische Medien, Forschungszentrum Jülich GmbH

Copyright: Forschungszentrum Jülich 2018

Schriften des Forschungszentrums Jülich Reihe Schlüsseltechnologien / Key Technologies, Band / Volume 168

D 82 (Diss., RWTH Aachen University, 2017)

ISSN 1866-1807 ISBN 978-3-95806-312-9

Vollständig frei verfügbar über das Publikationsportal des Forschungszentrums Jülich (JuSER) unter www.fz-juelich.de/zb/openaccess.

This is an Open Access publication distributed under the terms of the <u>Creative Commons Attribution License 4.0</u>, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Für Lena, Hannes und Theo

#### Kurzfassung

In den letzten Jahren haben einkristalline GeSn Halbleiterverbindungen deutliches wissenschaftliches Interesse erregt, besonders nachdem 2015 GeSn mit ausreichend hohem Sn-Gehalt und hoher Kristallqualität als direkter Halbleiter experimentell nachgewiesen wurde. Während verbesserte optische Eigenschaften bei einem direkten Material naheliegen, werden für GeSn auch verbesserte elektrische Eigenschaften erwartet, wie z.B. erhöhte Ladungsträgerbeweglichkeiten und Band-zu-Band-Tunnelraten, welche für Metal-Oxid-Halbleiter-Transistoren bzw. für Tunnelfeldeffekttransistoren von Vorteil sind. Die neuartigen GeSn Halbleiter stellen damit ein interessantes Materialsystem dar, welches ein neues Forschungsfeld zur Untersuchung dessen physikalischer, elektrischer, optischer und chemischer Eigenschaften eröffnet. Allerdings verlangt die Neuheit des Materialsystems auch die Entwicklung, Anpassung und Verifizierung aller Prozessschritte zur Herstellung GeSn-basierter Halbleiterbauelemente. Diese Arbeit konzentriert sich in erster Linie auf die elektrischen Eigenschaften von GeSn, deren Abhängigkeiten vom Sn-Gehalt sowie mögliche Anwendungen in elektronischen Bauelementen. Die Bausteine von Feldeffekttransistoren werden einzeln erforscht. Mittels Röntgenphotoelektronenspektroskopie erfolgt zunächst die Untersuchung der Reinigung der GeSn Oberfläche vor der Abscheidung des Dielektrikums sowie die Untersuchung der Oberflächenmanipulation beim selektiven Ätzen von Ge zu GeSn. Zur Verwendung als elektrischer Kontakt in GeSn-basierten Bauelementen werden NiGeSn-Verbindungen strukturell, mittels Röntgenbeugung und elektrisch, mittels Strom-Spannungsmessungen, charakterisiert. Schottky-Barriere, Schichtwiderstand und spezifischer Kontaktwiderstand werden extrahiert. Sehr kleine Schottky-Barrieren von Minimum 0.06 eV werden beobachtet. Erstmals ist es gelungen, die NiGeSn/GeSn Schottky-Barriere mittels Dotierstoffsegregation einzustellen. Als nächster Baustein werden Metal-Oxid-Halbleiter-Kondensatoren umfangreich untersucht. Dielektrikum/GeSn-Grenzflächendefektdichten werden für einen breiten Sn-Gehaltbereich extrahiert. Der Schwerpunkt liegt hierbei auf dem Einfluss der Bandstruktur des GeSn auf die Kapazitäts-Spannungscharakteristika. Es wird ein grundlegender Zusammenhang zwischen der Sn-induzierten Verringerung der Bandlücke und der Minoritätsladungsträgerantwort beobachtet. Die maximal erzielte, flächennormierte Kapazität beträgt ca.  $3\,\mu\text{F/cm}^2$ . Als Schritt in Richtung GeSn-basierter Tunnelfeldeffekttransistoren werden Esaki-Dioden (Tunneldioden) hergestellt und elektrisch charakterisiert. Die Esaki-Dioden verfügen über einen negativen differentiellen Widerstand mit einem Verhältnis aus lokalem Strommaximum und -minimum von 2.3, was als experimenteller Beweis von Band-zu-Band-Tunneln zählt. In Ge<sub>0.89</sub>Sn<sub>0.11</sub> p-i-n-Dioden werden erhöhte Band-zu-Band-Tunnelraten im Vergleich zu Ge beobachtet, was auf die verringerte und direkte Bandlücke zurückgeführt wird. Auf Grundlage dieser Arbeiten werden schließlich vertikale  $Ge_{0.93}Sn_{0.07}/Ge$  Tunnelfeldeffekttransistoren realisiert und umfangreich charakterisiert, wobei Band-zu-Band-Tunneln und defektunterstütztes Tunneln als Hauptbeiträge zum Transistorstrom nachgewiesen werden. Abschließend dienen Hall-Messungen dem experimentellen Nachweis erhöhter Elektronenbeweglichkeiten in GeSn mit direkter Bandlücke. Mit bis zu 4600 cm<sup>2</sup>/Vs stellen diese die bis jetzt höchsten Volumenladungsträgerbeweglichkeiten in der IV-Hauptgruppe bei einem Dotierniveau von ca.  $2.9 \cdot 10^{17} \,\mathrm{cm^{-3}}$  dar.

#### Abstract

Within the last few years single crystalline GeSn semiconductor alloys aroused significant scientific interest, especially since 2015, when GeSn with sufficiently high Sn content and crystalline quality was demonstrated as fundamentally direct bandgap group IV semiconductor. While enhanced optical properties are evident for direct bandgap materials compared to the fundamentally indirect Ge and Si group IV semiconductors, also enhanced electrical properties like increased carrier mobilities and enhanced band-to-band tunneling are expected for direct bandgap GeSn which are beneficial for metal-oxidesemiconductor transistors and tunnel field-effect transistors, respectively. The novel GeSn semiconductor alloys thereby manifests a fascinating emerging material system allowing a wide scope to study its fundamental physical, electrical, optical and chemical properties. On the other hand the novelty of the material system demands the re-development or modification and verification of all steps necessary to build GeSn based semiconductor devices. A comprehensive study is presented, focusing on the electrical properties of GeSn, their dependence on Sn content and possible applications in novel electronic devices. The building blocks of field-effect transistors are studied individually. GeSn surface composition and manipulation are investigated via X-ray photoemission spectroscopy to study pre-high- $\kappa$  deposition cleaning and highly selective Ge/GeSn etching processes. NiGeSn alloys for the use as electrical contacts of GeSn devices are structurally and electrically characterized using X-ray diffraction, transmission electron microscopy and temperature dependent current voltage measurements, respectively. Schottky barrier height, sheet resistance and specific contact resistivity are extracted. The modification of the NiGeSn/GeSn Schottky barrier height via dopant segregation is demonstrated for the first time. Schottky-barrier heights as low as  $0.06 \,\mathrm{eV}$ are observed. As a next module metal-oxide-semiconductor capacitors are comprehensively studied. High- $\kappa/\text{GeSn}$  interface trap densities are extracted for a wide range Sn contents. The focus is placed on the effect of the electronic band structure of GeSn on the capacitance voltage characteristics. Fundamental trends demonstrating the correlation of Sn-induced bandgap shrinkage and minority carrier response are observed. Furthermore a maximum capacitance of approx.  $3 \,\mu\text{F/cm}^2$  is achieved. As a step towards GeSn based tunnel field-effect transistors, Esaki diodes (tunnel diodes) are fabricated and electrically characterized. Negative differential resistance with a peak-to-valley current ratio of 2.3 is observed as an experimental proof of band-to-band tunneling. Enhanced band-to-band tunneling rates are observed in  $Ge_{0.89}Sn_{0.11}$  p-i-n diodes compared to Ge taking advantage of the low and direct bandgap. These studies lead to the realization of vertical heterojunction  $Ge_{0.93}Sn_{0.07}/Ge$  tunnel field-effect transistors. An extensive analysis is provided identifying the various contributions to the overall transistor current, particularly band-to-band tunneling and trap-assisted tunneling. Finally, Hall measurements are presented, showing enhanced electron mobilities in direct bandgap GeSn as compared to Ge. With up to  $4600 \,\mathrm{cm^2/Vs}$  this marks the highest bulk electron mobilities at the respective doping level of  $2.9 \cdot 10^{17} \,\mathrm{cm^{-3}}$  in a group IV semiconductor so far.

## Contents

| Lis | st of   | Figures                                                               | vii |

|-----|---------|-----------------------------------------------------------------------|-----|

| Lis | st of   | Tables                                                                | x   |

| Lis | st of . | Abbreviations                                                         | x   |

| 1.  | Intro   | oduction                                                              | 1   |

| 2.  | The     | (Si)GeSn material system                                              | 5   |

|     | 2.1.    | GeSn effective mass and mobility                                      | 8   |

|     | 2.2.    | Thermal stability and doping                                          | 10  |

| 3.  | GeS     | n Surface Composition and Manipulation                                | 11  |

|     | 3.1.    | Surface Cleaning and Native Oxide Removal                             | 12  |

|     | 3.2.    | (Selective) Etching of GeSn                                           | 14  |

|     | 3.3.    | Summary                                                               | 18  |

| 4.  | NiG     | eSn alloys as contacts for GeSn                                       | 19  |

|     | 4.1.    | Metal-Semiconductor Contacts                                          | 20  |

|     |         | 4.1.1. Electronic Transport in Metal-Semiconductor Contacts           | 22  |

|     | 4.2.    | Properties of NiGeSn                                                  | 24  |

|     |         | 4.2.1. Structural Analysis of NiGeSn                                  | 25  |

|     |         | 4.2.2. Schottky Barrier Height Extraction of NiGeSn/GeSn contacts     | 27  |

|     |         | 4.2.3. Dopant Segretation at the NiGeSn/GeSn Interface $\ldots$       | 29  |

|     | 4.3.    | Summary                                                               | 34  |

| 5.  | MO      | S-Structures on (Si)GeSn                                              | 35  |

|     | 5.1.    | MOS-basics                                                            | 37  |

|     |         | 5.1.1. The ideal MOS-Capacitor                                        | 38  |

|     |         | 5.1.2. Impact of Interface Traps on CV Characteristics                | 44  |

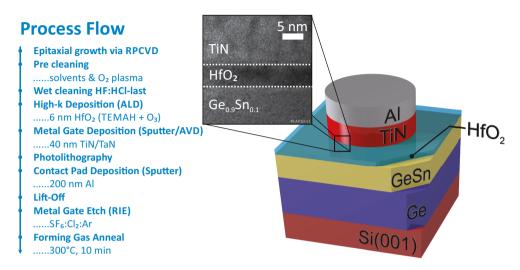

|     | 5.2.    | Fabrication and Verification of (Si)GeSn MOS-Structures               | 52  |

|     | 5.3.    | Extraction of Interface Trap Densities                                | 60  |

|     | 5.4.    | high- $\kappa$ scaling on GeSn MOS-Structures                         | 62  |

|     | 5.5.    |                                                                       | 66  |

|     |         | 5.5.1. Minority Carrier Response in (Si)GeSn MOSCaps                  | 67  |

|     |         | 5.5.2. Numerical simulations for minority carrier generation analysis | 72  |

|     | 5.6.    | Temperature Dependence and Deep Defect analysis                       | 76  |

|     | 5.7.    | Summary                                                               | 80  |

| 6. | 6.1.<br>6.2.<br>6.3.<br>6.4.                         | n p-i-n Diodes         The Esaki Diode         6.1.1. Band-to-Band Tunneling         6.1.2. Excess Current         6.1.3. Thermal Current         Diode Fabrication         Electrical Characterization and Modeling         Electroluminescence from GeSn p-i-n Diodes         Summary | <b>81</b><br>82<br>84<br>86<br>88<br>89<br>90<br>97 |

|----|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| 7. | <ol> <li>7.1.</li> <li>7.2.</li> <li>7.3.</li> </ol> | n-based Tunnel FETs<br>The Tunnel FET                                                                                                                                                                                                                                                   | <b>103</b><br>104<br>108<br>112<br>116              |

| 8. | Hall<br>8.1.<br>8.2.<br>8.3.<br>8.4.                 | Measurements on GeSn         (Magneto)transport in Semiconductors         Fabrication of GeSn on Insulator - GSOI         Hall Measurements         Summary                                                                                                                             | <b>117</b><br>118<br>120<br>122<br>126              |

| 9. | Con                                                  | clusion and Outlook                                                                                                                                                                                                                                                                     | 129                                                 |

| Ac | know                                                 | ledgements                                                                                                                                                                                                                                                                              | 133                                                 |

| Bi | bliogr                                               | raphy                                                                                                                                                                                                                                                                                   | 137                                                 |

| Α. | Serie                                                | es resistance Correction of CV Measurements                                                                                                                                                                                                                                             | I                                                   |

| В. | Proc                                                 | cess Details                                                                                                                                                                                                                                                                            | П                                                   |

| С. | List                                                 | of Publications                                                                                                                                                                                                                                                                         | v                                                   |

| D. | Curi                                                 | culum Vitae                                                                                                                                                                                                                                                                             | XI                                                  |

# List of Figures

| 2.1.         | Si, Ge and Sn band structure and GeSn bandgap $\mathit{vs.}$ Sn content $~$                                                           | 6        |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.2.         | Contour plot of directness <i>vs.</i> Sn content and biaxial strain as well as                                                        | 7        |

| 2.3.         | bandgap <i>vs.</i> strain                                                                                                             | 7<br>9   |

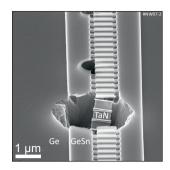

| 3.1.         | Demonstration of material loss in GeSn nanostructures after exposure to                                                               |          |

| 3.2.         | NH <sub>4</sub> OH:H <sub>2</sub> O <sub>2</sub>                                                                                      | 12<br>13 |

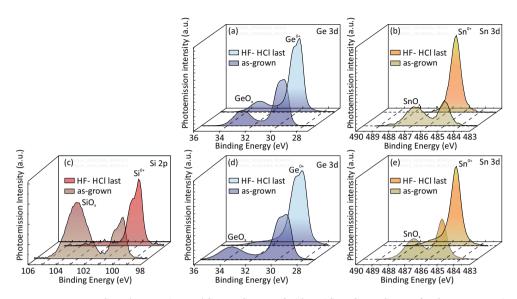

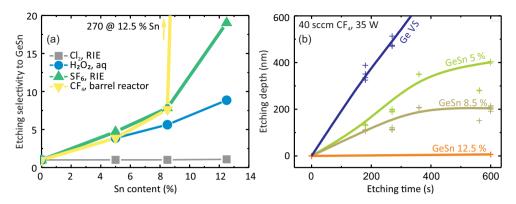

| 3.3.         | Etching selectivity for various etching processes.                                                                                    | 15       |

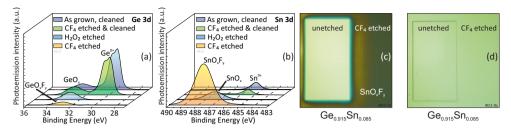

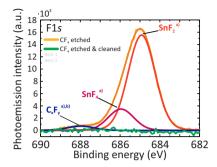

| 3.4.         | XPS analysis of the GeSn surface after different chemical treatments to study the etching mechanism.                                  | 16       |

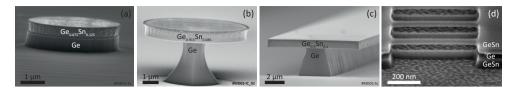

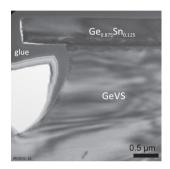

| 3.5.<br>3.6. | F1s peak after $CF_4$ etching prior to and after HF:HCl cleaning SEM images of GeSn structures fabricated for photonic and electronic | 17       |

| 3.7.         | application                                                                                                                           | 18<br>18 |

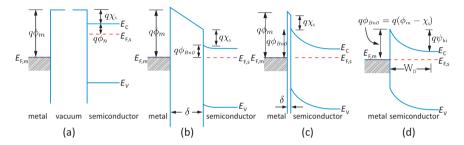

| 4.1.         | Formation of a Schottky barrier at a MS interface.                                                                                    | 20       |

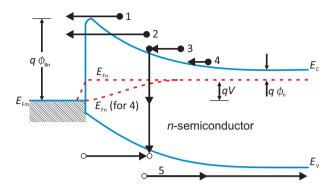

| 4.2.         | Transport mechanisms in a forward bias Schottky contact                                                                               | 21       |

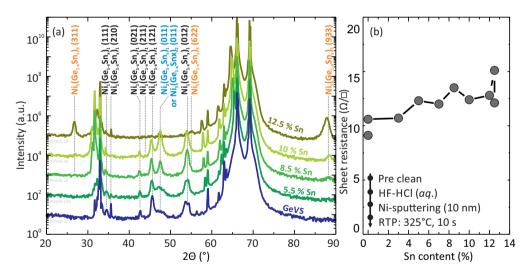

| 4.3.         | XRD and sheet resistance measurement of NiGeSn                                                                                        | 25       |

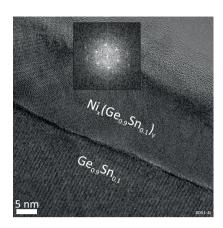

| 4.4.         | XTEM of a NiGeSn/GeSn MS contact                                                                                                      | 26       |

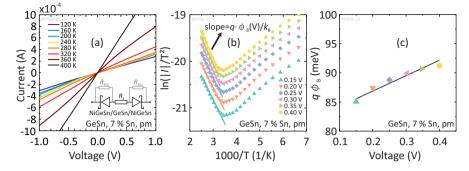

| 4.5.         | hSBH-extraction on NiGeSn formed on $Ge_{0.93}Sn_{0.07}$ .                                                                            | 28       |

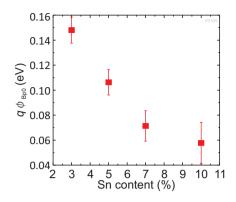

| 4.6.         | hSBH, $q\phi_{Bp0}$ vs. Sn content featuring a significant decrease of $q\phi_{Bp0}$ with                                             |          |

|              | Sn content.                                                                                                                           | 29       |

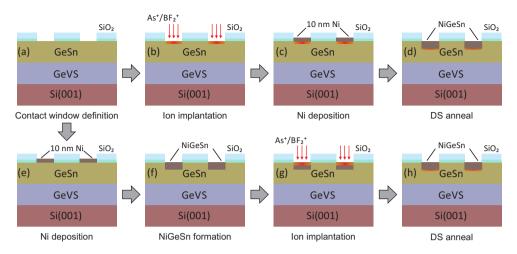

| 4.7.         | Key fabrication steps for MSM diodes with dopant segregation                                                                          | 31       |

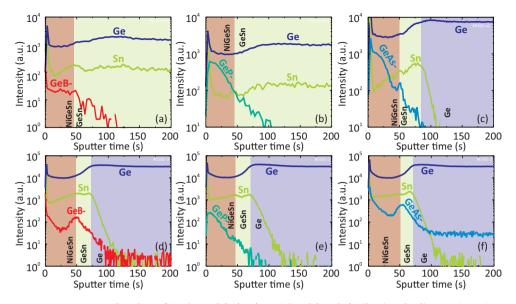

| 4.8.         | ToF-SIMS profiles for dopant segregation in NiGeSn/GeSn-contacts                                                                      | 32       |

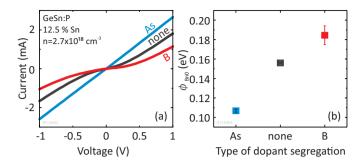

| 4.9.         | MSM diode characteristics and corresponding eSBH for DS with As,B                                                                     |          |

|              | and without additional implantation.                                                                                                  | 33       |

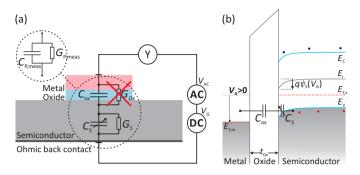

| 5.1.         | MOSCap sketch, internal equivalent circuit and band diagram                                                                           | 38       |

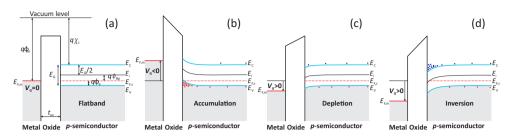

| 5.2.         | Band diagram of an ideal <i>p</i> -type MOSCap in different bias regimes                                                              | 39       |

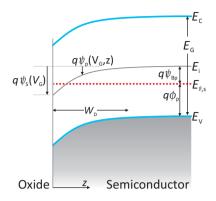

| 5.3.         | Band bending in a MOSCap                                                                                                              | 40       |

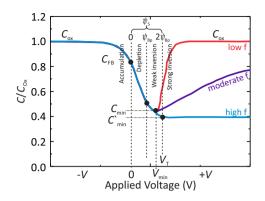

| 5.4.         | Typical CV characteristics of a MOSCap on <i>p</i> -type Si for low, medium                                                           |          |

|              | and high AC-probing frequency                                                                                                         | 42       |

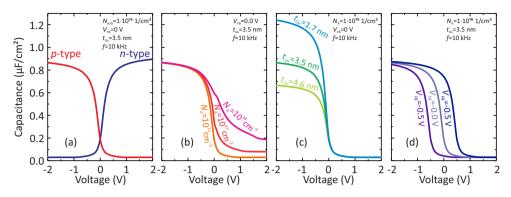

| 5.5.         | Simulated Si MOSCap CV curves for different majority carrier type, $N_{\rm A}$ ,                                                      |          |

|              | $t_{\rm Ox}$ and $V_{\rm FB}$ .                                                                                                       | 43       |

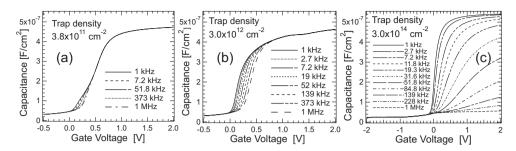

| 5.6.         | Simulated CV characteristics of a GaAs MOSCap with different $D_{\rm it}$ levels.                                                     | 46       |

| 5.7.         | Band diagram of a MOSCap with interface traps and corresponding equiv- $% \mathcal{A}^{(n)}$                                          |          |

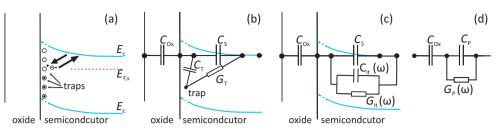

|              | alent circuit model                                                                                                                   | 47       |

| 5.8.  | Typical CV characteristics with minority carrier response and correspond-                                                |    |

|-------|--------------------------------------------------------------------------------------------------------------------------|----|

|       | ing band diagram of a MOSCap with interface traps biased in weak inversion                                               | 49 |

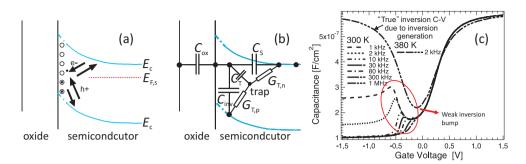

| 5.9.  | Calculation of interface trap frequency and detectable defect energy range                                               |    |

|       | for Ge                                                                                                                   | 51 |

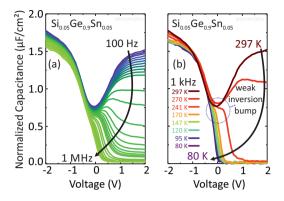

| 5.10. | CV measurements of a $Pt/HfO_2/(SiGeSn)O_x/Si_{0.05}Ge_{0.9}Sn_{0.05}MOSCap$                                             | 54 |

|       | MOSCap process flow for device integration and XTEM                                                                      | 55 |

| 5.12. | CV characteristics of a $450$ °C deposited TaN/HfO <sub>2</sub> stack on SiGeSn                                          | 56 |

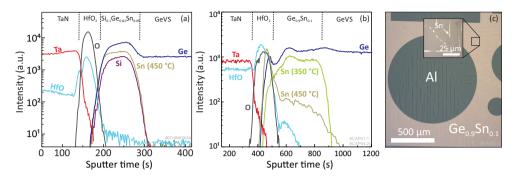

|       | ToF-SIMS analysis of TaN/HfO <sub>2</sub> /(Si)GeSn stacks.                                                              | 57 |

|       | Variability of TaN/HfO <sub>2</sub> /Ge(Sn) MOSCaps                                                                      | 58 |

| 5.15. | Gate leakage current density vs. gate voltage for a MOSCap with AVD                                                      |    |

|       | TaN                                                                                                                      | 58 |

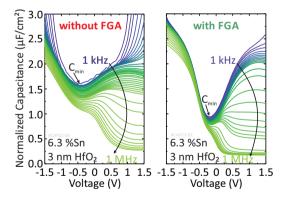

| 5.16. | Demonstration of the positive effect of FGA on CV characteristics                                                        | 59 |

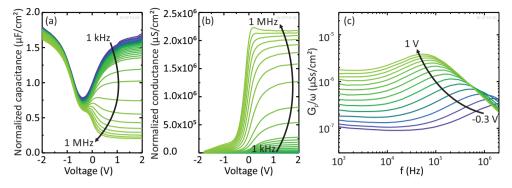

| 5.17. | CV, GV & $G_{\rm p}/\omega$ -vsf characteristics of a TiN/5 nm HfO <sub>2</sub> /Ge <sub>0.915</sub> Sn <sub>0.085</sub> |    |

|       | MOSCap                                                                                                                   | 60 |

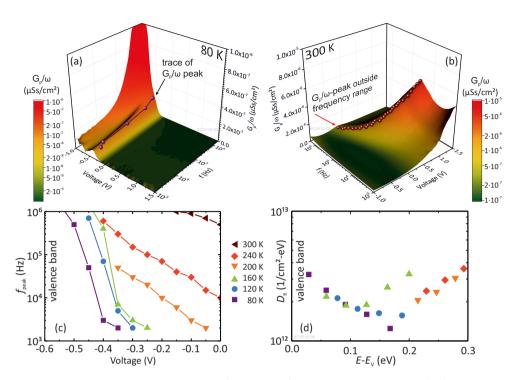

| 5.18. | $3D G_P/\omega$ -vsV <sub>G</sub> and f plot, characteristic trap frequency vs. gate voltage                             |    |

|       | and $D_{\rm it}$ vs. trap energy.                                                                                        | 61 |

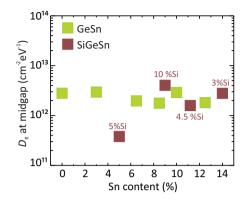

| 5.19. | $D_{\rm it}$ at midgap vs. Sn content for several samples covering a wide range of                                       |    |

|       | Sn content. GeSn with TiN and SiGeSn with Pt metal gate, respectively.                                                   | 62 |

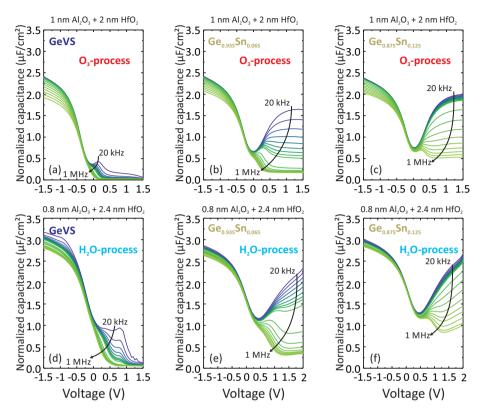

| 5.20. | CV on tri-layer gate stack                                                                                               | 64 |

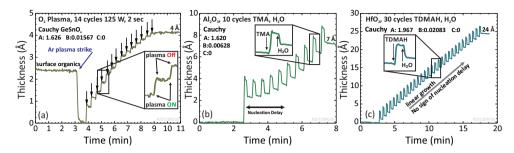

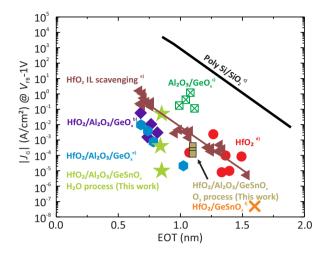

| 5.21. | In-situ ellipsometry                                                                                                     | 65 |

| 5.22. | EOT benchmark                                                                                                            | 66 |

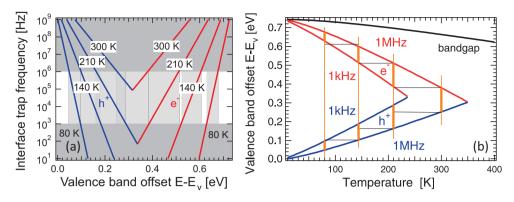

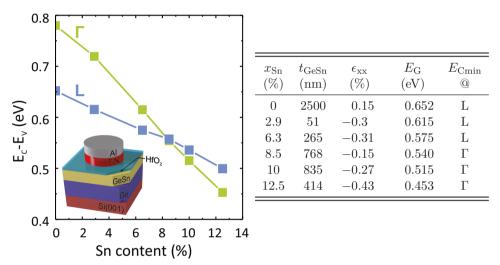

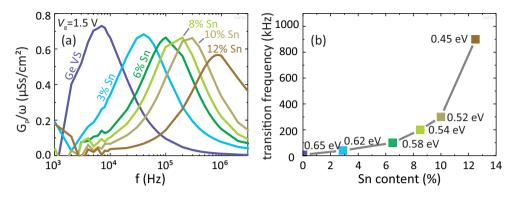

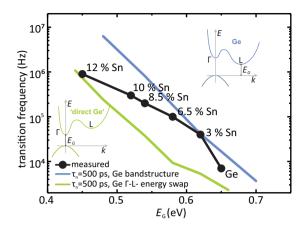

| 5.23. | Bandgap at $\Gamma$ and L-point vs. Sn content of the analyzed samples                                                   | 67 |

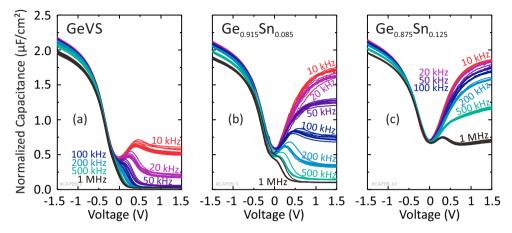

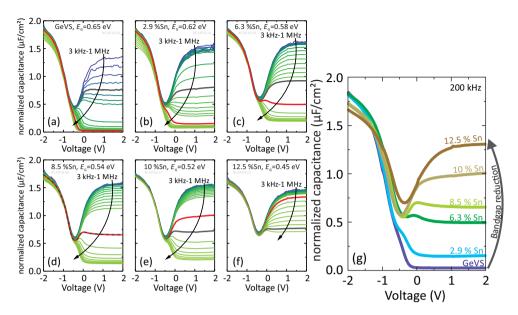

| 5.24. | Room temperature CV characteristics of GeSn-based MOSCaps with dif-                                                      |    |

|       | ferent Sn contents.                                                                                                      | 68 |

| 5.25. | Parallel conductance divided by angular frequency vs. frequency and                                                      |    |

|       | transition frequency vs. Sn content.                                                                                     | 69 |

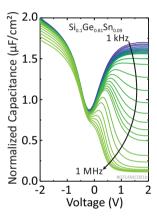

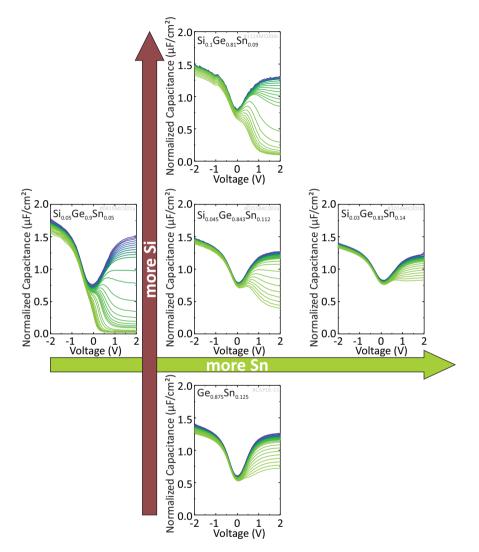

| 5.26. | CV characteristics of several SiGeSn MOSCaps differing in Sn and Si                                                      |    |

|       | contents                                                                                                                 | 71 |

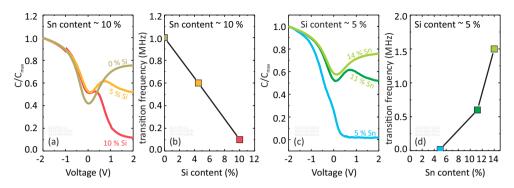

| 5.27. | CV characteristics and transition frequency of SiGeSn MOSCaps when                                                       |    |

|       | changing $Sn(Si)$ content while keeping the $Si(Sn)$ content fixed                                                       | 72 |

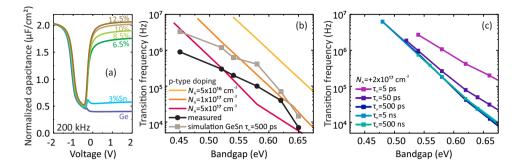

| 5.28. | Simulation of CV characteristics and transition frequency                                                                | 74 |

| 5.29. | Transition frequency vs. bandgap for simulated, artificially direct Ge                                                   |    |

|       | band structure.                                                                                                          | 76 |

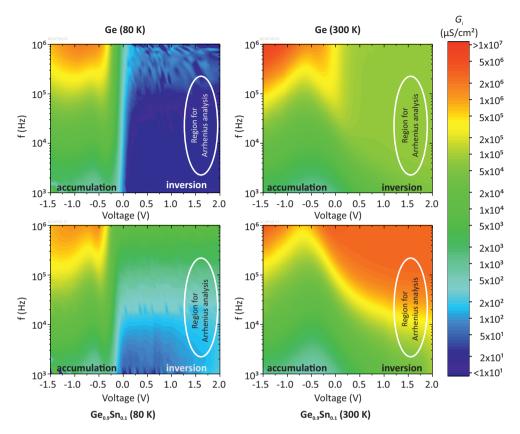

| 5.30. | Conductance maps for GeVS and $\mathrm{Ge}_{0.9}\mathrm{Sn}_{0.1}$ at 300 K and at 80 K                                  | 77 |

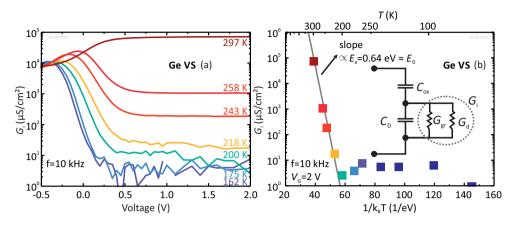

| 5.31. | Arrhenius analysis of inversion conductance for activation energy extraction.                                            | 78 |

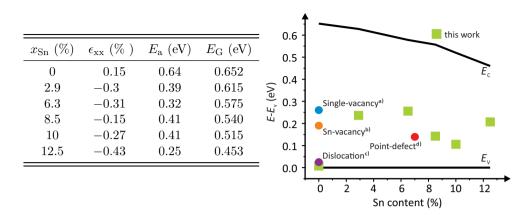

| 5.32. | Position of the extracted dominant SRH-levels in the bandgap referenced                                                  |    |

|       | to the valence band edge.                                                                                                | 79 |

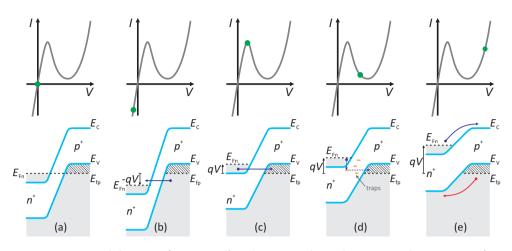

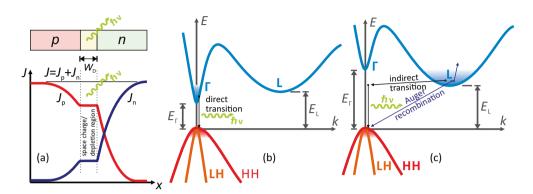

| 6.1.  | Band diagram and schematic IV characteristics of a tunnel diode in dif-                                                  |    |

| 5.1.  | ferent bias regimes                                                                                                      | 83 |

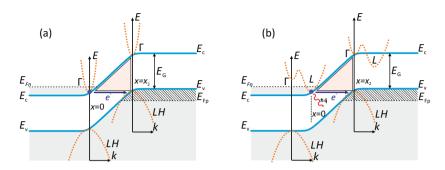

| 6.2.  | Direct vs. indirect tunneling                                                                                            | 84 |

|       |                                                                                                                          |    |

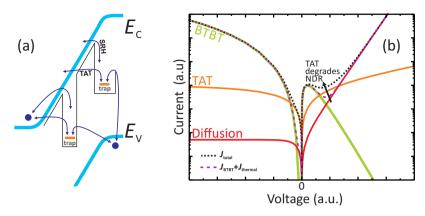

| 6.3.  | Illustration of TAT process and IV curve with breakdown in different current components        | 87  |

|-------|------------------------------------------------------------------------------------------------|-----|

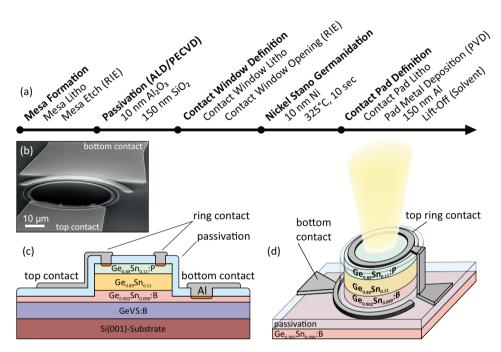

| 6.4.  | Process flow and layer sketch for GeSn <i>p-i-n</i> diode fabrication                          | 89  |

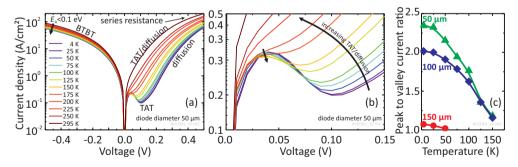

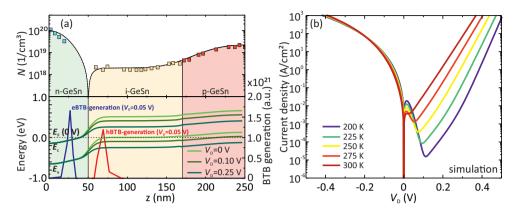

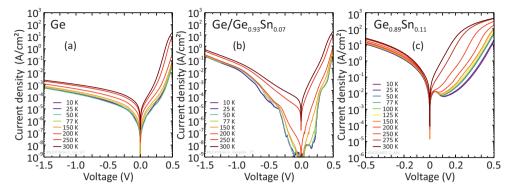

| 6.5.  | Temperature-dependent IV characteristics of GeSn $p-i-n$ diodes showing                        | 00  |

|       | NDR at low temperatures $\ldots$                                                               | 91  |

| 6.6.  | Band diagram and simulated IV characteristics of the $Ge_{0.89}Sn_{0.11}/$                     | -   |

|       | $Ge_{0.902}Sn_{0.098} p$ - <i>i</i> - <i>n</i> diode                                           | 93  |

| 6.7.  | Breakdown of simulated diode current in contributions from direct BTBT,                        |     |

|       | indirect BTBT and diffusion                                                                    | 94  |

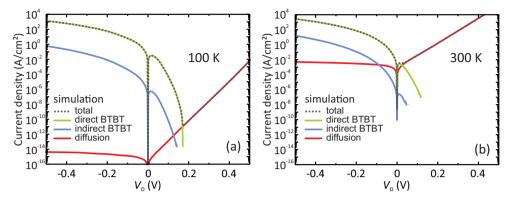

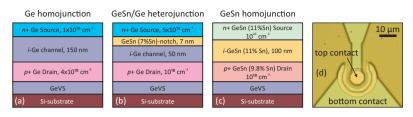

| 6.8.  | (a-c) Illustrated layer stacks of the three analyzed p-i-n structures. (d)                     | 01  |

|       | Optical microscopy image of a fabricated diode                                                 | 95  |

| 6.9.  | Temperature-dependent IV characteristics of Ge-homojunction, GeSn/Ge-                          |     |

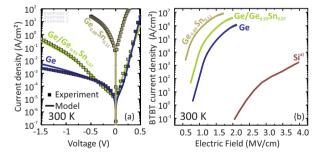

| 0.0.  | heterojunction and GeSn-homojunction $p$ - $i$ - $n$ diode                                     | 96  |

| 6.10. | Modeling of $p$ - $i$ - $n$ IV characteristics and extraction of BTBT current                  | 96  |

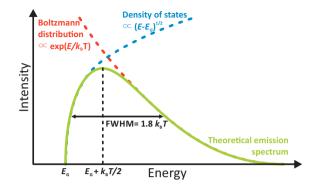

|       | Recombination in a forward biased $p - n$ diode $\dots \dots \dots \dots \dots$                | 98  |

|       | Theoretical EL spectrum for direct transitions.                                                | 99  |

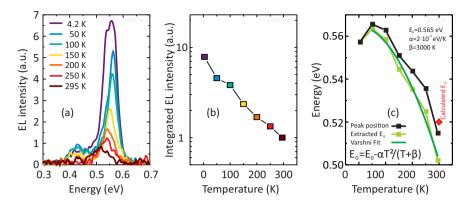

|       | Measured EL from GeSn $p$ - $i$ - $n$ diodes                                                   | 100 |

|       |                                                                                                |     |

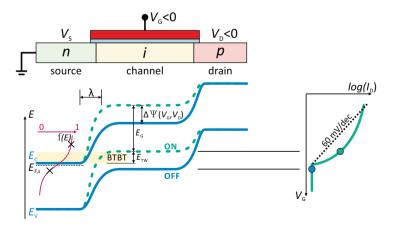

| 7.1.  | Operation principle of a TFET                                                                  | 104 |

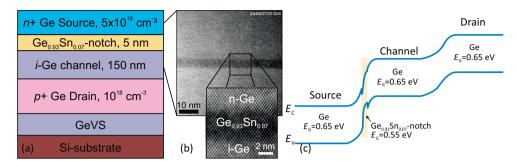

| 7.2.  | Layer stack used for GeSn $p$ TFET fabrication                                                 | 109 |

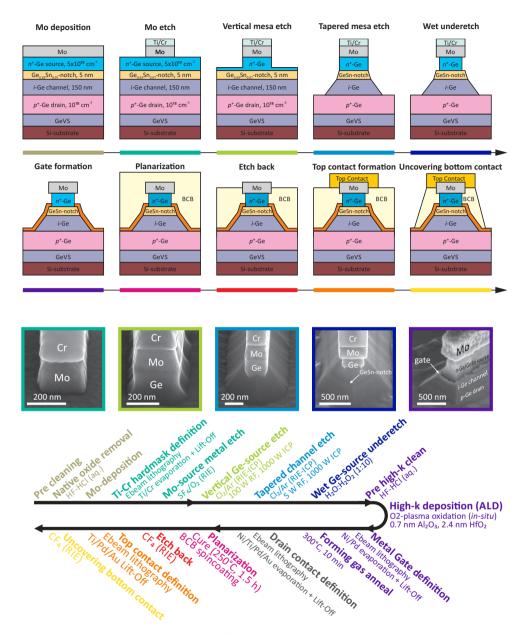

| 7.3.  | Key steps for vertical Ge/GeSn TFET fabrication                                                | 110 |

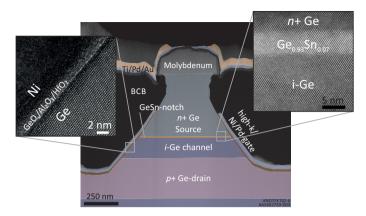

| 7.4.  | High-resolution STEM cross section of a GeSn/Ge TFET                                           | 111 |

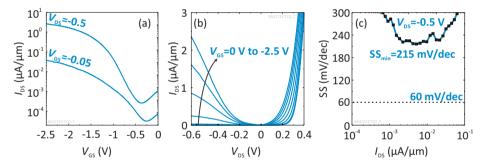

| 7.5.  | Electrical characteristics of a $Ge_{0.93}Sn_{0.07}/Ge-pTFET$                                  | 112 |

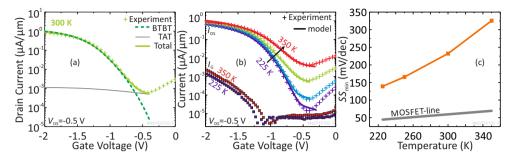

| 7.6.  | . Temperature dependence and modeling of GeSn/Ge TFET characteristics.113                      |     |

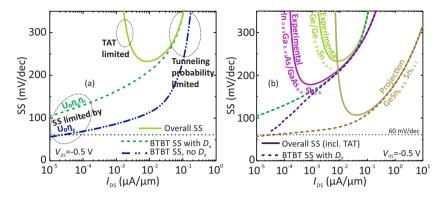

| 7.7.  | Analysis of transport mechanisms contributing to the overall TFET char-                        |     |

|       | acteristics                                                                                    | 114 |

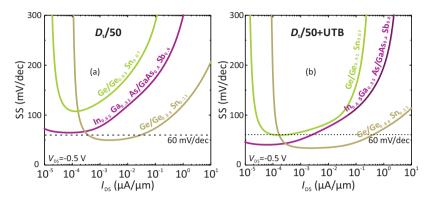

| 7.8.  | Projected $SS$ vs. $I_{DS}$ characteristics $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 115 |

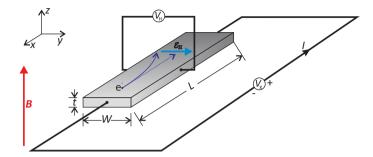

| 8.1.  | Illustration of the classical Hall effect                                                      | 119 |

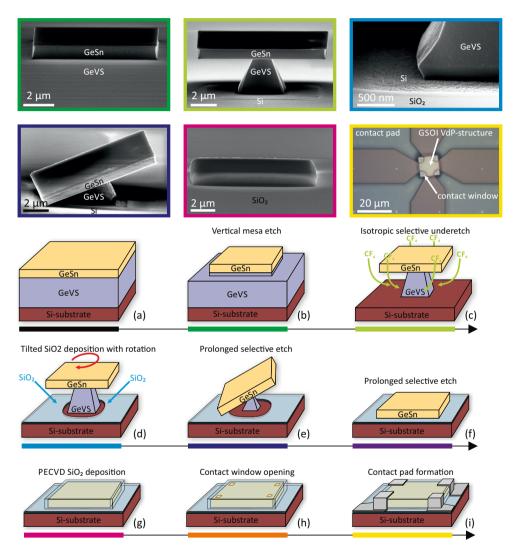

| 8.2.  | Key steps for GSOI fabrication.                                                                | 121 |

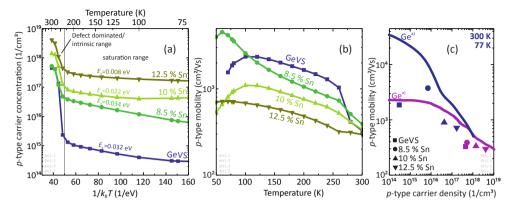

| 8.3.  | <i>p</i> -GeSn hole carrier density and mobility                                               | 123 |

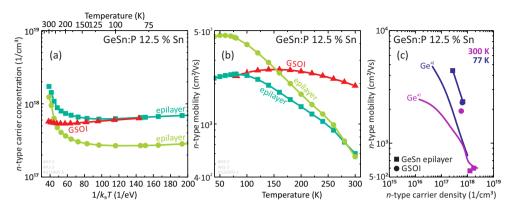

| 8.4.  | <i>n</i> -GeSn electron carrier density and mobility                                           | 125 |

## List of Tables

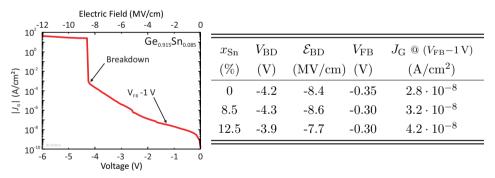

| 5.1. | Breakdown voltage, breakdown field and gate leakage for MOSCaps with |     |

|------|----------------------------------------------------------------------|-----|

|      | AVD TaN                                                              | 58  |

| 5.2. | Material parameters of the investigated GeSn sample series           | 67  |

| 5.3. | Inversion response activation energies                               | 79  |

| 6.1. | <i>p-i-n</i> diode material parameters                               | 91  |

| 7.1. | pTFET benchmarking                                                   | 112 |

|      | Etch rates of GeSn in various etchants                               |     |

## List of Abbreviations

| $\mathbf{AC}$ | Alternating Current               |

|---------------|-----------------------------------|

| Al            | Aluminum                          |

| ALD           | Atomic Layer Deposition           |

| APL           | Applied Physics Letters           |

| Ar            | Argon                             |

| As            | Arsenic                           |

| AVD           | Atomic Vapor Deposition           |

| Au            | Gold                              |

| В             | Boron                             |

| BCB           | Benzocyclobuten                   |

| BTBT          | Band-to-Band Tunneling            |

| CET           | Capacitance Equivalent Thickness  |

| $\mathbf{CV}$ | Capacitance Voltage (measurement) |

| CVD           | Chemical Vapor Deposition         |

| CMOS           | Complimentary MOS                 |

|----------------|-----------------------------------|

| $\mathbf{Cr}$  | Chromium                          |

| DC             | Direct Current                    |

| DFT            | Denstiy Functional Theory         |

| DLTS           | Deep Level Transient Spectroscopy |

| DMSO           | Dimethyl Sulfoxide                |

| DOS            | Density of States                 |

| DS             | Dopant Segregation                |

| EBL            | Electron Beam Lithography         |

| ECV            | Electrochemical CV                |

| EOT            | Equivalent Oxide Thickness        |

| EL             | Electroluminescence               |

| $\mathbf{F}$   | Fluorine                          |

| FET            | Field-Effect Transistor           |

| FFT            | Fast Fourier Transform            |

| FGA            | Forming Gas Anneal                |

| FIB            | Focused Ion Beam                  |

| GaAs           | Gallium Arsenide                  |

|                | Gainum Arseniue                   |

| GaAsSb         | Gallium Arsenide Antimonide       |

| GaAsSb<br>GaSb |                                   |

|                | Gallium Arsenide Antimonide       |

| GSOI          | GeSn on Insulator                      |

|---------------|----------------------------------------|

| $\mathbf{GV}$ | Conductance Voltage (measurement)      |

| ${ m GeVS}$   | Ge Virtual Substrate                   |

| HCl           | Hydrochloric acid                      |

| HF            | Hydrofluoric acid                      |

| нн            | Heavy Hole                             |

| HNF           | Helmholtz Nano Facility                |

| IC            | Integrated Circuit                     |

| ICSD          | Inorganic Crystal Structure Database   |

| ICP           | Inductively Coupled Plasma             |

| ICT           | Information & Communication Technology |

| IEDM          | International Electron Devices Meeting |

| IISG          | Implantation Into Stanogermanide       |

| IL            | Interfacial Layer                      |

| InAs          | Indium Arsenide                        |

| InGaAs        | Indium Gallium Arsenide                |

| InSb          | Indium Antimonide                      |

| IoT           | Internet of Things                     |

| IV            | Current Voltage (measurement)          |

| JAP           | Journal of Applied Physics             |

| LED           | Light Emitting Diode                   |

| LH            | Light Hole                             |

|               |                                        |

| MIT                              | Massachusetts Institute of Technology             |

|----------------------------------|---------------------------------------------------|

| Mo                               | Molybdenum                                        |

| MOS                              | Metal-Oxide-Semiconductor                         |

| MOSCap                           | Metal-Oxide-Semiconductor Capacitor               |

| MOSFET                           | Metal-Oxide-Semiconductor Field-Effect Transistor |

| $\mathbf{M}\mathbf{Q}\mathbf{W}$ | Multi Quantum Well                                |

| MS                               | Metal-Semiconductor                               |

| MSM                              | Metal-Semiconductor-Metal                         |

| Ni                               | Nickel                                            |

| NiGe                             | Nickelgermanide                                   |

| NiGeSn                           | Nickelstanogermanide                              |

| NDR                              | Negative Differential Resistance                  |

| NIST                             | National Institute of Standards and Technology    |

| Р                                | Phosphorous                                       |

| PC                               | Personal Computer                                 |

| Pd                               | Palladium                                         |

| PECVD                            | Plasma Enhanced Chemical Vapor Deposition         |

| PGI                              | Peter Grünberg Institute                          |

| PL                               | Photoluminescence                                 |

| Pt                               | Platinum                                          |

| PVCR                             | Peak-to-Valley Current Ratio                      |

| QMSA                             | Quantitative Mobility Spectrum Analysis           |

| RBS               | Rutherford Backscattering Spectrometry         |

|-------------------|------------------------------------------------|

| RCA               | Radio Corporation of America                   |

| $\mathbf{RF}$     | Radio Frequency                                |

| RIE               | Reactive Ion Etching                           |

| RPCVD             | Reduced Pressure Chemical Vapor Deposition     |

| RTA               | Rapid Thermal Annealing                        |

| SBH               | Schottky Barrier Height                        |

| $\mathbf{eSBH}$   | electron Schottky Barrier Height               |

| hSBH              | hole Schottky Barrier Height                   |

| SC-1              | Standard Clean 1                               |

| SC-2              | Standard Clean 2                               |

| sccm              | standard cubic centimeters per minute          |

| SEM               | Scanning Electron Microscopy                   |

| Si                | Silicon                                        |

| $\mathbf{SiGeSn}$ | Silicon Germanium Tin                          |

| ToF-SIMS          | Time of Flight Secondary Ion Mass Spectroscopy |

| Sn                | Tin                                            |

| SGIDS             | Stanogermanidation-Induced Dopant Segregation  |

| SRH               | Shockley-Read-Hall                             |

| SS                | Subthreshold Swing                             |

| SSE               | Solid State Electronics                        |

| STEM              | Scanning TEM                                   |

| SWIR           | Short Wavelength Infrared                                                                                                                                                                              |  |  |  |  |  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| TaN            | Tantalum Nitride                                                                                                                                                                                       |  |  |  |  |  |

| TAT            | Trap-Assisted Tunneling                                                                                                                                                                                |  |  |  |  |  |

| TBTDET         | $\label{eq:constraint} \begin{split} & {\rm Tris}({\rm diethylamido})(\textit{tert-butlyimino}){\rm tantalum} \\ & [(({\rm C}_2{\rm H}_5)_2{\rm N})_3({\rm C}_4{\rm H}_9{\rm N}){\rm Ta}] \end{split}$ |  |  |  |  |  |

| TCAD           | Technology Computer Aided Design                                                                                                                                                                       |  |  |  |  |  |

| TDMAH          | Tetrakis(Dimethylamino)Hafnium                                                                                                                                                                         |  |  |  |  |  |

| TED            | Transactions on Electron Devices                                                                                                                                                                       |  |  |  |  |  |

| TEM            | Transmission Electron Microscopy                                                                                                                                                                       |  |  |  |  |  |

| TEMAH          | Tetrakis Ethyl Methyl Amino Hafnium                                                                                                                                                                    |  |  |  |  |  |

| TFET           | Tunnel Field-Effect Transistor                                                                                                                                                                         |  |  |  |  |  |

| Ti             | Titanium                                                                                                                                                                                               |  |  |  |  |  |

| $\mathbf{TiN}$ | Titanium Nitride                                                                                                                                                                                       |  |  |  |  |  |

| TLM            | Transfer Length Method                                                                                                                                                                                 |  |  |  |  |  |

| TMA            | Trimethylaluminium                                                                                                                                                                                     |  |  |  |  |  |

| WKB            | Wentzel-Kramers-Brilloin                                                                                                                                                                               |  |  |  |  |  |

| XPS            | X-ray Photoelectron Spectroscopy                                                                                                                                                                       |  |  |  |  |  |

| XRD            | X-ray Diffraction                                                                                                                                                                                      |  |  |  |  |  |

| XTEM           | Cross sectional TEM                                                                                                                                                                                    |  |  |  |  |  |

| Symbol            | Unit                               | Description                                         |

|-------------------|------------------------------------|-----------------------------------------------------|

| A                 | $m^2$                              | Area                                                |

| $\mathcal{A}$     | $\mathrm{cm}^{-3}\mathrm{s}^{-1}$  | Parameter for BTBT                                  |

| $A^*$             | $A/(cm^2K^2)$                      | Effective Richardson constant                       |

| $A^{**}$          | $A/(cm^2K^2)$                      | Reduced effective Richardson constant               |

| ${\mathcal B}$    | MV/cm                              | Parameter for BTBT                                  |

| C                 | $\mu { m F}/{ m cm}^2$             | Capacitance per unit area                           |

| $C_{\rm c}$       | $\mu { m F}/{ m cm}^2$             | Series resistance corrected capacitance             |

| $C_{\rm D}$       | $\mu { m F}/{ m cm}^2$             | Semiconductor depletion capacitance                 |

| $C_{\rm FB}$      | $\mu { m F}/{ m cm}^2$             | Flatband capacitance                                |

| $C_{\rm m}$       | $\mu { m F}/{ m cm}^2$             | Measured gate area normalized capacitance           |

| $C_{\rm ma}$      | $\mu { m F}/{ m cm}^2$             | Gate area normalized capacitance measured in strong |

|                   |                                    | accumulation                                        |

| $C_{\mathrm{Ox}}$ | $\mu { m F}/{ m cm}^2$             | Oxide capacitance                                   |

| $C_{\mathrm{T}}$  | $\mu { m F}/{ m cm}^2$             | Trap capacitance                                    |

| $d_{\rm BTBT}$    | nm                                 | BTBT generation depth                               |

| $d_{\rm gen}$     | nm                                 | Generation length for TAT                           |

| $D_{\rm it}$      | $\mathrm{cm}^{-2}\mathrm{eV}^{-1}$ | Density of Interface Traps                          |

| $D_{\rm t}$       | $\rm cm^{-2} eV^{-1}$              | Trap density                                        |

| $E_{\rm a}$       | eV                                 | Activation energy                                   |

| $E_{\rm C}$       | eV                                 | Conduction band edge energy                         |

| $E_{\rm CL}$      | eV                                 | Energy of the L-valley                              |

| $E_{\rm C\Gamma}$ | eV                                 | Energy of the $\Gamma$ -valley                      |

| $E_{\rm F}$       | eV                                 | Fermi level                                         |

| $E_{\rm F,m}$     | eV                                 | Metal Fermi energy                                  |

| $E_{\rm F,s}$     | eV                                 | Semiconductor Fermi level                           |

| $E_{\rm G}$       | eV                                 | Bandgap                                             |

| $E_{\rm i}$       | eV                                 | Intrinsic level                                     |

| $E_{\rm sp}$      | eV                                 | Energy of a spontaneously emitted photon            |

| $E_{\rm t}$       | eV                                 | Trap energy                                         |

#### List of symbols

| $E_{\rm TW}$                | eV                             | BTBT window                                        |

|-----------------------------|--------------------------------|----------------------------------------------------|

| $E_{\rm V}$                 | eV                             | Valence band edge energy                           |

| ε                           | V/m                            | Electrical field                                   |

| $\mathcal{E}_{\mathrm{Bi}}$ | V/m                            | Built in electrical field                          |

| f                           | Hz                             | Frequency                                          |

| $f_{\rm peak}$              | Hz                             | Frequency of $(G_{\rm P}/\omega)_{\rm max.}$       |

| $f_{ m t}$                  | Hz                             | Transition frequency                               |

| $f_{ m c}$                  |                                | Conduction band Fermi distribution                 |

| $f_{\rm v}$                 |                                | Valence band Fermi distribution                    |

| G                           | $\mu \mathrm{S}/\mathrm{cm}^2$ | Conductance per unit area                          |

| $G_{\rm c}$                 | $\mu { m S/cm^2}$              | Series resistance corrected parallel conductance   |

| $G_{\rm m}$                 | $\mu { m S/cm^2}$              | Measured gate area normalized parallel conductance |

| $G_{\rm ma}$                | $\mu { m S/cm^2}$              | Gate area normalized parallel conductance measured |

|                             |                                | in strong accumulation                             |

| $G_{\rm t}$                 | $\mu { m S/cm^2}$              | Trap conductance                                   |

| h                           | $_{\rm Js}$                    | Planck constant                                    |

| $\hbar = \frac{h}{2\pi}$    | $_{\rm Js}$                    | Reduced Planck constant                            |

| ${\cal H}$                  |                                | Hamilton Operator                                  |

| Ι                           | А                              | Electrical current                                 |

| $I_{\rm DS}$                | $\mu A/\mu m$                  | Width normalized Drain-Source current              |

| $I_{\rm TAT}$               | $\mu A/\mu m$                  | Width normalized excess current                    |

| $I_{\rm G}$                 | $\mu A/\mu m$                  | Width normalized gate leakage current              |

| J                           | $A/cm^2$                       | Current density                                    |

| $J_{ m F}$                  | $A/cm^2$                       | Forward bias current density                       |

| $J_{ m G}$                  | $A/cm^2$                       | Gate leakage current density                       |

| $J_{ m R}$                  | $A/cm^2$                       | Reverse bias current density                       |

| $J_{\rm BTBT}$              | $\rm A/cm^2$                   | BTBT current density                               |

| $J_{\rm TAT}$               | $\rm A/cm^2$                   | Excess current density                             |

| $J_{\rm thermal}$           | $A/cm^2$                       | Thermal current density                            |

| k                           | 1/m                            | Lattice vector                                     |

| $k_{\rm B}$                 | J/K                            | Boltzmann constant                                 |

| L                           | m                              | Length                                             |

| $\mathcal{M}_{c}$          | $\mathrm{cm}^{-3}\mathrm{eV}^{-1}$ | Conduction band density of states                                |

|----------------------------|------------------------------------|------------------------------------------------------------------|

| $\mathcal{M}_{\mathrm{v}}$ | $cm^{-3}eV^{-1}$                   | Valence band density of states                                   |

| · •                        | kg                                 | Free electron mass                                               |

| $m_e$<br>$m^*$             | 0                                  | Effective carrier mass in a semiconductor                        |

|                            | m <sub>e</sub>                     | Effective electron mass                                          |

| $m_{ m e}^*$               | me                                 |                                                                  |

| $m_{ m h}^*$               | me                                 | Effective hole mass                                              |

| $m^*_{ m HH}$              | $m_e$                              | Heavy hole effective mass                                        |

| $m^*_{ m LH}$              | $m_e$                              | Light hole effective mass                                        |

| $m_{ m L}^*$               | $m_e$                              | L-valley electron effective mass                                 |

| $m_{ m T}^*$               | $m_e$                              | Tunneling effective mass                                         |

| $m_{\Gamma}^*$             | me                                 | $\Gamma$ -valley electron effective mass                         |

| n                          | $\mathrm{cm}^{-3}$                 | Electron carrier density                                         |

| $n_{ m i}$                 | $\mathrm{cm}^{-3}$                 | Intrinsic carrier concentration of an undoped                    |

|                            |                                    | semiconductor                                                    |

| $n_{\rm ps}$               | $\mathrm{cm}^{-3}$                 | Electron carrier density in space charge region                  |

|                            |                                    | (for $p$ -type)                                                  |

| $n_{ m po}$                | $\mathrm{cm}^{-3}$                 | Equilibrium electron carrier density (for $n$ -type)             |

| $n_{\rm 2D}$               | $\mathrm{cm}^{-2}$                 | Sheet carrier density                                            |

| N                          | $\mathrm{cm}^{-3}$                 | Doping concentration $(p \text{ or } n)$                         |

| $N_{\mathrm{A}}$           | $\mathrm{cm}^{-3}$                 | Acceptor concentration                                           |

| $N_{\rm D}$                | $\mathrm{cm}^{-3}$                 | Donator concentration                                            |

| $N_{ m t}$                 | $\mathrm{cm}^{-3}\mathrm{eV}^{-1}$ | Trap density (for a certain energy)                              |

| p                          | $\mathrm{cm}^{-3}$                 | Hole carrier density                                             |

| $p_{\rm ps}$               | $\mathrm{cm}^{-3}$                 | Hole carrier density in space charge region (for <i>p</i> -type) |

| $p_{ m po}$                | $\mathrm{cm}^{-3}$                 | Equilibrium hole carrier density (for $p$ -type)                 |

| q                          | As                                 | Elementary charge                                                |

| q                          | 1/m                                | Phonon                                                           |

| $r_{ m H}$                 | ·                                  | Hall factor                                                      |

| R                          | Ω                                  | Electrical resistance                                            |

| $R_{\rm H}$                | Ω                                  | Hall resistance                                                  |

| $R_{\rm S}$                | Ω                                  | Series resistance                                                |

| $R_{ m Sht}$               | Ω                                  | Shunt resistance                                                 |

|                            |                                    |                                                                  |

| $\mathcal{R}_{	ext{sp}}$ | $eV^{-1}s^{-1}m^{-3}$            | Spectral spontaneous emission rate             |

|--------------------------|----------------------------------|------------------------------------------------|

| $\mathcal{R}_{	ext{t}}$  | $\mathrm{s}^{-1}\mathrm{m}^{-3}$ | TAT net generation rate                        |

| $R_{\Box}$               | Ω                                | Sheet resistance                               |

| SS                       | $\mathrm{mV/dec}$                | Subthreshold Swing                             |

| $t_{\rm GeSn}$           | nm                               | GeSn epilayer thickness                        |

| $t_{\rm Ox}$             | nm                               | Oxide thickness                                |

| T                        | Κ                                | Temperature                                    |

| $T_{\rm BTBT}$           |                                  | Tunneling probability                          |

| $v_{\rm D}$              | m/s                              | Drift velocity                                 |

| $v_{\rm G}$              | m/s                              | Group velocity                                 |

| $V_{\rm BD}$             | V                                | Breakdown voltage                              |

| $V_{ m F}$               | V                                | Forward bias                                   |

| $V_{\rm FB}$             | V                                | Flatband voltage                               |

| $V_{\rm G}$              | V                                | Gate voltage                                   |

| $V_{\rm D}$              | V                                | Drain voltage                                  |

| $V_{\rm DS}$             | V                                | Drain-Source voltage                           |

| $V_{\rm H}$              | V                                | Hall voltage                                   |

| $V_{\rm R}$              | V                                | Reverse bias                                   |

| $V_{\rm S}$              | V                                | Source voltage                                 |

| W                        | m                                | Width                                          |

| $W_{\rm D}$              | nm                               | Depletion width                                |

| $\alpha$                 |                                  | Diode ideality factor                          |

| $\beta$                  |                                  | Image force and static barrier lowering factor |

| $\gamma$                 |                                  | Minority carrier injection ratio               |

| $\Delta E$               | eV                               | Energy range for TAT                           |

| $\epsilon$               | %                                | Strain                                         |

| $\varepsilon_0$          | As/Vm                            | Vacuum permittivity                            |

| $\varepsilon_{\rm s}$    |                                  | Relative permittivity of the semiconductor     |

| $\varepsilon_{\rm Ox}$   |                                  | Relative permittivity of the gate oxide        |

| $\lambda$                | nm                               | Characteristic scaling length                  |

| $\kappa$                 |                                  | Same as $\varepsilon_{\text{Ox}}$              |

| $\mu$                    | $\mathrm{cm}^2/\mathrm{Vs}$      | Charge carrier mobility                        |

| $\nu$ $1/s$ Photon frequency $\rho_c$ $\Omega  \mathrm{cm}^2$ Specific contact resistivity $\sigma$ $1/(\Omega \mathrm{m})$ Conductivity $\sigma_{\mathrm{t}}$ $\mathrm{m}^2$ Trap capture cross-section $\tau_{\mathrm{m}}$ sScattering time $\tau_{\mathrm{n}}$ sMinority carrier life-time (electrons) $\tau_{\mathrm{p}}$ sMinority carrier life-time (holes) |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| $ \begin{array}{cccc} \sigma & 1/(\Omega m) & Conductivity \\ \sigma_t & m^2 & Trap capture cross-section \\ \tau_m & s & Scattering time \\ \tau_n & s & Minority carrier life-time (electrons) \\ \end{array} $                                                                                                                                                 |    |

| $ \begin{array}{cccc} \sigma_{t} & m^{2} & Trap \ capture \ cross-section \\ \tau_{m} & s & Scattering \ time \\ \tau_{n} & s & Minority \ carrier \ life-time \ (electrons) \\ \end{array} $                                                                                                                                                                     |    |

| $\tau_{\rm m}$ sScattering time $\tau_{\rm n}$ sMinority carrier life-time (electrons)                                                                                                                                                                                                                                                                            |    |

| $\tau_{\rm n}$ s Minority carrier life-time (electrons)                                                                                                                                                                                                                                                                                                           |    |

|                                                                                                                                                                                                                                                                                                                                                                   |    |

| $\tau_{\rm p}$ s Minority carrier life-time (holes)                                                                                                                                                                                                                                                                                                               |    |

| $q\phi_{Bn0}$ eV Ideal electron Schottky barrier height                                                                                                                                                                                                                                                                                                           |    |

| $q\phi_{Bp0}$ eV Ideal hole Schottky barrier height                                                                                                                                                                                                                                                                                                               |    |

| $q\phi_B$ eV Effective Schottky barrier height $(p \text{ or } n)$                                                                                                                                                                                                                                                                                                |    |

| $q\phi_{B0}$ eV Zero bias effective Schottky barrier height $(p \text{ or } n)$                                                                                                                                                                                                                                                                                   |    |

| $q\phi_m$ eV Workfunction of a metal                                                                                                                                                                                                                                                                                                                              |    |

| $q\phi_{\rm n}$ eV Distance of semiconductor Fermi level to conduction                                                                                                                                                                                                                                                                                            |    |

| band edge (for $n$ -type)                                                                                                                                                                                                                                                                                                                                         |    |

| $q\phi_{\rm p}$ eV Distance of semiconductor Fermi level to valence band                                                                                                                                                                                                                                                                                          | d  |

| edge (for $p$ -type)                                                                                                                                                                                                                                                                                                                                              |    |

| $\Phi$ V Potential                                                                                                                                                                                                                                                                                                                                                |    |

| $q\chi_{\rm S}$ eV Semiconductor electron affinity                                                                                                                                                                                                                                                                                                                |    |

| $q\psi_{\rm Bi}$ eV Build in potential                                                                                                                                                                                                                                                                                                                            |    |

| $q\psi_{\rm Bp}$ eV Distance of semiconductor Fermi level to intrinsic level                                                                                                                                                                                                                                                                                      | el |

| (for $p$ -type)                                                                                                                                                                                                                                                                                                                                                   |    |

| $q\psi_{\rm S}$ eV Semiconductor band bending (surface potential)                                                                                                                                                                                                                                                                                                 |    |

| $q\psi_{\rm S0}$ eV Surface potential in a TFET for zero gate bias as a                                                                                                                                                                                                                                                                                           |    |

| function of $V_{\rm D}$                                                                                                                                                                                                                                                                                                                                           |    |

## 1 Introduction

THE undamped trend of functionalization, diversification, omnipresence and performance enhancement in Information & Communication Technology (ICT) also known as the Internet of Things (IoT) lead and continuously leads to an enormous increase of data traffic. For example in 2015 the global internet traffic of 638 exabyte  $(6.38 \cdot 10^{20} \text{ bytes/year})$  was equivalent to  $26 \times$  the volume of the entire global internet in 2005. Until the end of 2020 this traffic is projected to reach  $2.3 \cdot 10^{21}$  bytes/year [1]. At that same time only 29% of the total internet traffic will be due to Personal Computers (PC)s while 44 % of all network devices are projected to be mobile connected [1]. Even though the continuous shrinking of conventional Complimentary Metal-Oxide-Semiconductor (CMOS) transistors - known as Moore's law - strongly reduced the power per computing operation, it is evident that the overall power consumption of ICT drastically increased within the last years [2]. More than that, with the release of the 7 nm node with 15 nm transistor gate length end of 2016 [3,4] classic Si CMOS technology approaches its physical limits. This triggers materials innovation and a paradigm shift towards diversification and application driven computer architectures summarized under the term More than Moore technologies. Especially quantum computing [5] and brain inspired/neuromorphic computing [6] are promising approaches for certain objectives as efficient factorization, search algorithms or pattern recognition.

However the predominant portion of integrated systems in the IoT will still rely on classical logic operations that demand significant reduction in power consumption both at transistor level and for interconnects. Material innovation towards higher transistor channel mobilities is an evident but not trivial approach to maintain transistors oncurrent and switching speed while reducing the supply voltage. Strain engineering was the first approach to improve mobility in Si CMOS transistors. As this potential is exploited sustained effort is placed on the co-integration of Ge and III-V materials on the well established Si platform enabling higher channel mobility to further reduce power consumption on the transistor level [7]. Also novel device concepts are intensively studied that enable a steeper transition between off and on-state than physically achievable with a classical Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET) and thereby allow significant supply voltage reduction well below 0.5 V. Among several approaches [8–11] the Tunnel Field-Effect Transistor (TFET) is one of the most prominent candidates for future energy efficient computing [10, 12]. At the same time ICT dissipates significant amount of energy in electrical interconnects [13]. Here a smart solution is the on-chip (monolithic) integration of a light source for optical-based on-chip and chip-to-chip communication [14]. Since Si is known to be an inefficient light emitter this again suggests the integration of III-V materials on Si which faces challenges though due to dissimilar mechanical properties, material quality and cost.

An alternate material approach is the novel all-group IV (Si)GeSn semiconductor family based on *Tin* (Sn). It was experimentally demonstrated that *Germanium Tin* (GeSn) is a direct bandgap semiconductor and for the first time allowed lasing in a group IV material [15], thereby unambiguously proofing its suitability for photonics with possible and starting from 2011 also partially demonstrated applications in *Light Emitting Diodes* (LED)s [16–19], detectors [20], gas sensors [21] or solar cells [22].

While the boon of a direct and engineered bandgap GeSn is evident for Si based photonics such alloys may also serve as a performance booster for electronic devices. The low and direct bandgap properties with a small conduction band effective mass suggest GeSn to be a promising material for TFETs allowing high *Band-to-Band Tunneling* (BTBT) rates [23,24]. Also enhanced electron mobilities are projected [25,26] and even proofed within the scope of this work. Last but not least the Si/Sn content depending lattice constant of SiGeSn can be utilized for strain engineering as source/drain stressors [27,28] or directly as strained channel [29]. First GeSn MOSFETs [30,31] and even TFETs were experimentally demonstrated within the last few years, starting in 2011 [32–37].

In short GeSn merges superior properties resulting from III-Vs direct bandgap with the intrinsic Si-compatibility of group IV materials allowing straight forward integration on the established Si platform. Epitaxially grown GeSn with high quality and especially direct bandgap is available since recent years only, enabling the unique possibility to study fundamental physical properties of a novel material. On the other hand all necessary steps to fabricate GeSn-based devices need to be developed or adapted and validated.

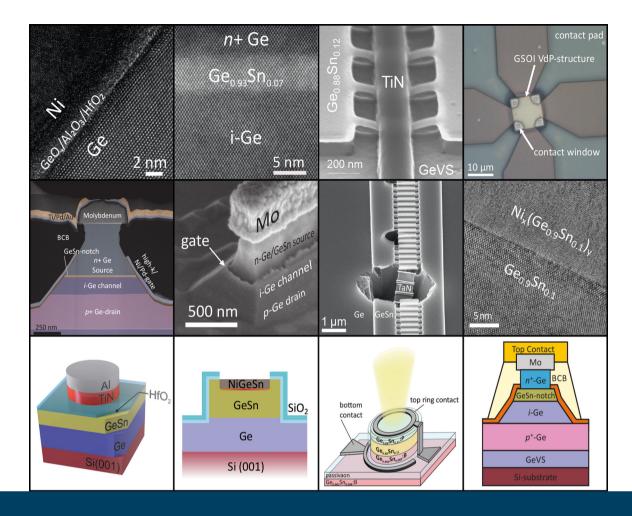

$\mathbf{I}^{\mathrm{N}}$  this work the potential of GeSn for electronic applications is studied from fundamental material properties to complete devices including tunnel diodes, LEDs, MOSFETs and TFETs<sup>1</sup>. The thesis contains nine chapters. Relevant background and a brief literature overview is provided at the beginning of each of the seven main chapters. Following this preface, a general introduction into the (Si)GeSn material system is provided in CHAPTER 2. Subsequently individual modules that are essential for each transistor, such as surface manipulation, contact formation and high- $\kappa$ /metal gate stack are studied in the CHAPTERS 3, 4 and 5, respectively. Special emphasis is placed on the characterization of high- $\kappa$ /metal gate stacks on (Si)GeSn, particularly on the correlation of bandgap and minority carrier response. In CHAPTER 6 p-i-n diodes are evaluated both as LED and as tunnel diodes, the fundamental building block of any TFET. In this context the focus is placed on the capability of GeSn to enable direct BTBT. These studies lead to the experimental demonstration of vertical GeSn/Ge heterojunction TFETs in CHAPTER 7 in conjunction with a comprehensive analysis of the dominant transport mechanisms. In the last main chapter, CHAPTER 8 Hall measurements are presented to evaluate carrier mobility enhancement, carrier density and dominant scattering mechanism in GeSn. MOSFETs, also fabricated within the scope of this work will be not treated here. To that end it shall be referred to Ref. [26].

Finally CHAPTER 9 provides a brief summary of the present work and concludes its key results while giving an outlook of this fascinating emerging material system.

<sup>&</sup>lt;sup>1</sup>Semiconductor processing and characterization were primarily conducted at PGI9 and HNF [38] of the FZ-Jülich, Germany. Experiments presented in CHAPTER 7 and partially in CHAPTER 5 & 6 were conducted during a research stay at the Suman Datta group at the University of Notre Dame, IN, USA.

### $2 \quad | \quad \text{The (Si)GeSn material system}$

| 2.1. | GeSn effective mass and mobility | • | • | • | <br>• | • | • | • | • | • | · | • | • | • | 8  |

|------|----------------------------------|---|---|---|-------|---|---|---|---|---|---|---|---|---|----|

| 2.2. | Thermal stability and doping     |   |   |   |       |   |   | • |   |   |   | • |   |   | 10 |

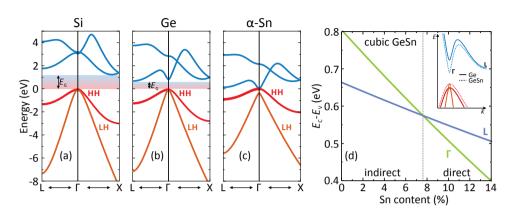

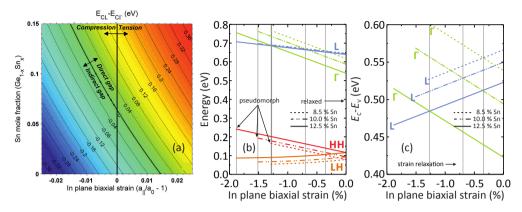

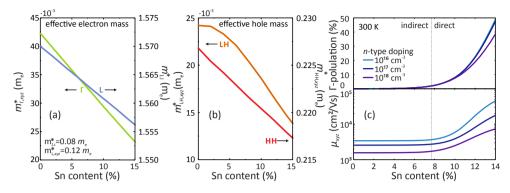

I<sup>N</sup> this chapter fundamental properties of the novel (Si)GeSn semiconductor material system are introduced, while reviewing the key step stones of (Si)GeSn's rapid development within the recent past. First, changes in electronic band structure, effective mass and mobility are discussed, arising from strain and Sn/Si incorporation in the Ge-lattice. In the second part thermal stability and doping, both relevant for (Si)GeSn device fabrication are outlined.