# **Strained Silicon-Germanium / Silicon Heterostructure Tunnel FETs for Low Power Applications**

Sebastian Blaeser

Schlüsseltechnologien/ Key Technologies Band/Volume 124 ISBN 978-3-95806-135-4

Forschungszentrum Jülich GmbH Peter Grünberg Institute Semiconductor Nanoelectronics (PGI-9)

## Strained Silicon-Germanium/Silicon Heterostructure Tunnel FETs for Low Power Applications

Sebastian Blaeser

Schriften des Forschungszentrums Jülich Reihe Schlüsseltechnologien / Key Technologies Bibliographic information published by the Deutsche Nationalbibliothek. The Deutsche Nationalbibliothek lists this publication in the Deutsche Nationalbibliografie; detailed bibliographic data are available in the Internet at http://dnb.d-nb.de.

Publisher and Forschungszentrum Jülich GmbH

Distributor: Zentralbibliothek

52425 Jülich

Tel: +49 2461 61-5368 Fax: +49 2461 61-6103

Email: zb-publikation@fz-juelich.de

www.fz-juelich.de/zb

Cover Design: Grafische Medien, Forschungszentrum Jülich GmbH

Printer: Grafische Medien, Forschungszentrum Jülich GmbH

Copyright: Forschungszentrum Jülich 2016

Schriften des Forschungszentrums Jülich Reihe Schlüsseltechnologien / Key Technologies, Band / Volume 124

D 82 (Diss. RWTH Aachen University, 2016)

ISSN 1866-1807 ISBN 978-3-95806-135-4

The complete volume is freely available on the Internet on the Jülicher Open Access Server (JuSER) at www.fz-juelich.de/zb/openaccess.

## **Abstract**

Scaling of nanoelectronics consequently comes along with power consumption in integrated circuits, either in terms of static power consumption  $P_{\text{static}}$  due to different leakage contributions or in terms of dynamic power consumption  $P_{\text{dynamic}}$ , accounting for the power density arising in an integrated circuit and thus, restricting an arbitrary miniaturization. Since dynamic power consumption scales with the second power of the supply voltage,  $P_{\rm dynamic} \propto V_{\rm DD}^2$ , a reduction of the latter represents a promising approach in order to enable low power electronics. However, a reduction of the supply voltage  $V_{\mathrm{DD}}$  inevitably results in an either lowered on-current  $I_{\rm on}$  or increased off-current  $I_{\rm off}$  of a metal-oxide-semiconductor field-effect transistor (MOSFET). A reduction of the subthreshold swing SS of the transistor as a measure of the steepness of its transition from the off- to the on-state in turn allows for a reduction of the supply voltage  $V_{\rm DD}$  without accepting an either lowered on-current  $I_{\rm on}$  or increased off-current  $I_{\rm off}$ . However, since charge transport in a MOSFET is based on thermionic emission over a potential barrier due to a broadened FERMI distribution function, its subthreshold swing SS is limited to  $60 \,\mathrm{mV/dec}$  at room temperature  $T = 300 \,\mathrm{K}$ . In order to overcome this inherent limitation of a MOSFET and allow for a smaller subthreshold swing SS, the tunnel field-effect transistor (TFET) has been suggested as a promising alternative due to its charge transport realized by means of quantum mechanical band-to-band tunneling (BTBT).

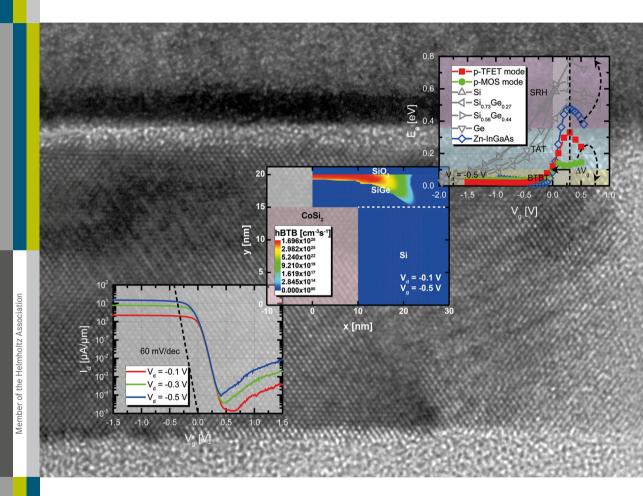

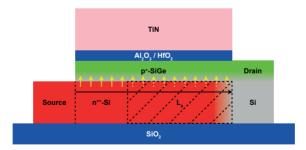

Within the framework of this thesis, two different proposals of a TFET device concept allowing for low power applications are investigated. As a first approach, a vertical Silicon-Germanium/Silicon (SiGe/Si) heterostructure TFET is considered which makes use of strained SiGe as a material with smaller band gap  $E_{\rm g}$  at the source tunnel junction in order to increase the probability for BTBT while suppressing the ambipolar switching characteristics in parallel due to the use of Si with its higher band gap  $E_{\rm g}$  as compared to SiGe at the drain tunnel junction, thus enabling a heterostructure device concept. As a second approach, a planar SiGe/Si heterostructure TFET is presented which not only makes use of strained SiGe as a material with smaller band gap  $E_{\rm g}$  at the source tunnel junction, but also benefits from a selective and self-adjusted silicidation in combination with a counter doped pocket at the source tunnel junction in order to enable line tunneling aligned with the gate electric field lines in an enlarged area directly underneath the gate. In addition, for both types of TFETs, technology computer aided design (TCAD) simulations are consulted in order to evaluate the respective experimental results as well as to illustrate potential improvements of each device concept.

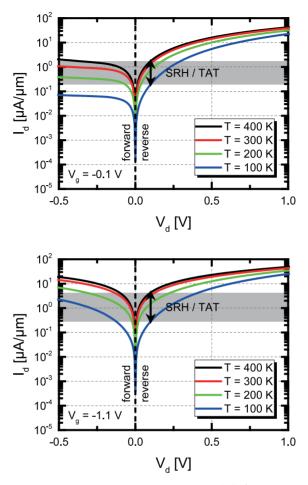

However, the vertical SiGe/Si heterostructure n-TFET suffers from a high subthreshold swing SS, a weak onset of the drain current  $I_{\rm d}$  with a pronounced S-shape as well as no visible saturation of the drain current  $I_{\rm d}$  due to a strong degradation of both tunnel junctions which may stem from poor electrostatic control caused by a defective interface between

semiconductor and high- $\kappa$  dielectrics as well as a pronounced surface roughness at the side walls of the fin, both favoring trap assisted tunneling (TAT). In addition, a pronounced ambipolar switching characteristics despite a heterostructure device concept becomes obvious, resulting from a much stronger contribution from TAT at the p<sup>++</sup>-SiGe tunnel junction as compared to the n<sup>+</sup>-Si tunnel junction, caused by the different chemical compositions of their respective interfacial oxide layers on the one hand and a much higher carrier concentration n within the SiGe layer on the other hand, scaling TAT.

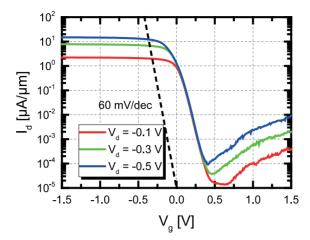

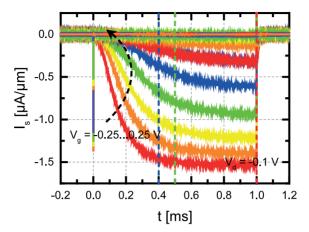

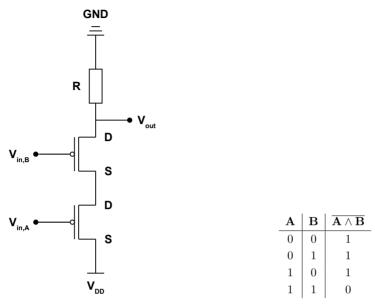

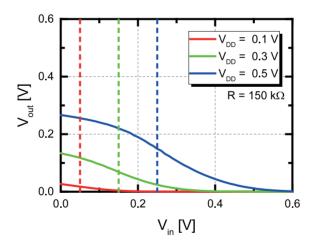

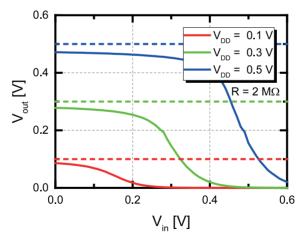

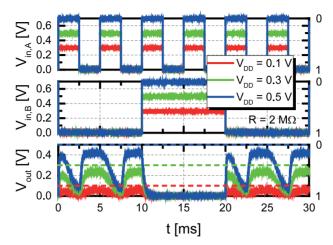

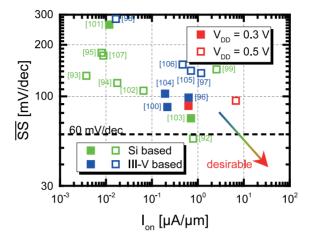

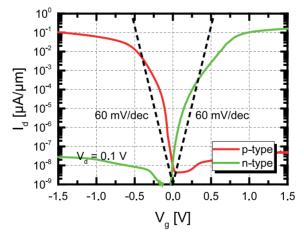

The planar SiGe/Si heterostructure p-TFET in turn reveals a high on-current  $I_{\text{on}}$  of  $6.7\,\mu\text{A/\mu}\text{m}$  at a supply voltage  $V_{\text{DD}}$  of  $0.5\,\text{V}$  in parallel with an average subthreshold swing SS of about 80 mV/dec over four orders of magnitude of drain current  $I_{\rm d}$ . Benchmarking the planar SiGe/Si heterostructure p-TFET with published state of the art TFETs in terms of on-current  $I_{\rm on}$  and average subthreshold swing SS over four orders of magnitude of drain current  $I_{\rm d}$  highlights the planar SiGe/Si heterostructure p-TFET outperforming other devices due to line tunneling aligned with the gate electric field lines being the dominant contribution to BTBT. Pulsed measurements allow for an identification of TAT being responsible for a degradation of the subthreshold swing SS. A sharp transition of the activation energy  $E_a$ from both Shockley-Read-Hall (SRH) and TAT to BTBT regime within a small gate voltage window  $\Delta V_{\sigma}$  of less than 0.4 V is revealed by means of low temperature T measurements, being much steeper as compared to state of the art Si, SiGe or Ge TFETs, thus facilitating high on-currents  $I_{\rm on}$  at a low supply voltage  $V_{\rm DD}$  and a constant subthreshold swing SS in parallel. Finally, p-logic Not-AND (NAND) operation is demonstrated by means of two planar SiGe/Si heterostructure p-TFETs connected in series, highlighting their ability for both low power electronics and logic applications down to ultra-low supply voltages  $V_{\mathrm{DD}}$ of 0.1 V.

## Kurzfassung

Skalierung in der Nanoelektronik geht unweigerlich einher mit dem Energieverbrauch eines integrierten Schaltkreises, sei es in Form von statischem Energieverbrauch  $P_{\text{static}}$  aufgrund unterschiedlicher Leckstrompfade oder in Form von dynamischem Energieverbrauch  $P_{\text{dynamic}}$ , der die Energiedichte in einem integrierten Schaltkreis bestimmt und so einer beliebigen Miniaturisierung Grenzen setzt. Da der dynamische Energieverbrauch mit dem Quadrat der Versorgungsspannung skaliert,  $P_{\rm dynamic} \propto V_{\rm DD}^2$ , stellt die Verringerung letzterer einen vielversprechenden Ansatz für die Realisierung elektronischer Anwendungen mit niedrigem Energieverbrauch dar. Jedoch hat eine Verringerung der Versorgungsspannung  $V_{\rm DD}$  unvermeidlich einen entweder reduzierten An-Strom  $I_{

m on}$  oder erhöhten Aus-Strom  $I_{

m off}$  eines Metall-Oxid-Halbleiter-Feldeffekttransistors (MOSFET) zur Folge. Dagegen ermöglicht eine Verringerung der Unterschwellenspannung SS des Transistors als Maeta für die Steilheit des Überganges zwischen Aus- und An-Zustand eine Verringerung der Versorgungsspannung  $V_{\rm DD}$ , ohne einen entweder reduzierten An-Strom  $I_{\rm on}$  oder erhöhten Aus-Strom  $I_{\rm off}$  in Kauf nehmen zu müssen. Da der Ladungstransport in einem MOSFET jedoch auf thermischer Emission über eine Potentialbarriere aufgrund einer aufgeweiteten FERMI Verteilungsfunktion beruht, ist seine Unterschwellenspannung SS auf  $60\,\mathrm{mV/dec}$  bei Raumtemperatur  $T=300\,\mathrm{K}$  begrenzt. Um diese inhärente Limitierung des MOSFETs zu überwinden und eine kleinere Unterschwellenspannung SS zu ermöglichen, wird der Tunnel-Feldeffekttransistor (TFET) als vielversprechende Alternative in Betracht gezogen, da dessen Ladungstransport auf quantenmechanischem Band-zu-Band Tunneln (BTBT) beruht.

Im Rahmen dieser Dissertation werden zwei unterschiedliche Vorschläge eines TFET-Bauelementkonzeptes unter dem Gesichtspunkt der Realisierung elektronischer Anwendungen mit niedrigem Energieverbrauch diskutiert. Als erster Ansatz wird ein vertikaler Silizium-Germanium/Silizium (SiGe/Si) Heterostruktur TFET untersucht, der von verspanntem SiGe als einem Material mit kleinerer Bandlücke  $E_g$  an der Tunnelverbindung der Quelle profitiert, um die Wahrscheinlichkeit für BTBT zu erhöhen, und gleichzeitig ein ambipolares Schaltverhalten unterdrückt, indem auf Si mit seiner größeren Bandlücke  $E_{\rm g}$  an der Tunnelverbindung der Senke zurückgegriffen wird, um auf diese Weise das Konzept einer Heterostruktur zu realisieren. Als zweiter Ansatz wird ein planarer SiGe/Si Heterostruktur TFET vorgestellt, der nicht nur auf verspanntes SiGe als ein Material mit kleinerer Bandlücke  $E_{\sigma}$  an der Tunnelverbindung der Quelle zurückgreift, sondern auch von einer selektiven und selbstjustierenden Silizidierung in Kombination mit einer gegendotierten Tasche an der Tunnelverbindung der Quelle profitiert, so dass Linientunneln in Richtung der elektrischen Feldlinien in einem vergrößerten Bereich direkt unterhalb der Steuerelektrode ermöglicht wird. Zusätzlich wird bei beiden TFETs auf Simulationen mittels technologischem, rechnerunterstütztem Konstruierens (TCAD) zurückgegriffen, um sowohl die jeweiligen experimentellen Ergebnisse beurteilen als auch Raum für potentielle Verbesserungen des jeweiligen Bauelementkonzeptes aufzeigen zu können.

Jedoch wird der vertikale SiGe/Si Heterostruktur n-TFET durch eine hohe Unterschwellenspannung SS, einen schwachen Anstieg des Senkenstromes  $I_{\rm d}$  mit einer ausgeprägten S-Form sowie keiner sichtbaren Sättigung des Senkenstromes  $I_{\rm d}$  limitiert, die auf eine starke Schädigung beider Tunnelverbindungen schließen lassen. Diese Schädigung beider Tunnelverbindungen kann sowohl von schwacher elektrostatischer Kontrolle aufgrund einer defektreichen Grenzfläche zwischen Halbleiter und high- $\kappa$  Dielektrikum als auch einer ausgebildeten Oberflächenrauheit an den Seitenwänden der Finne herrühren, so dass Tunneln über Störstellen (TAT) begünstigt wird. Zudem tritt ein ausgeprägtes ambipolares Schaltverhalten trotz des Konzepts einer Heterostruktur zu Tage, das in einem stärkeren Beitrag von TAT an der p<sup>++</sup>-SiGe Tunnelverbindung im Vergleich zur n<sup>+</sup>-Si Tunnelverbindung begründet liegt. Diese unterschiedlich starke Ausprägung von TAT lässt sich einerseits auf Unterschiede in der chemischen Zusammensetzung der jeweiligen Grenzflächenoxide und andererseits auf eine deutlich höhere Ladungsträgerkonzentration n innerhalb der SiGe-Schicht, die TAT skaliert, zurückführen.

Der planare SiGe/Si Heterostruktur p-TFET dagegen weist einen hohen An-Strom  $I_{\rm on}$  von  $6.7\,\mu\text{A}/\mu\text{m}$  für eine Versorgungsspannung  $V_{\text{DD}}$  von  $0.5\,\text{V}$  bei einer gleichzeitig mittleren Unterschwellenspannung SS von ungefähr  $80\,\mathrm{mV/dec}$  über vier Größenordnungen des Senkenstromes  $I_{\rm d}$  auf. Ein Vergleichsmaßstab des planaren SiGe/Si Heterostruktur p-TFETs mit publizierten TFETs nach aktuellem Stand der Technik in Bezug auf An-Strom  $I_{\rm on}$  und mittlere Unterschwellenspannung SS über vier Größenordnungen des Senkenstromes  $I_d$  offenbart die Überlegenheit des planaren SiGe/Si Heterostruktur p-TFETs, die im Linientunneln in Richtung der elektrischen Feldlinien als maßgeblichen Anteil zum BTBT begründet liegt. Mithilfe von Pulsmessungen kann TAT als Ursprung der erhöhten Unterschwellenspannung SS ausgemacht werden. Messungen bei tiefen Temperaturen T zeigen einen scharfen Übergang der Aktivierungsenergie  $E_{\rm a}$  von einem durch SHOCKLEY-READ-HALL (SRH) und TAT bestimmten Ladungstransport hin zu einem durch BTBT dominierten auf. Dieser Übergang wird in einer geringen Spannungsdifferenz  $\Delta V_{\rm g}$  der Steuerelektrode von weniger als  $0.4\,{\rm V}$ vollzogen, ist deutlich schärfer als bei anderen publizierten TFETs nach aktuellem Stand der Technik auf Basis von Si, SiGe oder Ge und begünstigt so hohe An-Ströme  $I_{\rm on}$  für niedrige Versorgungsspannungen  $V_{\rm DD}$  bei einer gleichzeitig konstanten Unterschwellenspannung SS. Abschließend wird ein Nicht-UND (NAND)-Gatter in p-Logik mithilfe von zwei in Serie verschalteten planaren SiGe/Si Heterostruktur p-TFETs realisiert, die damit ihre Eignung sowohl im Bereich elektronischer Anwendungen mit niedrigem Energieverbrauch als auch im Bereich von Logikanwendungen für Niedrigst-Versorgungsspannungen  $V_{\rm DD}$  von  $0.1\,\mathrm{V}$  unter Beweis stellen.

## **Contents**

| Κι<br>1<br>2 |                        | ssung                                    | iii |  |

|--------------|------------------------|------------------------------------------|-----|--|

| _            | Intr                   | roduction                                |     |  |

| 2            |                        |                                          | 1   |  |

|              | Theoretical Background |                                          |     |  |

|              | 2.1                    | Power Consumption in Integrated Circuits | 5   |  |

|              | 2.2                    | Physics of a MOSFET                      | 6   |  |

|              |                        | 2.2.1 Subthreshold Characteristics       | 7   |  |

|              | 2.3                    | Physics of a TFET                        | 9   |  |

|              |                        | 2.3.1 Kane's BTBT Model                  | 10  |  |

|              |                        | 2.3.2 Phonon Assisted BTBT               | 13  |  |

|              |                        | 2.3.3 Trap Assisted Tunneling            | 14  |  |

|              |                        | 2.3.4 Shockley-Read-Hall Recombination   | 16  |  |

|              |                        | 2.3.5 BTBT Mechanisms                    | 16  |  |

|              | 2.4                    | Design Considerations                    | 19  |  |

|              |                        | 2.4.1 Strain Engineering                 | 19  |  |

|              |                        | 2.4.2 EOT Scaling                        | 20  |  |

| 3            | Vert                   | tical SiGe/Si Heterostructure TFETs      | 25  |  |

|              | 3.1                    | Device Fabrication                       | 25  |  |

|              | 3.2                    | Device Characterization and Simulation   | 29  |  |

|              |                        | 3.2.1 Design Considerations              | 30  |  |

|              |                        | 3.2.2 DC Characteristics                 | 32  |  |

|              | 3.3                    | Summary and Discussion                   | 39  |  |

| 4            | Plar                   | nar SiGe/Si Heterostructure TFETs        | 41  |  |

|              | 4.1                    | Device Fabrication                       | 41  |  |

|              | 4.2                    | Device Characterization and Simulation   | 45  |  |

|              |                        | 4.2.1 DC Characteristics                 |     |  |

|              |                        | 4.2.2 Pulsed Measurements                | 64  |  |

|              |                        | 4.2.3 Low Temperature Analysis           | 67  |  |

|              |                        | 4.2.4 Logic Applications                 |     |  |

|              | 4.3                    | Summary and Discussion                   |     |  |

| 5            | Sun                    | nmary and Outlook                        | 85  |  |

| -            | 5.1                    | Design Optimizations                     |     |  |

| Bibliography         | i  |

|----------------------|----|

| List of Publications | xv |

**Curriculum Vitae**

Acknowledgments

## 1 Introduction

Whenever discussing scaling of nanoelectronics, Moore's empirical law from 1965 comes into play, suggesting a doubling of the number of transistors in a highly integrated circuit approximately every two years [1]. Due to steady progress in technology such as the introduction of high- $\kappa$  dielectrics in the 45 nm node in 2007 or the establishment of tri-gate fin-shaped field-effect transistors (FinFETs) as one step towards a three-dimensional device geometry in the 22 nm node in 2012 [2, 3], a premature ending of MOORE's prediction could be postponed over and over again and is valid for more than 50 years now. However, the more the dimensions of a metal-oxide-semiconductor field-effect transistor (MOSFET) as the key component of state of the art complementary metal-oxide-semiconductor (CMOS) technology shrink, the more contributions from leakage have to be taken into account, resulting in an increased static power consumption  $P_{\text{static}}$  of the integrated circuit and thus, degraded performance. Recently, Intel Corporation had to admit a slowdown of their cadence for technology transitions from two to two and a half years [4], resulting in a pronounced delay of their 10 nm node, first announced for 2015, now expected to show up in 2017. But on the contrary, a research alliance consisting of IBM, Globalfoundries and Samsung Corporation recently demonstrated a transistor incorporating a SiGe channel based on a 7 nm node utilizing extreme ultraviolet (EUV) lithography [5], once more postponing the limits of miniaturization and thus, further approaching the fundamental physical limits arising from quantum mechanics. Besides static power consumption  $P_{\text{static}}$  due to leakage contributions, dynamic power consumption  $P_{\text{dynamic}}$  must also be taken into account. Dense packaging of transistors in highly integrated circuits results in a considerable energy dissipation, making a restriction to an arbitrary miniaturization due to the limit of power density at a value of about 100 W/cm<sup>2</sup> much more probable than due to quantum mechanical effects [6]. Thus, a reduction of dynamic power consumption  $P_{\text{dynamic}}$  is indispensable if Moore's empirical law should not come to its end. Since dynamic power consumption scales with the second power of the supply voltage,  $P_{\rm dynamic} \propto V_{\rm DD}^2$ , a reduction of the latter represents a promising approach in order to enable low power electronics as one key requirement for both mobility and context-aware computing [7].

However, a reduction of the supply voltage  $V_{\rm DD}$  inevitably results in an either lowered oncurrent  $I_{\rm on}$  or increased off-current  $I_{\rm off}$  of the transistor. In this regard, a steeper transition from the off- to the on-state of a transistor may encounter this issue, thus bringing the subthreshold swing SS as a further figure of merit of a transistor into focus of consideration. Since charge transport in a MOSFET is based on thermionic emission over a potential barrier due to a broadened Fermi distribution function, its subthreshold swing SS is limited to  $60\,\mathrm{mV/dec}$  at room temperature  $T=300\,\mathrm{K}$ . In order to overcome this inherent limitation of a MOSFET and allow for a smaller subthreshold swing SS, new device concepts enabling a different mechanism of charge transport are needed. As one example of such a new device

concept, a Schottky barrier FET making use of impact ionization was recently experimentally demonstrated, allowing for a steep subthreshold swing SS far below 60 mV/dec [8]. However, Monte-Carlo simulations suggest a reduced switching speed in case of impact ionization due to a considerable time required in order to activate the process of carrier multiplication [9], claiming one major drawback of this novel device concept. With respect to the switching speed of a transistor, the tunnel field-effect transistor (TFET) as the most promising candidate for steep-slope devices comes into play. Charge transport in a TFET is not based on thermionic emission over but on quantum mechanical band-to-band tunneling (BTBT) through a potential barrier. The mechanism of BTBT was already experimentally observed and discussed by Esaki in narrow Ge p-n junctions in 1958 [10], exhibiting a negative differential resistance (NDR) at forward bias in the corresponding current-voltage (IV) characteristics, whereas first concepts for a transistor making use of BTBT date back to the late 1980s [11, 12]. Finally, the first TFET enabling a subthreshold swing SS below 60 mV/dec was experimentally realized in 2005 by means of a carbon nanotube transistor (CNT) [13], whereas the first TFET experimentally revealing a subthreshold swing SS below 60 mV/dec, but based on Si technology, came up in 2007 [14]. However, TFETs still suffer from low on-currents I<sub>on</sub> as compared to state of the art MOSFETs since the probability for BTBT yields to T(E) < 1 and thus, limits charge transport in a TFET, whereas in case of (short-channel) MOSFETs, charge transport within the channel can be assumed as ballistic, enabling a transmission probability T(E) = 1 [15]. One possibility to encounter the issue of low on-currents  $I_{\rm on}$  is the introduction of materials with small band gap  $E_{\rm g}$ such as strained Ge or GeSn which allow for a direct band gap  $E_g$  transition in order to enhance the transmission probability T(E). In this regard, the first TFET employing GeSn was experimentally realized in 2012 [16, 17], providing high on-currents I<sub>on</sub>, but still lacking in terms of a direct band gap E<sub>g</sub> transition due to the actual Sn content not exceeding the critical concentration yet. However, in 2015 GeSn finally was proven to enable a direct band gap  $E_{g}$  transition by means of lasing for Sn concentrations above 9% while maintaining a Si compatible technology [18]. In summary, the recent usability of TFETs as a replacement for MOSFETs is still quite limited, but theoretical calculations predict superior performance, higher switching speed and less power consumption of TFETs as compared to MOSFETs for supply voltages  $V_{\rm DD}$  below 0.5 V, revealing their promising potential even more pronounced in complementary metal-oxide-semiconductor (CMOS) logic applications [19, 20], but also in analog and sensor applications [21, 22, 23, 24].

Within the framework of this thesis, two different proposals of a TFET device concept allowing for low power applications will be investigated. As a first approach, a vertical Silicon-Germanium/Silicon (SiGe/Si) heterostructure TFET will be considered which makes use of strained SiGe as a material with smaller band gap  $E_{\rm g}$  at the source tunnel junction in order to increase the probability for BTBT while suppressing the ambipolar switching characteristics in parallel due to the use of Si with its higher band gap  $E_{\rm g}$  as compared to SiGe at the drain tunnel junction, thus enabling a heterostructure device concept. As a second approach, a planar SiGe/Si heterostructure TFET will be presented which not only makes use of strained SiGe as a material with smaller band gap  $E_{\rm g}$  at the source tunnel junction, but also benefits from a selective and self-adjusted silicidation in combination with a counter doped pocket at the source tunnel junction in order to enable line tunneling aligned with the gate electric field lines in an enlarged area directly underneath the gate. In

addition, for both types of TFETs, technology computer aided design (TCAD) simulations will be consulted in order to evaluate the respective experimental results as well as illustrate potential improvements of each device concept.

The content of this thesis is divided into five chapters. Subsequent to this introductory chapter, chapter 2 provides the theoretical background which is needed to describe the physics of the experimental work presented in this thesis, highlighting the different working principles of a MOSFET and a TFET respectively as well as discussing strain engineering and equivalent oxide thickness (EOT) scaling as two possibilities in order to improve subthreshold swing SS and on-current  $I_{\rm on}$  of a TFET. The vertical SiGe/Si heterostructure n-TFET will be introduced in chapter 3, first motivating this device concept by means of TCAD simulations, then presenting the experimental results obtained by direct current (DC) characterization. Chapter 4 presents the experimental results obtained from the planar SiGe/Si heterostructure p-TFET. Besides DC characterization, pulsed measurements and low temperature Tanalysis are performed in order to describe the physics emerging in this TFET structure. TCAD simulations assist in evaluating the experimental results and identifying critical process parameters. In addition, as a first step towards logic applications, a Not-AND (NAND) gate is presented, realized by means of p-TFET logic. Finally, chapter 5 concludes by summarizing the different results derived within the framework of this thesis and by giving an outlook by means of TCAD simulations for an optimized TFET device concept based on the planar SiGe/Si heterostructure p-TFET in order to demonstrate TFETs as a fierce competitor of MOSFETs in terms of low power electronics as well as low power CMOS logic applications.

## 2 Theoretical Background

This chapter provides the theoretical background which is needed in order to describe the physics of the experimental work presented in this thesis. At first, basic principles concerning power consumption in integrated circuits are highlighted in order to motivate the focus of this thesis on low power electronics. The MOSFET as the key component of state of the art CMOS technology is discussed, briefly deriving its subthreshold characteristics. Subsequently, the TFET as one candidate to overcome the inherent limitations of a MOSFET is introduced. Kane's BTBT model as well as different BTBT mechanisms and additional properties emerging in a TFET are deduced and discussed in order to describe its physics. Finally, strain engineering and EOT scaling as two possible techniques in order to optimize design and operation of a TFET are considered.

#### 2.1 Power Consumption in Integrated Circuits

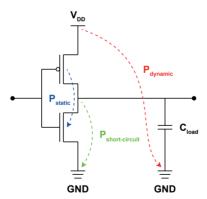

Power consumption in integrated circuits arises from dynamic power  $P_{\rm dynamic}$ , short-circuit power  $P_{\rm short-circuit}$  and static power  $P_{\rm static}$  as three independent contributions [25]. Figure 2.1.1 sketches these different components of power consumption in an integrated circuit. Dynamic power  $P_{\rm dynamic}$  and short-circuit power  $P_{\rm short-circuit}$  are also known as the switching power of an integrated circuit. Both are consumed whenever transistors change their logic

Figure 2.1.1: Schematic illustration of the different contributions to power consumption arising in integrated circuits. Dynamic power  $P_{\rm dynamic}$  and short-circuit power  $P_{\rm short-circuit}$  are consumed when transistors change their logic state due to charging and discharging of load capacitors  $C_{\rm load}$  whereas static power  $P_{\rm static}$  in turn dissipates due to different leakage contributions.

state due to charging and discharging of load capacitors  $C_{\text{load}}$ . The dependency of the dynamic power  $P_{\text{dynamic}}$  on the supply voltage  $V_{\text{DD}}$  can be described as

$$P_{\text{dynamic}} = AC_{\text{load}}V_{\text{DD}}^2f, \qquad (2.1.1)$$

where A denotes the activity factor, ranging between 0 and 1, as a measure of the average switching activity in the integrated circuit and f is the corresponding switching frequency. Static power  $P_{\rm static}$  in turn dissipates due to different leakage contributions like reverse biased diode leakage, gate induced drain leakage, gate oxide tunneling and subthreshold leakage and depends linearly on the off-current  $I_{\rm off}$  of a transistor:

$$P_{\text{static}} = I_{\text{off}} V_{\text{DD}}. \tag{2.1.2}$$

The off-current  $I_{\text{off}}$  of a transistor in turn is mainly dominated by the subthreshold leakage. As a consequence, the dependency of the off-current  $I_{\text{off}}$  on the supply voltage  $V_{\text{DD}}$  can also be approximated by the subthreshold swing SS as a figure of merit of a transistor, allowing for the evaluation of the steepness of its transition from the off- to the on-state [15]:

$$SS \approx \frac{V_{\rm DD}}{\log\left(\frac{I_{\rm on}}{I_{\rm off}}\right)},$$

(2.1.3)

which is equivalent to

$$I_{\text{off}} = I_{\text{on}} \cdot 10^{-\frac{V_{\text{DD}}}{SS}}.$$

(2.1.4)

Equation (2.1.4) reveals an exponential increase of the off-current  $I_{\rm off}$  of a transistor for a reduction of the supply voltage  $V_{\rm DD}$  but keeping the on-current  $I_{\rm on}$  constant. This unfavorable behavior becomes visible in the corresponding transfer characteristics plotting the drain current  $I_{\rm d}$  of the transistor as a function of the gate voltage  $V_{\rm g}$  as illustrated in figure 2.1.2. A reduction of the supply voltage  $V_{\rm DD}$  without accepting an either lowered on-current  $I_{\rm on}$  or increased off-current  $I_{\rm off}$  can only be achieved by a smaller subthreshold swing SS enabling a sharper transition from the off- to the on-state of the transistor as already indicated in chapter 1.

### 2.2 Physics of a MOSFET

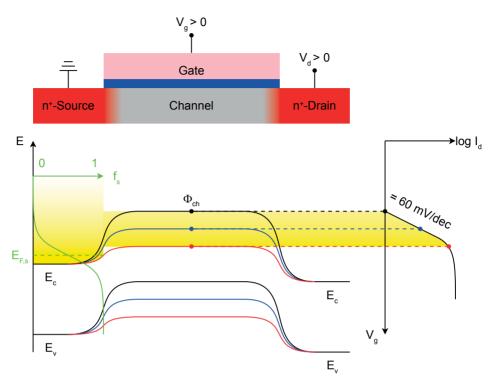

A MOSFET is a three-terminal device making use of the electrical field-effect in order to control charge transport from a doped source to a doped drain through an intrinsic channel. The electrostatic potential within the channel is controlled by an electrically isolated gate electrode determining the metal-oxide-semiconductor (MOS) capacitor of the transistor. Injection of carriers from the source into the channel is based on thermionic emission over a potential barrier due to a broadened FERMI distribution function in the source. In case of n-MOSFET operation as depicted in figure 2.2.1, source and drain are n<sup>+</sup>-doped and a positive voltage  $V_{\rm d}>0$  at the drain is applied, resulting in the conduction band edge of the channel being a potential barrier for electrons from source and drain respectively. By applying a positive voltage  $V_{\rm g}>0$  at the gate electrode, conduction and valence band in the channel are lowered in energy, allowing for charge transport between source and drain

Figure 2.1.2: Schematic illustration of the transfer characteristics of a MOSFET, revealing an exponential increase of the off-current  $I_{\rm off}$  of a transistor for a reduction of the supply voltage  $V_{\rm DD}$  but keeping the on-current  $I_{\rm on}$  constant. A reduction of the supply voltage  $V_{\rm DD}$  without either accepting a lowered on-current  $I_{\rm on}$  or increased off-current  $I_{\rm off}$  can only be achieved by a subthreshold swing SS below 60 mV/dec enabling a sharper transition from the off- to the on-state as provided in case of a TFET.

due to a reduced potential barrier, indicated by the surface potential  $\Phi_{\rm ch}$  of the channel. Thereby, the characteristics of the drain current  $I_{\rm d}$  depend exponentially on the broadening of the Fermi distribution function as deduced in chapter 2.2.1.

#### 2.2.1 Subthreshold Characteristics

Charge transport in a MOSFET can be derived by means of the LANDAUER-BÜTTIKER formalism interpreting conduction in a one-dimensional system as a transmission problem [26]:

$$I_{\rm d} = \frac{2e}{h} \int_{E} dE T(E) [f_{\rm s}(E) - f_{\rm d}(E)],$$

(2.2.1)

where e is the elementary charge, h the Planck constant,  $T\left(E\right)$  the transmission probability and  $f_{\rm s}$  and  $f_{\rm d}$  represent the Fermi distribution functions of source and drain respectively. As already suggested in chapter 1, assuming ballistic transport within the channel yields a transmission probability  $T\left(E\right)=1$  for energies  $E>\Phi_{\rm ch}$  greater than the surface potential of the channel and  $T\left(E\right)=0$  for all other energies, simplifying the integral in equation (2.2.1) to:

$$I_{\rm d} \approx \frac{2e}{h} \int_{\Phi_{\rm ch}}^{\infty} dE \left[ f_{\rm s} \left( E \right) - f_{\rm d} \left( E \right) \right].$$

(2.2.2)

Applying a positive drain voltage  $V_{\rm d}>0$  causes a lowered chemical potential  $\mu_{\rm d}<\mu_{\rm s}$  at the drain as compared to the source. As a consequence, the contribution of the Fermi

Figure 2.2.1: Schematic illustration of the band structure and corresponding transfer characteristics in case of n-MOSFET operation with source and drain being n<sup>+</sup>-doped and a positive voltage  $V_{\rm d}>0$  at the drain applied. By applying a positive voltage  $V_{\rm g}>0$  at the gate electrode, conduction and valence band in the channel are lowered in energy, allowing for charge transport based on thermionic emission between source and drain due to a reduced potential barrier, indicated by the surface potential  $\Phi_{\rm ch}$  of the channel.

distribution function of the drain becomes negligible with respect to that of the source,  $f_{\rm d} \ll f_{\rm s}$ , further simplifying the integral in equation (2.2.2) to:

$$I_{\rm d} \approx \frac{2e}{h} \int_{\Phi_{\rm ch}}^{\infty} \mathrm{d}E \, f_{\rm s} \left( E \right).$$

(2.2.3)

Assuming charge transport in the subthreshold regime of a MOSFET, the FERMI distribution function  $f_s$  of the source can be approximated by the BOLTZMANN distribution function since the surface potential of the channel is much greater than the chemical potential of the source,  $\Phi_{ch} \gg \mu_s$ , thus allowing for an analytic solution of the integral in equation (2.2.3):

$$I_{\rm d} \approx \frac{2e}{h} \int_{\Phi_{\rm ch}}^{\infty} {\rm d}E \, \exp\left(-\frac{E-\mu_{\rm s}}{k_{\rm B}T}\right) = \frac{2e}{h} k_{\rm B}T \exp\left(-\frac{\Phi_{\rm ch}-\mu_{\rm s}}{k_{\rm B}T}\right). \tag{2.2.4}$$

In order to evaluate the steepness of the transition of a MOSFET from its off- to its on-state, the subthreshold swing SS as one figure of merit is defined:

$$SS = \left[ \frac{\partial \log I_{\rm d}}{\partial V_{\rm g}} \right]^{-1} = \ln (10) \left[ \frac{1}{I_{\rm d}} \frac{\partial I_{\rm d}}{\partial V_{\rm g}} \right]^{-1} = \ln (10) \left[ \frac{1}{I_{\rm d}} \frac{\partial I_{\rm d}}{\partial \Phi_{\rm ch}} \frac{\partial \Phi_{\rm ch}}{\partial V_{\rm g}} \right]^{-1}, \tag{2.2.5}$$

where the first derivative of the drain current  $I_{\rm d}$  with respect to the surface potential  $\Phi_{\rm ch}$  of the channel can be calculated from equation (2.2.4). In order to evaluate the influence of the gate voltage  $V_{\rm g}$  on the surface potential  $\Phi_{\rm ch}$  of the channel, the gate capacitance C of a MOSFET has to be taken into account [6]:

$$C = \frac{\partial Q_{\text{depl}}}{\partial V_{\text{g}}} + \frac{\partial Q_{\text{inv}}}{\partial V_{\text{g}}} = \left(\frac{\partial Q_{\text{depl}}}{\partial \Phi_{\text{ch}}} + \frac{\partial Q_{\text{inv}}}{\partial \Phi_{\text{ch}}}\right) \frac{\partial \Phi_{\text{ch}}}{\partial V_{\text{g}}} = \frac{C_{\text{depl}} + C_{\text{inv}}}{e} \frac{\partial \Phi_{\text{ch}}}{\partial V_{\text{g}}}, \tag{2.2.6}$$

with  $C_{\text{depl}}$  and  $C_{\text{inv}}$  being the capacitances in depletion and inversion respectively. In addition, the gate capacitance C can be described as a combination of a parallel and a series connection of depletion, inversion and oxide capacitances  $C_{\text{depl}}$ ,  $C_{\text{inv}}$  and  $C_{\text{ox}}$ :

$$C = \frac{(C_{\text{depl}} + C_{\text{inv}}) C_{\text{ox}}}{C_{\text{ox}} + C_{\text{depl}} + C_{\text{inv}}}.$$

(2.2.7)

Combining equations (2.2.6) and (2.2.7) yields the dependency of the surface potential  $\Phi_{\rm ch}$  of the channel on the gate voltage  $V_{\sigma}$ :

$$\frac{\partial \Phi_{\rm ch}}{\partial V_{\rm g}} = e \left( \frac{C_{\rm ox}}{C_{\rm ox} + C_{\rm depl} + C_{\rm inv}} \right). \tag{2.2.8}$$

As a consequence, the subthreshold swing SS of a MOSFET becomes a function of the temperature T and the different contributions from the gate capacitance C:

$$SS = \ln(10) \frac{k_{\rm B}T}{e} \left( 1 + \frac{C_{\rm depl} + C_{\rm inv}}{C_{\rm ox}} \right).$$

(2.2.9)

Assuming the oxide capacitance is much greater than the capacitances in depletion and inversion,  $C_{\rm ox} \gg C_{\rm depl} + C_{\rm inv}$ , the lower limit of the subthreshold swing SS of a MOSFET at room temperature  $T=300\,\rm K$  can be calculated as:

$$SS = \ln{(10)} \frac{k_{\rm B}T}{e} \approx 60 \,\text{mV/dec.}$$

(2.2.10)

## 2.3 Physics of a TFET

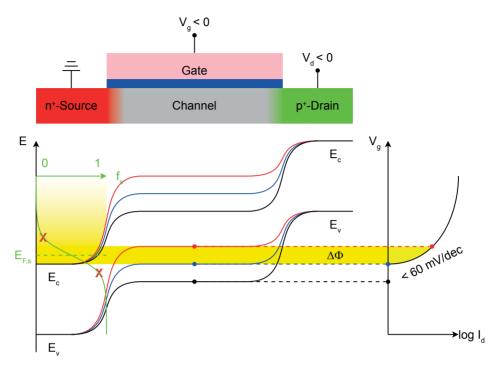

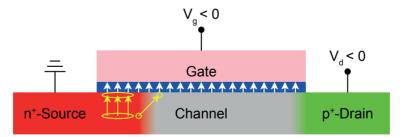

In contrast to a MOSFET, charge transport in a TFET is not based on thermionic emission over a potential barrier but on quantum mechanical BTBT. Therefore, source and drain are doped with opposite dopant species, resulting in a gated p-i-n structure which is operated in reverse bias conditions. In case of p-TFET operation as illustrated in figure 2.3.1, the source is n<sup>+</sup>-doped whereas the drain is p<sup>+</sup>-doped and a negative voltage  $V_{\rm d} < 0$  at the drain is applied, resulting in the conduction band edge of the channel being a potential

Figure 2.3.1: Schematic illustration of the band structure and corresponding transfer characteristics in case of p-TFET operation with the source being n<sup>+</sup>-doped, the drain being p<sup>+</sup>-doped and a negative voltage  $V_{\rm d} < 0$  at the drain applied. By applying a negative voltage  $V_{\rm g} < 0$  at the gate electrode, conduction and valence band in the channel are raised in energy, causing an energy overlap  $\Delta\Phi$  between the conduction band of the source and the valence band of the channel. This energy overlap  $\Delta\Phi$  defines the tunneling window for BTBT from the source into the channel.

barrier for electrons from the source and the valence band edge of the channel being a potential barrier for holes from the drain. By applying a negative voltage  $V_{\rm g} < 0$  at the gate electrode, conduction and valence band in the channel are raised in energy, causing an energy overlap  $\Delta\Phi$  between the conduction band of the source and the valence band of the channel. This energy overlap  $\Delta\Phi$  defines the tunneling window for BTBT from the source into the channel. Thereby, the confinement of the tunneling windows gives rise to a band-pass filter like behavior of the TFET due to a cut off of the high and low energy tale of the FERMI distribution function, allowing for a subthreshold swing SS lower than  $60\,{\rm mV/dec}$  as in case of a MOSFET.

#### 2.3.1 Kane's BTBT Model

BTBT as a quantum mechanical process is based on the assumption that electrons can not only be described as particles but also as wave functions. In contrast to classical mechanics,

these wave functions are not fully reflected at a potential barrier but have a finite probability to penetrate through and continue after the potential barrier. In case of BTBT, this potential barrier is represented by the band gap  $E_{\rm g}$  of a semiconductor. Whenever an electron tunnels from the valence into the conduction band through the band gap  $E_{\rm g}$ , an electron-hole pair is generated.

The probability for this tunneling process can be sufficiently described by Kane's semiclassical, local BTBT model which translates BTBT currents into generation rates G of electrons and holes respectively. In case of a local model, the electric field as the gradient of the electrostatic potential,  $F = -\frac{\partial \Phi}{\partial x}$ , is supposed to be both constant and uniform, being a valid assumption as long as the electrostatic potential  $\Phi$  does not change rapidly along a certain direction x according to the so-called Wentzel-Kramers-Brillouin (WKB) approximation [27]. Thus, the generation rates G of electrons and holes can be described as a function of the first derivative of the current density J with respect to the energy E by means of the relation  $E = -e\Phi$ :

$$G = \frac{1}{e} \frac{\partial J}{\partial x} = -\frac{F}{e} \frac{\partial J}{\partial \Phi} = F \frac{\mathrm{d}J}{\mathrm{d}E}.$$

(2.3.1)

In contrast to the current density J, the generation rates G of electrons and holes are not dependent on the position x as long as the electric field F is constant as assumed in case of a local model. The current density J in turn can be derived by means of the already discussed Landauer-Büttiker formalism according to:

$$J = \frac{2e}{h} \frac{1}{A} \int_{E} dE \sum_{\mathbf{k}_{\perp}} T(E, \mathbf{k}_{\perp}) [f_{v}(E) - f_{c}(E)], \qquad (2.3.2)$$

where A denotes a normalized area and  $f_{\rm v}$  and  $f_{\rm c}$  are the FERMI distribution functions of valence and conduction band respectively. Furthermore, the transmission probability  $T\left(E,\mathbf{k}_{\perp}\right)$  is not only a function of the energy E but also of the wave vector  $\mathbf{k}_{\perp}=\mathbf{k}_{y}+\mathbf{k}_{z}$  perpendicular to the tunneling direction. Assuming an electron tunnels from a fully occupied valence into an empty conduction band, the FERMI distribution functions of valence and conduction band can be set to  $f_{\rm v}=1$  and  $f_{\rm c}=0$  respectively, simplifying equation (2.3.2) to:

$$J \approx \frac{2e}{h} \frac{1}{A} \int_{E} dE \sum_{\mathbf{k}_{\perp}} T(E, \mathbf{k}_{\perp}). \tag{2.3.3}$$

Taking the first derivative of the current density J given in equation (2.3.3) with respect to the energy E and multiplying with the electric field F yields the generation rates G of electrons and holes as follows:

$$G = \frac{2e}{h} \frac{F}{A} \sum_{\mathbf{k}_{\perp}} T(E, \mathbf{k}_{\perp}). \tag{2.3.4}$$

The sum over the transmission probabilities  $T(E, \mathbf{k}_{\perp})$  as a function of the wave vector  $\mathbf{k}_{\perp}$  perpendicular to the tunneling direction as stated in equation (2.3.4) can be converted into an integral over the whole momentum space of  $\mathbf{k}_{\perp}$  multiplied with its two-dimensional density of states  $\frac{A}{(2\pi)^2}$ :

$$G = \frac{e}{2\pi^2 h} F \iint_{\mathbf{k}_{\perp}} d^2 \mathbf{k}_{\perp} T(E, \mathbf{k}_{\perp}).$$

(2.3.5)

The transmission probability  $T(E, \mathbf{k}_{\perp})$  in turn can be calculated according to the WKB approximation as follows [28]:

$$T(E, \mathbf{k}_{\perp}) = \frac{\pi^2}{9} \exp\left(-2 \int_{x_1}^{x_2} dx \operatorname{Im}(k_x)\right),$$

(2.3.6)

with  $x_1$  and  $x_2$  being the classical turning points of the tunneling process and  $k_x$  denoting the norm of the wave vector  $\mathbf{k}_x$  parallel to the tunneling direction. Moreover, the norm of the wave vector  $\mathbf{k}_x$  parallel to the tunneling direction must be a function of the position,  $k_x = k_x(x)$ , due to energy conservation. Thus, the transmission probability  $T(E, \mathbf{k}_\perp)$  as stated in equation (2.3.6) has to be integrated over a path conserving the energy E on the one hand and the wave-vector  $\mathbf{k}_\perp$  perpendicular to the tunneling direction on the other hand. A dispersion relation E(k) as a function of the norm k of the wave-vector  $\mathbf{k}$  is required which links the states of the valence band to the states of the conduction band and is valid within the band gap  $E_{\rm g}$  in parallel [29]:

$$E_{\pm} = \frac{E_{\rm g}}{2} + \frac{\hbar^2 k^2}{2m_0} \pm \frac{1}{2} \sqrt{E_{\rm g}^2 + \frac{E_{\rm g} \hbar^2 k^2}{m_{\rm r}}},$$

(2.3.7)

where  $\hbar = \frac{h}{2\pi}$  denotes the reduced PLANCK constant. The energy of valence and conduction band respectively is given as the difference of the total energy and the energy arising from the electric field,  $E_{\pm} = E - eFx$ . The reduced tunneling mass in turn can be expressed by the reciprocal of the effective masses of valence and conduction band,  $m_r = \left(\frac{1}{m_v} + \frac{1}{m_c}\right)^{-1}$ . Assuming the contribution from the kinetic energy  $\frac{\hbar^2 k^2}{2m_0}$  as negligible within the band gap  $E_{\rm g}$ , equation (2.3.7) simplifies to:

$$E_{\pm} \approx \frac{E_{\rm g}}{2} \pm \frac{1}{2} \sqrt{E_{\rm g}^2 + \frac{E_{\rm g} \hbar^2 k^2}{m_{\rm r}}},$$

(2.3.8)

where the norm of the total wave-vector  $\mathbf{k} = \mathbf{k}_x + \mathbf{k}_\perp$  can be expressed as  $k^2 = k_x^2 + k_\perp^2 = \text{Re}(k_x)^2 + \text{Im}(k_x)^2 + k_\perp^2$  with  $k_x$  being solely imaginary within the band gap  $E_{\rm g}$ . The non-zero contribution of  $k_\perp$  keeps  $k_x$  imaginary over an even longer path as compared to the classical tunneling distance  $\frac{E_{\rm g}}{eF}$ , resulting in a larger effective band gap  $E_{\rm g}$  and thus, in a reduced transmission probability  $T(E, \mathbf{k}_\perp)$  for large values of  $k_\perp$ . In order to enable tunneling, the energy of valence and conduction band respectively has be compensated by the energy of the electric field,  $E_{\pm} = eFx$ , allowing for equation (2.3.8) to be transformed into:

$$\operatorname{Im}(k_x) = \sqrt{\frac{m_{\rm r}}{E_{\rm g}\hbar^2}} \sqrt{E_{\rm g}^2 + \frac{E_{\rm g}\hbar^2 k_{\perp}^2}{m_{\rm r}} - 4\left(eFx - \frac{E_{\rm g}}{2}\right)^2}.$$

(2.3.9)

Plugging equation (2.3.9) into equation (2.3.6) and setting the limits of the integral to  $x_1 = 0$  and  $x_2 = \frac{E_g}{eF}$  finally allows for an evaluation of the transmission probability  $T(E, \mathbf{k}_{\perp})$ :

$$T(E, \mathbf{k}_{\perp}) = \frac{\pi^2}{9} \exp\left(-\frac{\pi^2 \sqrt{m_{\rm r}} E_{\rm g}^{3/2}}{ehF}\right) \exp\left(-\frac{h\sqrt{E_{\rm g}}}{4e\sqrt{m_{\rm r}} F} k_{\perp}^2\right). \tag{2.3.10}$$

Combining equations (2.3.5) and (2.3.10) yields an integral which can be solved analytically by means of the relation  $\int_{-\infty}^{\infty} dx \, \exp\left(-ax^2\right) = \sqrt{\frac{\pi}{a}}$ . Thus, the generation rates G of electrons and holes in the limit of both a constant and uniform electric field F can be expressed as:

$$G = \frac{2\pi e^2 \sqrt{m_r}}{9h^2 \sqrt{E_g}} F^2 \exp\left(-\frac{\pi^2 \sqrt{m_r} E_g^{3/2}}{ehF}\right) = AF^2 \exp\left(-B/F\right), \tag{2.3.11}$$

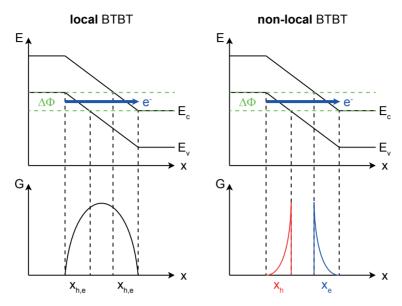

with  $A = A(E_g, m_r)$  and  $B = B(E_g, m_r)$  being material dependent parameters. Thus, equation (2.3.11) provides a sufficient approach in comparing BTBT in different semiconductors as a function of the material dependent parameters A and B. However, the corresponding BTBT currents derived from KANE's semiclassical, local model tend to be overestimated due to the assumption of both a constant and uniform electric field F, allowing for BTBT currents flowing even when no drain voltage  $V_d$  is applied since generation rates G of electrons and holes are only a function of the electric field F, but not of the drain voltage  $V_d$ . Non-local models as implemented in TCAD may encounter this issue by numerical integration. In this concept, the tunneling distance is no longer determined by a local electric field F, but by the bending of valence and conduction band due to a gradient of the electrostatic potential  $\Phi$  [30]. As a consequence, a local model does not distinguish between the generation rate  $G_h$  of holes and the generation rate  $G_e$  of electrons, resulting in the highest generation rates G of electrons and holes occurring within the band gap  $E_g$ , whereas a non-local model enables a generation rate  $G_h$  of holes at the beginning and a generation rate  $G_e$  of electrons at the end of the tunneling path as presented in figure 2.3.2.

#### 2.3.2 Phonon Assisted BTBT

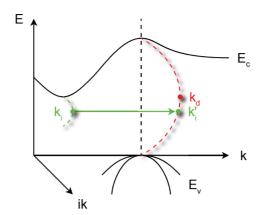

The tunneling probability as derived from Kane's semiclassical, local model describes BTBT in semiconductors exhibiting a direct band gap  $E_{\rm g}$ . This direct band gap  $E_{\rm g}$  can be overcome by proceeding along the imaginary axis ik while keeping the same point k in momentum space k as indicated in figure 2.3.3. In this concept, valence and conduction bands meet at a branch point  $k_{\rm d}$  on the imaginary axis where a direct transition from the one into the other band takes place. However, in semiconductors with an indirect band gap  $E_{\rm g}$  such as Si or Ge, an interaction with phonons is required in order to enable a transition between valence and conduction band in accordance with momentum conservation. Thus, phonon scattering bridges the gap between the two branch points  $k_{\rm i}$  and  $k'_{\rm i}$  and allows for indirect BTBT. In case of Si and Ge, the main contribution to phonon assisted BTBT arises from the interaction with transverse acoustic phonons due to their highest phonon occupation number and smallest phonon energy [31]. Phonon scattering results in an earlier onset of phonon assisted BTBT as compared to direct BTBT, introducing a stronger dependency of the generation rates G of electrons and holes on the electric field F as considered in equation (2.3.11) by changing the exponent from 2 to 2.5 as follows:

$$G = A_{\text{ind}} F^{2.5} \exp(-B_{\text{ind}}/F)$$

. (2.3.12)

Figure 2.3.2: Schematic illustration of the respective generation rates G of electrons and holes as a function of the position x in case of a local or a non-local BTBT model. A local model does not distinguish between the generation  $G_h$  of holes and the generation  $G_e$  of electrons, resulting in the highest generation rates G of electrons and holes occurring within the band gap  $E_g$ , whereas a non-local model enables a generation  $G_h$  of holes at the beginning and a generation  $G_e$  of electrons at the end of the tunneling path.

The material dependent parameters  $A_{\text{ind}}$  and  $B_{\text{ind}}$  have to be adjusted as well in order to account for the interaction with phonons:

$$A_{\text{ind}} = \frac{ge^{5/2} \left(1 + 2N_{\text{ta}}\right) D_{\text{ta}}^2 \left(m_{\text{DOS,v}} m_{\text{DOS,c}}\right)^{3/2}}{2^{21/4} h^{5/2} \rho E_{\text{ta}} m_{\text{r}}^{5/4} E_{\sigma}^{7/4}} \quad \text{and} \quad B_{\text{ind}} = \frac{2^{7/2} \pi m_{\text{r}}^{1/2} E_{\text{g}}^{3/2}}{3eh}, \quad (2.3.13)$$

with  $N_{\rm ta}$  being the phonon occupation number,  $D_{\rm ta}$  the phonon deformation potential and  $E_{\rm ta}$  the energy of transverse acoustic phonons. The density of the semiconductor itself is denoted by  $\rho$ . In addition, a degeneracy factor  $g=2g_{\rm v}g_{\rm c}$  is introduced in order to account for the degeneracy of spin and the degeneracy of different valleys in valence and conduction band respectively with the latter requiring an introduction of effective density of state (DOS) masses  $m_{\rm DOS,v}$  and  $m_{\rm DOS,c}$  of valence and conduction band respectively.

#### 2.3.3 Trap Assisted Tunneling

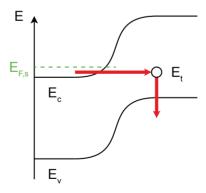

Similar to phonon assisted BTBT, trap assisted tunneling (TAT) enables a tunneling process without an energy overlap  $\Delta\Phi$  of valence and conduction band already established by an external electrical field F, also resulting in an earlier onset of TAT as compared to direct

Figure 2.3.3: Schematic illustration of a direct and an indirect BTBT process. A direct band gap  $E_{\rm g}$  can be overcome by proceeding along the imaginary axis ik while keeping the same point k in momentum space k. Valence and conduction band meet at a branch point  $k_{\rm d}$  on the imaginary axis where a direct transition from the one into the other band takes place. In case of an indirect band gap  $E_{\rm g}$ , an interaction with phonons is required in order to enable a transition between valence and conduction band in accordance with momentum conservation. Thus, phonon scattering bridges the gap between the two branch points  $k_{\rm i}$  and  $k'_{\rm i}$  and allows for indirect BTBT.

BTBT. Carriers from the source tunnel into trap states of an energy  $E_{\rm t}$  within the band gap  $E_{\rm g}$  of the channel and reach its bands by thermal excitation from these trap states as shown in figure 2.3.4 [32]. Trap states can be introduced by traps at the interface of the oxide, defects due to ion implantation at the tunneling junction or dopants themselves. TAT arising from the latter will be discussed in more detail in chapter 3.2.2.

Figure 2.3.4: Schematic illustration of a TAT process. Carriers from the source tunnel into trap states of an energy  $E_{\rm t}$  within the band gap  $E_{\rm g}$  of the channel and reach its bands by thermal excitation from these trap states.

Since the excitation of carriers from trap states into the channel is based on thermionic emission, a dependency on the FERMI distribution function arises. As a consequence, the band-pass filter like behavior of a TFET is lost, degrading the lower limit of the subthreshold swing SS to  $60 \,\mathrm{mV/dec}$  as in case of a MOSFET.

#### 2.3.4 Shockley-Read-Hall Recombination

The recombination of electrons from the conduction band with holes from the valence band by means of trap states of an energy  $E_{\rm t}$  within the band gap  $E_{\rm g}$  is known as Shockley-Read-Hall (SRH) recombination [33, 34]. The process describes a non-radiative recombination, being much more probable than direct recombination since less energy is needed for activation. The energy released during this recombination process is consumed by lattice vibrations. The resulting recombination rate R can be calculated as:

$$R = \frac{np - n_{\rm i}^2}{(n + n_0)\tau_{\rm p} + (p + p_0)\tau_{\rm p}},$$

(2.3.14)

with

$$n_0 = n_{\rm i} \exp\left(\frac{E_{\rm t} - E_{\rm F}}{k_{\rm B}T}\right)$$

and  $p_0 = n_{\rm i} \exp\left(\frac{E_{\rm F} - E_{\rm t}}{k_{\rm B}T}\right)$ , (2.3.15)

where n and p denote the carrier concentrations of electrons and holes respectively and  $\tau_n$  and  $\tau_p$  their corresponding lifetimes. The energy  $E_t$  of the trap states is given with respect to the FERMI energy  $E_F$ . Moreover, the intrinsic carrier concentration  $n_i$  of a semiconductor can be expressed as [27]:

$$n_{\rm i} = \sqrt{N_{\rm c}N_{\rm v}} \exp\left(-\frac{E_{\rm g}}{2k_{\rm B}T}\right),\tag{2.3.16}$$

with  $N_c$  and  $N_v$  being the DOS in conduction and valence band respectively. Equation (2.3.16) reveals an increase of the intrinsic carrier concentration  $n_i$  of the semiconductor with decreasing band gap  $E_g$  [35].

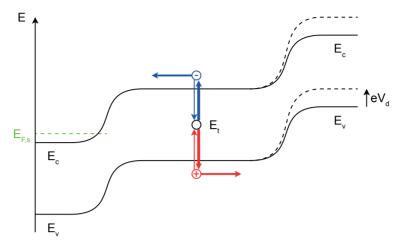

In case of TFET operation as described in chapter 2.3, the p-i-n structure is operated in reverse bias conditions, resulting in electrons from the channel flowing to the n<sup>+</sup>-doped region and holes from the channel to the p<sup>+</sup>-doped region respectively as depicted in figure 2.3.5. Subsequently, the carrier concentrations n and p of electrons and holes are decreased below the intrinsic carrier concentration  $n_i$  of the channel, enabling a negative recombination rate R as visible from equation (2.3.14). For this particular case, SRH generation exceeds SRH recombination and thus, determines the lower limit of the off-current  $I_{\text{off}}$  in a TFET. As a consequence, taking equation (2.3.16) into account, the use of materials with small(er) band gap  $E_g$  such as strained SiGe, Ge or GeSn requires a trade-off between an increased off-current  $I_{\text{off}}$  due to enabled SRH generation and an increased on-current  $I_{\text{on}}$  due to an improved probability for BTBT.

#### 2.3.5 BTBT Mechanisms

The BTBT mechanism as described in chapter 2.3 is referred to in literature as point tunneling. Point tunneling occurs at the interface between source and channel with the latter

Figure 2.3.5: Schematic illustration of a SRH generation-recombination process. In case of TFET operation, the p-i-n structure is operated in reverse bias conditions, resulting in electrons from the channel flowing to the  $n^+$ -doped region and holes from the channel to the  $p^+$ -doped region respectively. Subsequently, the carrier concentrations n and p of electrons and holes are decreased below the intrinsic carrier concentration  $n_i$  of the channel, enabling a negative recombination rate R. For this particular case, SRH generation exceeds SRH recombination.

controlled by a gate and thus, is confined to a local area. In addition, when parts of the source region are also overlapped by the gate, line tunneling into a depleted region within the source as a second contribution to BTBT may set in. Naming of both BTBT mechanisms arises from the area where each tunneling process has its origin: While point tunneling starts from a single point at the interface between source and channel, the area for line tunneling resembles a line perpendicular to the gate electric field lines as illustrated in figure 2.3.6. As a consequence, line tunneling occurs in direction parallel with the gate electric field lines,

Figure 2.3.6: Schematic illustration of the point and line tunneling mechanism. Point tunneling starts from a single point at the interface between source and channel whereas the area for line tunneling resembles a line perpendicular to the gate electric field lines. As a consequence, line tunneling occurs in direction parallel with the gate electric field lines into a depleted region within the source overlapped by the gate.

enabling a diminished influence of the latter as compared to point tunneling and thus, accounting for the strong dependency of the generation rates G of electrons and holes on the electric field F in case of phonon assisted BTBT as already discussed in chapter 2.3.2.

In order to be able to quantify the respective dependencies of both BTBT mechanisms on the electric field F, their corresponding dependencies of the drain current  $I_{\rm d}$  on the gate voltage  $V_{\rm g}$  are derived by integrating the generation rates G of electrons and holes as stated in equation (2.3.11) over the volume V of the p-i-n structure:

$$I_{\rm d} = e \int_{V} dV G = e \int_{V} dV A F^2 \exp(-B/F).$$

(2.3.17)

Assuming direct BTBT as indicated in equation (2.3.17) due to the exponent of the electric field F being equal to 2, the dependency of the drain current  $I_{\rm d}$  on the gate voltage  $V_{\rm g}$  in case of point tunneling can be approximated as [36]:

$$I_{\rm d} \propto V_{\sigma}^4 \exp(1/V_{\rm g}),$$

(2.3.18)

resulting in a dependency of the subthreshold swing SS on the gate voltage  $V_{\rm g}$  as follows:

$$SS = \left[\frac{\partial \log I_{\rm d}}{\partial V_{\rm g}}\right]^{-1} \propto V_{\rm g}.$$

(2.3.19)

Equation (2.3.19) reveals a linear increase of the subthreshold swing SS as a function of the gate voltage  $V_g$ , allowing for small values of the subthreshold swing SS only for small gate voltages  $V_g$ . In contrast to point tunneling, the dependency of the drain current  $I_d$  on the gate voltage  $V_g$  in case of line tunneling can be approximated as [37, 36]:

$$I_{\rm d} \propto \sqrt{V_{\rm g} - V_{\rm onset}} \exp\left(\sqrt{V_{\rm g} - V_{\rm onset}}\right),$$

(2.3.20)

where  $V_{\rm onset}$  denotes the onset voltage as a measure of the gate voltage  $V_{\rm g}$  required in order to deplete parts of the source region directly underneath the gate as a precondition for line tunneling aligned with the gate electric field lines. The corresponding dependency of the subthreshold swing SS on the gate voltage  $V_{\rm g}$  yields:

$$SS = \left[\frac{\partial \log I_{\rm d}}{\partial V_{\rm g}}\right]^{-1} \propto \sqrt{V_{\rm g} - V_{\rm onset}} \approx \sqrt{V_{\rm onset}} + \mathcal{O}\left(V_{\rm g}\right). \tag{2.3.21}$$

As already indicated, equation (2.3.21) reveals a less pronounced dependency of the subthreshold swing SS on the gate voltage  $V_{\rm g}$  in case of line tunneling as compared to point tunneling due to a root dependency instead of a linear relation. Taking the TAYLOR series for an expansion at small gate voltages  $V_{\rm g}$  into account, the subthreshold swing SS in case of line tunneling can be assumed as constant with its lower limit depending only on the root of the onset voltage  $\sqrt{V_{\rm onset}}$ . Thus, good electrostatic control is required in order to minimize the value of the onset voltage  $V_{\rm onset}$  with the latter mainly determined by the band gap  $E_{\rm g}$ , the thickness  $t_{\rm ox}$  of the gate oxide and the carrier concentration  $n_{\rm s}$  of the source which has to be depleted in a region directly underneath the gate in order to allow for line

tunneling aligned with the gate electric field lines [37, 36]. For both BTBT mechanisms, no direct dependency of the subthreshold swing SS on the temperature T is obvious due to the band-pass filter like behavior of a TFET, being a major difference as compared to a MOSFET where the lower limit of the subthreshold swing SS is determined by the high and low energy tale of the FERMI distribution function.

#### 2.4 Design Considerations

TFETs are discussed as a promising concept for low-power electronics, but still suffer from low on-currents  $I_{\rm on}$  as compared to state of the art MOSFETs. In addition, their usage in CMOS applications is still quite limited due to the inherent ambipolar switching of TFETs. This ambipolar switching arises from the symmetry of the p-i-n structure that defines a TFET. Thus, BTBT in a TFET occurs not only at the source junction but also at the drain junction depending on the actual gate voltage  $V_{\rm g}$  applied to the channel. The ambipolarity of a TFET becomes even more pronounced when contributions from phonon assisted BTBT and TAT come into play. Due to their earlier onset as compared to direct BTBT, the resulting n- and p-branch of the transfer characteristics move closer together. For n- and p-branch intersecting, the off-current  $I_{\rm off}$  of the TFET is increased as compared to pure SRH generation, resulting in a degraded static power consumption  $P_{\rm static}$  as visible from equation (2.1.2).

Both problems of low on-currents  $I_{\rm on}$  as well as the ambipolar switching can be tackled in parallel by introducing materials with small(er) band gap  $E_{\rm g}$  such as strained SiGe, Ge or GeSn at the source tunnel junction of the TFET, allowing for a heterostructure device concept. In contrast to a homostructure, a heterostructure may suppress the ambipolar switching due to the symmetry of the p-i-n structure lifted while enabling an enhanced probability for BTBT and increased on-current  $I_{\rm on}$  due to a reduction of the band gap  $E_{\rm g}$ in parallel. However, this reduced band gap  $E_{\rm g}$  might increase the off-current  $I_{\rm off}$  of the TFET due to increased SRH generation as already pointed out in chapter 2.3.4. Within the framework of this thesis, compressively strained SiGe as the material with smaller band gap  $E_{\rm g}$  of choice and its influence on the performance of a TFET will be examined. As a further possibility to tune the probability for BTBT and the on-current  $I_{\text{on}}$  of a TFET without a simultaneous increase of the off-current  $I_{\text{off}}$ , an optimization of the electrostatic control with respect to the gate oxide is suggested. As already highlighted in chapter (2.3.5), especially line tunneling aligned with the gate electric field lines requires optimized electrostatic control due to its dependency on an onset voltage  $V_{\text{onset}}$ , allowing for an improved subthreshold swing SS as compared to point tunneling.

#### 2.4.1 Strain Engineering

When growing SiGe pseudomorphically on Si, compressive, biaxial strain  $\varepsilon$  is introduced into the SiGe layer due to the lattice mismatch between Si and Ge. In this regard, the lattice

constant  $a_{0,\text{SiGe}}(x)$  of relaxed SiGe as a function of the Ge mole fraction x can be obtained by the following analytical expression based on VEGARD's empirical law [38]:

$$a_{0.\text{SiGe}}(x) = a_{0.\text{Si}} + 0.200326x(1-x) + (a_{0.\text{Ge}} - a_{0.\text{Si}})x^2,$$

(2.4.1)

with  $a_{0,\mathrm{Si}} = 5.43\,\text{Å}$  and  $a_{0,\mathrm{Ge}} = 5.65\,\text{Å}$  denoting the lattice constants of Si and Ge respectively at room temperature  $T = 300\,\mathrm{K}$ . The resulting band structure of relaxed SiGe can be approximated as Si-like for Ge mole fractions up to  $x \leq 0.85$  [39], enabling an indirect transition stemming from the band gap  $E_{\mathrm{g}}$  between  $\Gamma$  and  $\Delta$  being the dominant contribution to BTBT. The according band gap  $E_{\mathrm{g,SiGe}}(x)$  of relaxed SiGe as a function of the Ge mole fraction x can be approximated as [40]:

$$E_{g,SiGe}(x) = E_{g,Si} - 0.454x + 0.208x^2,$$

(2.4.2)

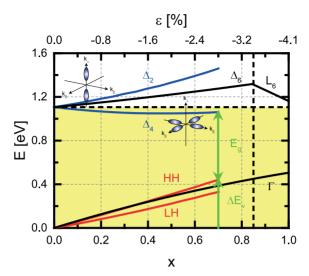

where  $E_{\rm g,Si}=1.11\,{\rm eV}$  denotes the band gap of relaxed Si at room temperature  $T=300\,{\rm K}.$ Equation (2.4.2) reveals a decreasing band gap  $E_{g,SiGe}(x)$  for increasing Ge mole fractions x. The compressive, biaxial strain  $\varepsilon$  introduced by the pseudomorphic growth breaks the lattice symmetry of the relaxed SiGe layer, lifting both the degeneracy of the  $\Delta_6$  conduction band valleys as well as the degeneracy of LH and HH bands stemming from the  $\Gamma$  valley. The  $\Delta_6$  conduction band valleys split into  $\Delta_4$  and  $\Delta_2$  valleys with the former lowered in energy whereas the HH band is increased in energy with respect to the LH band. Thus, the band gap  $E_{\rm g}$  of compressively, biaxially strained SiGe is determined by the difference of the  $\Delta_4$  conduction band valleys and the HH band as presented in figure 2.4.1. While the conduction band offset  $\Delta E_c$  between the strained SiGe layer and the Si substrate is mainly determined by the difference in their electron affinities  $\chi$  and thus, can be assumed as negligible, the valence band offset at room temperature  $T = 300 \,\mathrm{K}$  scales linearly as a function of the Ge mole fraction according to  $\Delta E_{\rm v} \approx 0.74x$  [42], resulting in a p-type configuration being the more favorable one in terms of an energy overlap  $\Delta\Phi$  as a tunneling window to be established. In addition, the electron effective masses  $m_c$  of the  $\Delta_4$  valleys do not change significantly as a function of the Ge mole fraction x or strain  $\varepsilon$  [43]. Even though the band gap  $E_{\rm g}$  of compressively, biaxially strained SiGe is further reduced as compared to relaxed SiGe, phonon assisted BTBT still remains the dominant transition for Ge mole fractions up to x < 0.7 with higher Ge mole fractions x > 0.7 constrained due to the critical thickness caused by the lattice mismatch between Si and Ge [42]. The resulting degeneracy factor for phonon assisted BTBT according to equation (2.3.13) can be specified as  $g = 2g_vg_c = 2 \cdot 1 \cdot 4 = 8$  with respect to spin, the non-degenerate HH band and the fourfold degenerate  $\Delta_4$  conduction band valleys.

#### 2.4.2 EOT Scaling

In order to quantify the electrostatic control in a single-gate transistor with respect to the gate oxide, the screening length  $\lambda_{ch}$  as one solution of Poisson's equation can be taken into account [44]:

$$\lambda_{\rm ch} = \sqrt{\frac{\kappa_{\rm sc}}{\kappa_{\rm ox}} t_{\rm sc} t_{\rm ox}},\tag{2.4.3}$$

with  $\kappa_{\rm sc}$  and  $\kappa_{\rm ox}$  being the dielectric constants of the semiconductor and the gate oxide respectively and  $t_{\rm sc}$  and  $t_{\rm ox}$  denoting their respective layer thicknesses. Equation (2.4.3)

Figure 2.4.1: Schematic illustration of the band structures of relaxed and strained SiGe as a function of the Ge mole fraction x and the corresponding compressive biaxial strain  $\varepsilon$  within the SiGe layer based on nonlocal empirical pseudopotential method (EPM) calculations [41, 40, 42]. The band structure of relaxed SiGe changes from Si-like into Ge-like at a Ge mole fraction x of about 0.85 as indicated by a dashed vertical line. The dashed horizontal line in turn depicts the band gap  $E_{\rm g}$  of Si at room temperature  $T=300\,{\rm K}$  as a reference level for the valence band offset  $\Delta E_{\rm v}$ . Compressive, biaxial strain  $\varepsilon$  introduced by the pseudomorphic growth breaks the lattice symmetry of the relaxed SiGe layer, lifting both the degeneracy of the  $\Delta_6$  conduction band valleys as well as the degeneracy of LH and HH bands stemming from the  $\Gamma$  valley. The  $\Delta_6$  conduction band valleys split into  $\Delta_4$  and  $\Delta_2$  valleys with the former lowered in energy whereas the HH band is increased in energy with respect to the LH band. Thus, the band gap  $E_{\rm g}$  of compressively, biaxially strained SiGe is determined by the difference of the  $\Delta_4$  conduction band valleys and the HH band.

reveals a reduced screening length  $\lambda_{\rm ch}$  for either a decreased thickness  $t_{\rm sc}$  of the semiconductor, a decreased thickness  $t_{\rm ox}$  of the gate oxide or an increased dielectric constant  $\kappa_{\rm ox}$  of the gate oxide itself. However, decreasing the thickness  $t_{\rm ox}$  of the gate oxide may result in an increased gate leakage, degrading the off-current  $I_{\rm off}$  and consequently, the subthreshold characteristics of a TFET. In this regard, the introduction of dielectrics with a higher relative permittivity  $\kappa_{\rm ox}$  enables an appropriate way to reduce the screening length  $\lambda_{\rm ch}$  while keeping the thickness  $t_{\rm ox}$  of the gate oxide layer constant, allowing for an overall improved electrostatic control. In 2007, HfO<sub>2</sub> as such a high- $\kappa$  dielectrics with a relative permittivity of  $\kappa_{\rm HfO_2} \approx 25$  was introduced by Intel Corporation in their 45 nm node [2]. However, the growth of high- $\kappa$  dielectric layers still remains challenging due to the formation of an interfacial oxide layer. In case of Si, this interfacial oxide layer consists of SiO<sub>2</sub> with its low relative permittivity of  $\kappa_{\rm SiO_2} \approx 3.9$ , diminishing the intended effect of a high- $\kappa$  dielectric.

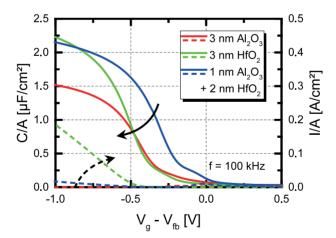

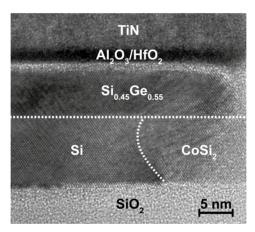

Within the framework of this thesis, the introduction of  $Al_2O_3$  as an interlayer between Si and  $HfO_2$  is investigated. On the one hand,  $Al_2O_3$  provides a relative permittivity of  $\kappa_{Al_2O_3} \approx 9$  being more than two times larger than in case of pure SiO<sub>2</sub> and on the other

hand, Aluminium (Al) is known to act as a diffusion barrier, resulting in a decreased thickness of the interfacial oxide layer in ideal case [45, 46]. In order to evaluate the influence of an  ${\rm Al_2O_3}$  interlayer on the electrostatic control, capacitance-voltage (CV) measurements on MOS capacitors incorporating three different gate oxide compositions, namely 3 nm  ${\rm Al_2O_3}$ , 3 nm  ${\rm HfO_2}$  and 1 nm  ${\rm Al_2O_3} + 2$  nm  ${\rm HfO_2}$ , are performed, granting information about both the gate capacitance C as well as the leakage current I of each MOS capacitor. In this regard, the respective capacitance  $C_{\rm acc}$  in accumulation of each MOS capacitor corresponds to the capacitance  $C_{\rm ox}$  of its gate oxide and can be assumed as:

$$C_{\rm acc} = C_{\rm ox} = \kappa_0 \kappa_{\rm ox} \frac{A}{t_{\rm ox}},\tag{2.4.4}$$

with  $\kappa_0$  being the vacuum permittivity and A denoting the area of the capacitor. Equation (2.4.4) reveals an increased capacitance  $C_{\rm ox}$  of the gate oxide for an increased dielectric constant  $\kappa_{\rm ox}$ . Both the resulting area-normalized gate capacitance  $\frac{C}{A}$  of the MOS capacitor and its area-normalized leakage current  $\frac{I}{A}$  are plotted as a function of the gate voltage  $V_{\rm g}$  corrected by the respective flat-band voltage  $V_{\rm fb}$  of each gate stack composition at a frequency f of 100 kHz as shown in figure 2.4.2. In this regard, the flat-band voltage  $V_{\rm fb}$  as a measure of the difference of the work functions of the gate metal and the semiconductor can be determined as the maximum of the reciprocal of the second derivative of the gate capacitance C with respect to the gate voltage  $V_{\rm g}$  [47]. In addition, in order to account for a possible frequency dispersion arising in accumulation, a compensation of the series resistance is applied beforehand [48]. Pure HfO<sub>2</sub> reveals not only the highest area-normalized capacitance  $\frac{C_{\rm acc}}{A}$  in accumulation at a gate voltage of  $V_{\rm g} = V_{\rm fb} - 1\,\rm V$  but also the highest area-normalized leakage current  $\frac{I_{\rm acc}}{A}$  in accumulation. Instead of the area-normalized capacitance

Figure 2.4.2: Measured area-normalized gate capacitance  $\frac{C}{A}$  of the MOS capacitor as well as its area-normalized leakage current  $\frac{I}{A}$  as a function of the gate voltage  $V_{\rm g}$  corrected by the respective flatband voltage  $V_{\rm fb}$  of each gate stack composition at a frequency f of 100 kHz. Pure HfO<sub>2</sub> reveals not only the highest area-normalized capacitance  $\frac{C_{\rm acc}}{A}$  in accumulation at a gate voltage of  $V_{\rm g} = V_{\rm fb} - 1 \, {\rm V}$  but also the highest area-normalized leakage current  $\frac{I_{\rm acc}}{A}$  in accumulation.

$\frac{C_{\rm acc}}{A}$  in accumulation, the use of the equivalent oxide thickness (EOT) is more convenient in order to compare the three different gate stack compositions. In this regard, the EOT is a measure of how thick a gate stack consisting of pure SiO<sub>2</sub> needs to be in order to reach the same area-normalized capacitance  $\frac{C_{\rm acc}}{A}$  in accumulation as the gate stack having high- $\kappa$  dielectrics incorporated and can be calculated from the capacitance equivalent thickness (CET) plus a quantum mechanical correction as follows:

$$EOT = CET - QM_{corr} = \frac{\kappa_0 \kappa_{SiO_2}}{\underline{C_{acc}}} - 0.4 \,\text{nm}, \qquad (2.4.5)$$

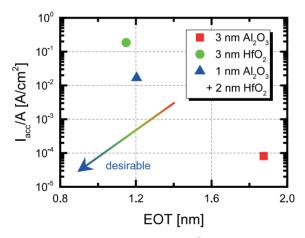

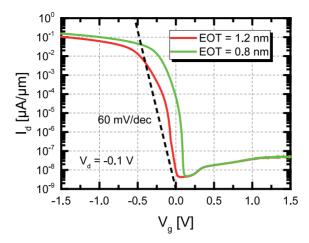

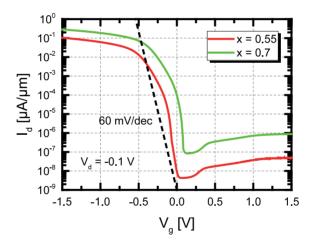

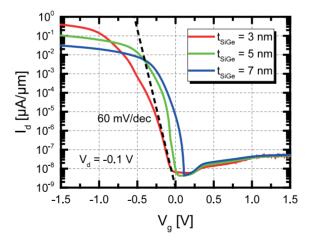

with  $QM_{corr}=0.4\,\mathrm{nm}$  being the quantum mechanical correction in case of Si [49]. Figure 2.4.3 summarizes the obtained values of the EOT, plotting the area-normalized leakage current  $\frac{I_{acc}}{A}$  in accumulation as a function of the EOT for all three different gate oxide compositions. At first, the values of the EOT in case of pure HfO<sub>2</sub> and the combination of Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> are comparable in the range of 1.2 nm, suggesting a reduction of the interfacial layer by the presence of Al<sub>2</sub>O<sub>3</sub> in order to compensate for its lower relative permittivity as compared to pure HfO<sub>2</sub>,  $\kappa_{\mathrm{Al_2O_3}} < \kappa_{\mathrm{HfO_2}}$ . Even more important, the combination of Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> reveals an one order of magnitude lower area-normalized leakage current  $\frac{I_{acc}}{A}$  in accumulation as compared to pure HfO<sub>2</sub>, allowing for a decreased off-current  $I_{\mathrm{off}}$  and thus, improved subthreshold characteristics as a key advantage for TFET operation.

Figure 2.4.3: Measured area-normalized leakage current  $\frac{I_{aC}}{A}$  in accumulation as a function of the EOT for all three different gate oxide compositions. At first, the values of the EOT in case of pure  $HfO_2$  and the combination of  $Al_2O_3$  and  $HfO_2$  are comparable in the range of 1.2 nm, suggesting a reduction of the interfacial layer by the presence of  $Al_2O_3$  in order to compensate for its lower relative permittivity as compared to pure  $HfO_2$ ,  $\kappa_{Al_2O_3} < \kappa_{HfO_2}$ . Even more important, the combination of  $Al_2O_3$  and  $HfO_2$  reveals an one order of magnitude lower area-normalized leakage current  $\frac{I_{acc}}{A}$  in accumulation as compared to pure  $HfO_2$ , allowing for a decreased off-current  $I_{off}$  and thus, improved subthreshold characteristics as a key advantage for TFET operation.

## 3 Vertical SiGe/Si Heterostructure TFETs

This chapter deals with the concept of a vertical SiGe/Si heterostructure TFET which makes use of strained SiGe as a material with smaller band gap  $E_{\rm g}$  at the source tunnel junction in order to increase the probability for BTBT while suppressing the ambipolar switching characteristics in parallel due to the use of Si with its higher band gap  $E_{\rm g}$  as compared to SiGe at the drain tunnel junction, enabling a heterostructure device concept. In addition, the vertical SiGe/Si heterostructure TFET benefits from in-situ doping of source and drain during growth in order to allow for a low density of defects at the source tunnel junction and thus, a diminished influence of TAT as compared to common ion implantation. Furthermore, the vertical SiGe/Si heterostructure TFET serves as a proof of concept for further integration of materials with small band gap  $E_{\rm g}$  such as strained Ge or GeSn which allow for a direct band gap  $E_{\rm g}$  transition into a three-dimensional device structure while maintaining a Si compatible technology [18].

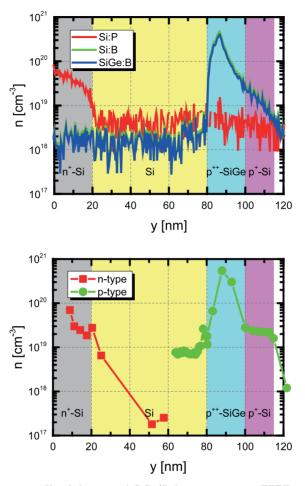

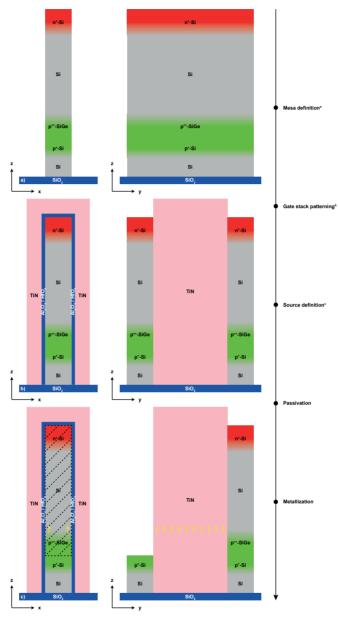

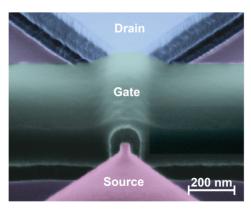

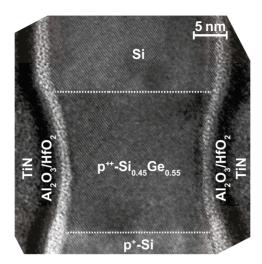

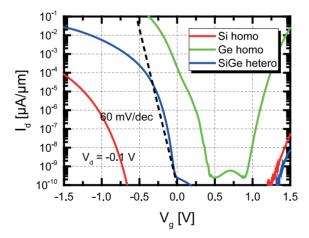

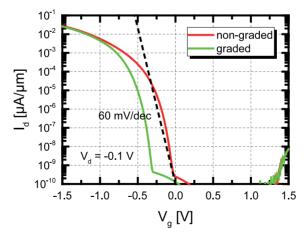

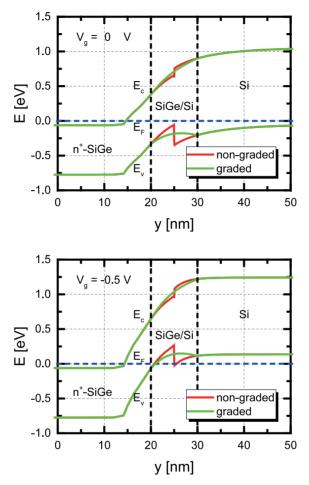

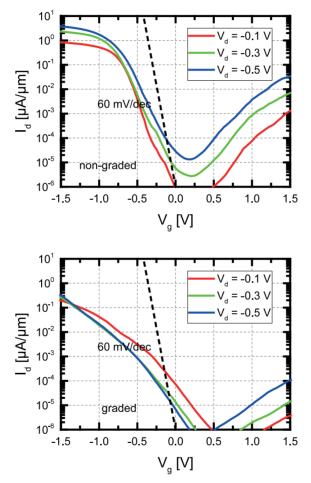

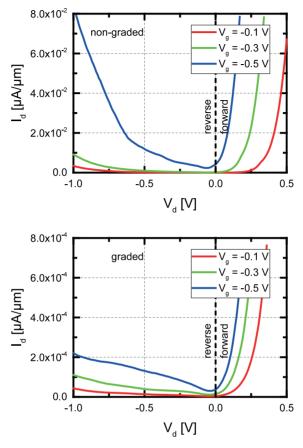

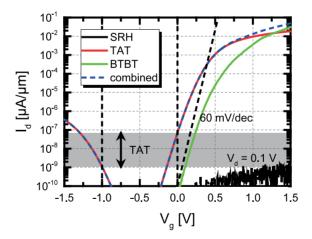

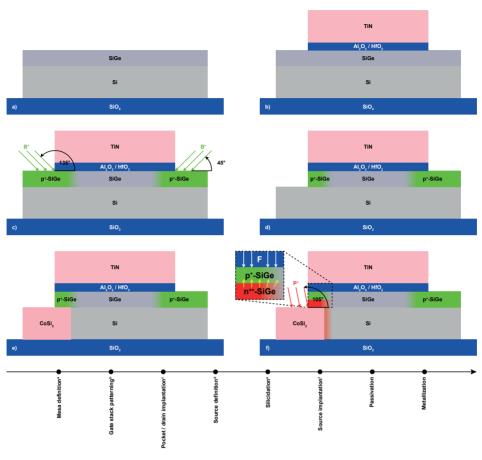

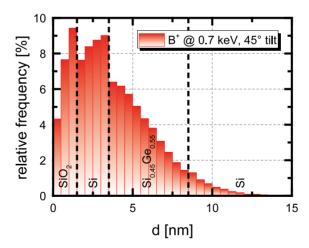

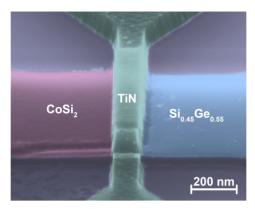

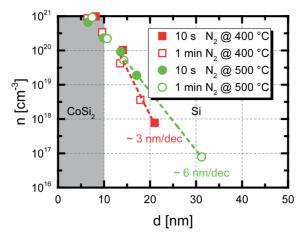

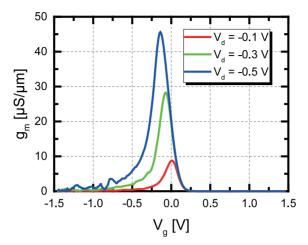

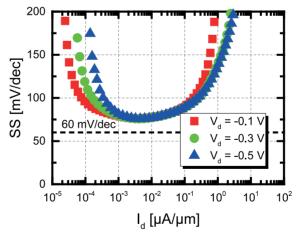

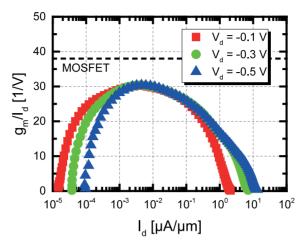

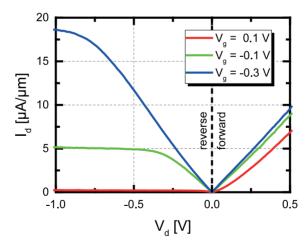

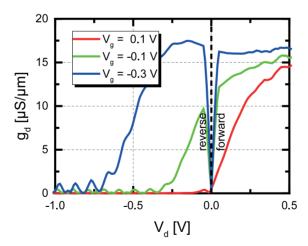

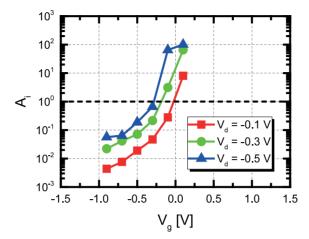

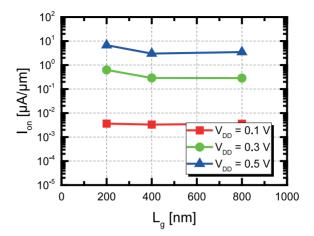

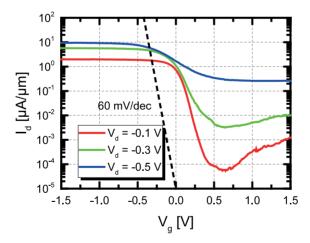

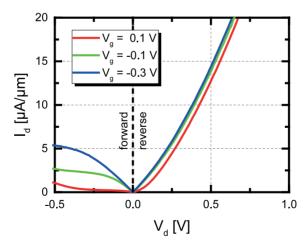

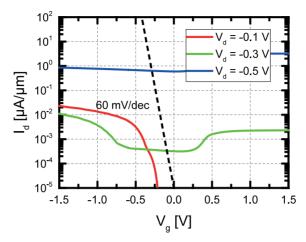

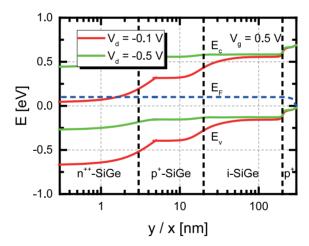

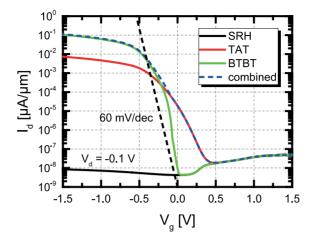

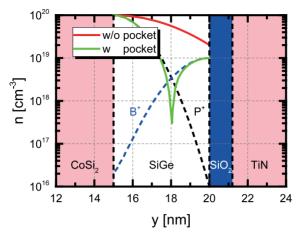

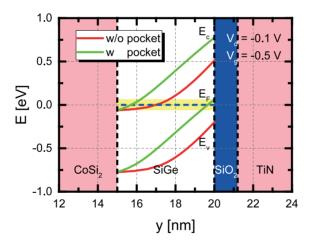

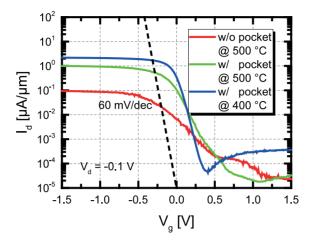

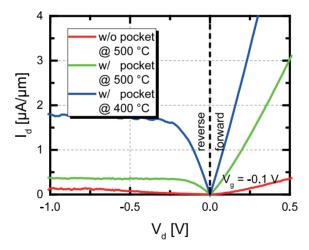

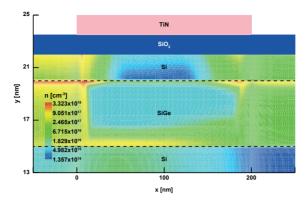

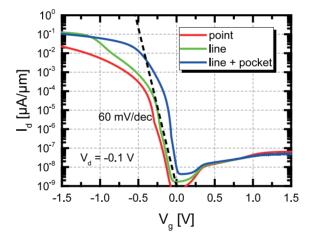

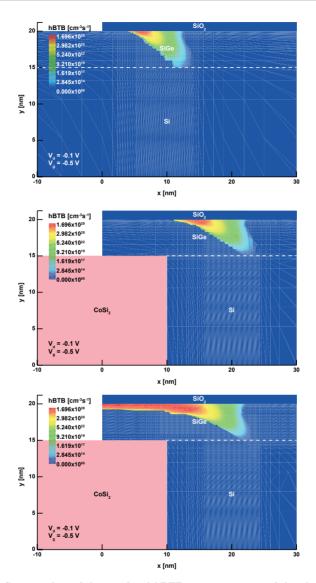

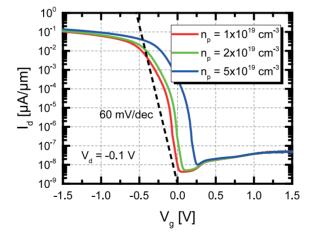

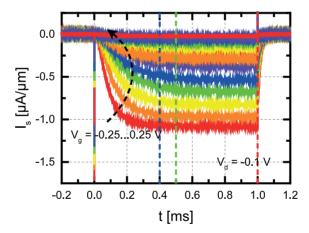

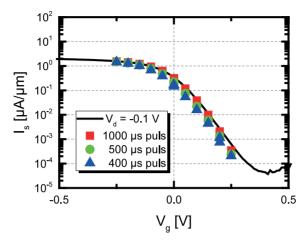

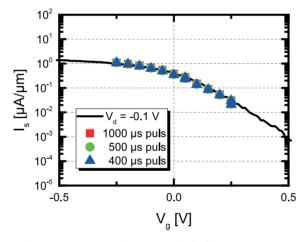

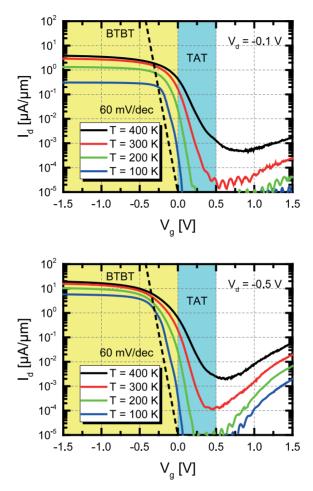

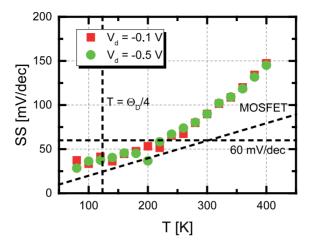

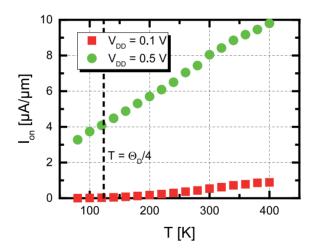

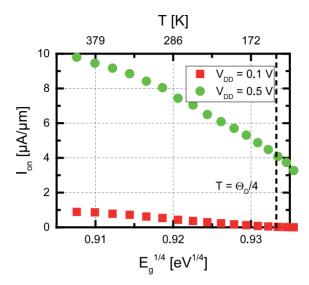

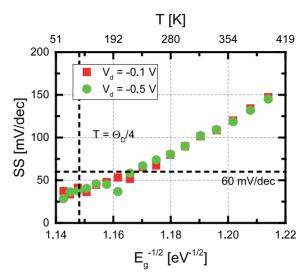

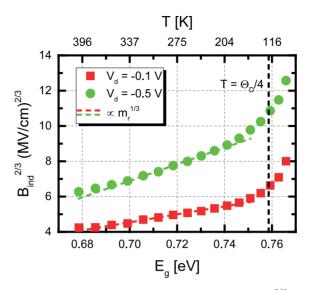

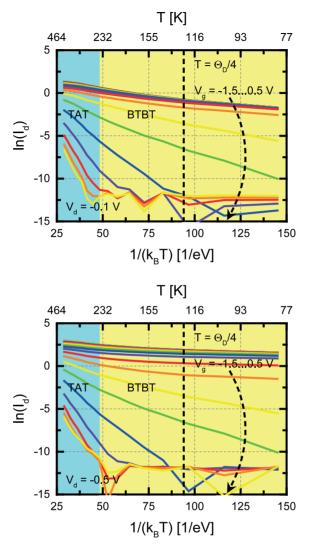

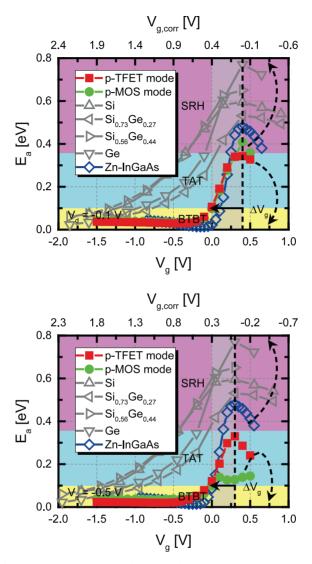

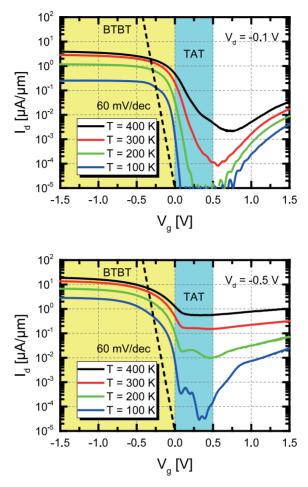

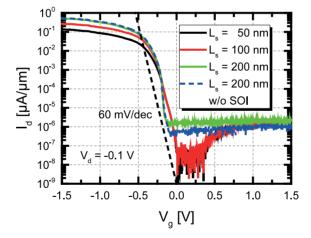

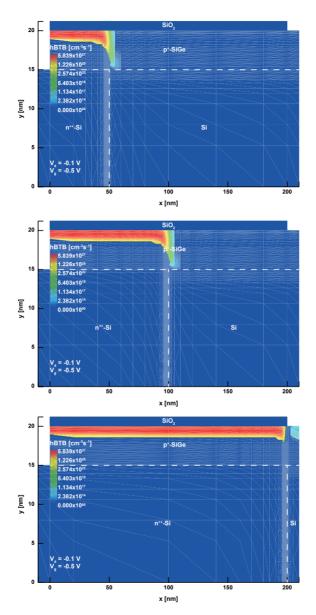

#### 3.1 Device Fabrication