# Silicon nanowire structures for neuronal cell interfacing

Sergii Pud

Schlüsseltechnologien / Key Technologies Band / Volume 112 ISBN 978-3-95806-089-0

Forschungszentrum Jülich GmbH Peter Grünberg Institute/Institute of Complex Systems Bioelectronics (PGI-8/ICS-8)

# Silicon nanowire structures for neuronal cell interfacing

Sergii Pud

Schriften des Forschungszentrums Jülich Reihe Schlüsseltechnologien / Key Technologies

Band / Volume 112

ISSN 1866-1807

ISBN 978-3-95806-089-0

Bibliographic information published by the Deutsche Nationalbibliothek. The Deutsche Nationalbibliothek lists this publication in the Deutsche Nationalbibliografie; detailed bibliographic data are available in the Internet at http://dnb.d-nb.de.

| Publisher and<br>Distributor: | Forschungszentrum Jülich GmbH<br>Zentralbibliothek<br>52425 Jülich<br>Tel: +49 2461 61-5368<br>Fax: +49 2461 61-6103<br>Email: zb-publikation@fz-juelich.de<br>www.fz-juelich.de/zb |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cover Design:                 | Grafische Medien, Forschungszentrum Jülich GmbH                                                                                                                                     |

| Printer:                      | Grafische Medien, Forschungszentrum Jülich GmbH                                                                                                                                     |

| Copyright:                    | Forschungszentrum Jülich 2015                                                                                                                                                       |

Schriften des Forschungszentrums Jülich Reihe Schlüsseltechnologien / Key Technologies, Band / Volume 112

D 82 (Diss. RWTH Aachen University, 2015)

ISSN 1866-1807 ISBN 978-3-95806-089-0

The complete volume is freely available on the Internet on the Jülicher Open Access Server (JuSER) at www.fz-juelich.de/zb/openaccess.

Neither this book nor any part of it may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying, microfilming, and recording, or by any information storage and retrieval system, without permission in writing from the publisher.

| TAB            | LE ( | OF CONTENTS                                          | 5  |

|----------------|------|------------------------------------------------------|----|

| ABS            | TRA  | ACT                                                  | 7  |

| ZUS            | AMI  | MENFASSUNG                                           | 9  |

| ACK            | (NO  | WLEDGEMENTS                                          | 11 |

| 1.             | INTI | RODUCTION                                            |    |

|                |      | CORETICAL, EXPERIMENTAL BACKGROUND AND STAT          |    |

|                |      | licon nanowire based biosensors                      |    |

| <b>2.1</b> 2.1 |      | Icon nanowire based biosensors<br>Introduction       |    |

| 2.1            |      | Ion-sensitive field effect transistors as biosensors |    |

| 2.1            | 1.3  | Silicon nanowire FET biosensors.                     |    |

| 2.1            | 1.4  | Signal-to-noise ratio in silicon NW FETs             |    |

| 2.2            | No   | pise Spectroscopy                                    |    |

| 2.2            | 2.1  | Introduction                                         |    |

| 2.2            | 2.2  | Spectral density                                     | 31 |

| 2.2            | 2.3  | Main sources of noise in Si NW FET                   |    |

| 2.3            |      | ectrogenic cells on FETs                             |    |

| 2.3            |      | Introduction                                         |    |

| 2.3            |      | Neuronal cells and the action potential              |    |

| 2.3            | 3.3  | Extracellular recording from a neuronal cell         |    |

| 2.4            | Su   | mmary                                                | 49 |

| <b>3.</b> 1    | MAT  | FERIALS AND METHODS                                  | 50 |

| 3.1            | In   | troduction                                           | 50 |

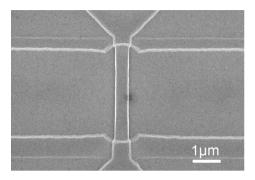

| 3.2            | Sil  | licon nanowire FETs                                  | 50 |

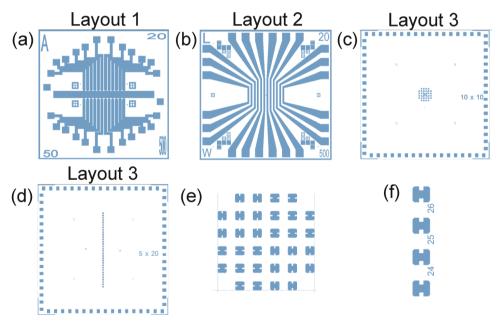

| 3.2            | 2.1  | Chip layout                                          |    |

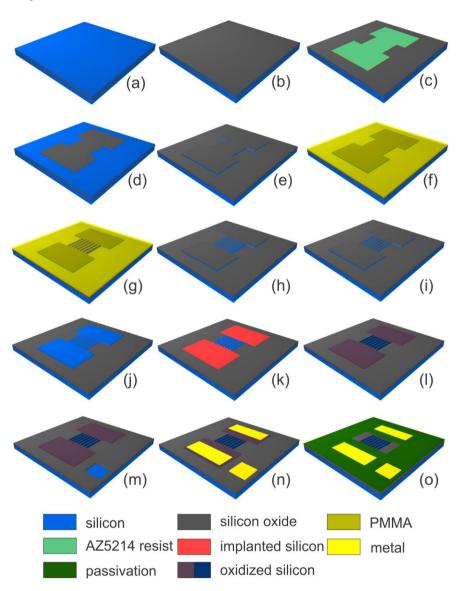

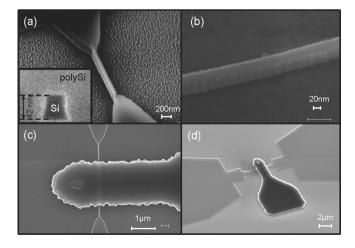

| 3.2            | 2.2  | Fabrication technology                               |    |

| 3.2            | 2.3  | Encapsulation of the Si NW chips                     |    |

| 3.3            |      | NW FET characterization                              |    |

| 3.3            |      | <i>I-V characterization</i>                          |    |

| 3.3            |      | Noise spectra measurements                           |    |

| 3.3            | 3.3  | Transconductance measurements                        |    |

# Table of contents

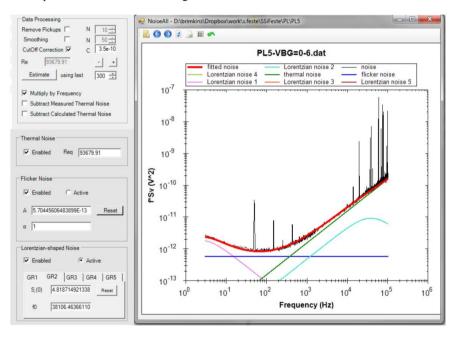

| 3.3.4  | Noise spectra fitting                                                  | 66  |

|--------|------------------------------------------------------------------------|-----|

| 3.4 N  | euronal cells on silicon nanowires                                     |     |

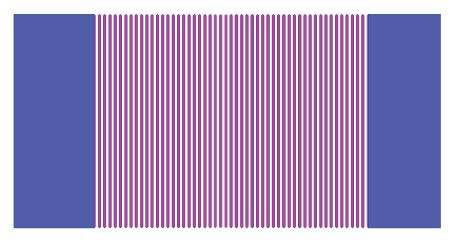

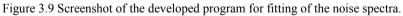

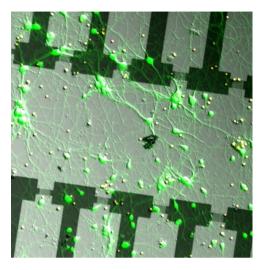

| 3.4.1  | Nanowire test pattern                                                  | 68  |

| 3.4.2  | Cell culture                                                           | 68  |

| 3.4.3  | Live/dead staining                                                     | 69  |

| 3.4.4  | Cell fixation                                                          |     |

| 3.5 Si | ımmary                                                                 | 71  |

| 4. RES | SULTS AND DISCUSSION                                                   | 72  |

| 4.1 Si | licon nanowire FETs based on single wire                               | 72  |

| 4.1.1  | Introduction                                                           |     |

| 4.1.2  | Charge and voltage sensitivity of Si NWs                               |     |

| 4.1.3  | Influence of the liquid gate electrolyte on Si NW transport properties |     |

| 4.1.4  | Role of the NW parameters in the NW FET device characteristics         |     |

| 4.1.5  | Spectra of transconductance of Si NW FET.                              |     |

| 4.1.6  | Summary                                                                |     |

|        | NW array FET structures for neuronal cell interfacing                  |     |

| 4.2.1  | Design considerations for Si NW array FET                              |     |

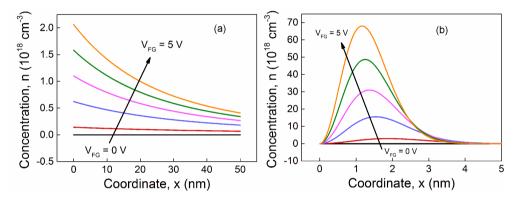

| 4.2.2  | Simulation of front-back gate coupling in Si NWs                       |     |

| 4.2.3  | Enhancing sensitivity of Si NW FET by liquid-back gate coupling        | 111 |

| 4.2.4  | Patterning PLL on Si NW FET structures                                 | 123 |

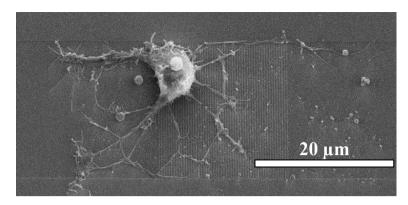

| 4.2.5  | Investigation of Si NWs / neuronal cell interface using FIB            |     |

| 5. CO  | NCLUSIONS AND OUTLOOK                                                  |     |

| REFER  | ENCES                                                                  |     |

| PERSO  | NAL PUBLICATIONS LIST                                                  |     |

#### Abstract

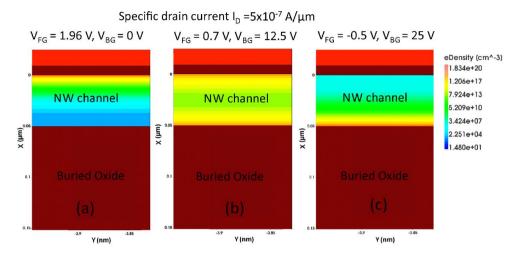

During last decade silicon nanowire (NW) field effect transistors (FETs) attracted considerable attention of researchers as perfect candidates for development of highly sensitive and reliable biosensors, which are compatible with cost-efficient CMOS technology. Recently the liquid-gated FETs were used to demonstrate proof of principle extracellular measurements of neuronal cells action potential, which is of great interest regarding the large variety of applications like monitoring of electrical communication within neuronal networks, transmission paths of ionic channels etc. The NWs are expected to provide an improved contact between neuronal cells and NW surface, which is of crucial importance for signal transduction from the cell to the channel of the NW. However, it is still challenging to establish robust tool for the extracellular monitoring of electrogenic cell activity. One of the important milestones of the research in this area is the signalto-noise ratio (SNR), which determines the detection limit of such type of sensors. Therefore, current work is devoted to design, technology development and fabrication of Si NW FET structures for neuronal cell interfacing and characterizing of their transport properties and reliability utilizing technique of noise spectroscopy. During the work we study the transport properties of single Si NW FET transistors, in order to improve understanding of the factors influencing SNR of the NW biosensors. The results demonstrate modulation effect of the channel current by single trap located in the gate dielectric, which reflects extreme charge sensitivity of the NW FET devices. Arising from these investigations we developed and fabricated the Si NW FET structures based on arrays of 50 NWs connected in parallel. Fabricated liquid-gated NW FET structures are characterized in order to find optimal regimes of operation. The revealed front-back gate coupling effect was used to improve the SNR of the fabricated devices by 50%. According to our measurements, the developed Si NW FET structures meet the requirements needed for extracellular detection of the neuronal cell activity. The interface between neuronal cells and fabricated structures was studied using FIB technique. The results demonstrate that the cells contact NWs without a cleft.

#### Zusammenfassung

In den letzten Jahren haben Silizium-Nanodraht (NW) Feldeffekttransistoren (FETs) bei Forschern großes Interesse geweckt als perfekte Kandidaten für die Entwicklung von hochempfindlichen und robusten Biosensoren, die mit kostengünstiger CMOS-Technologie kompatibel sind. Seit kurzem werden NW-FETs mit einem Elektrolyt-gesteurten Gate verwendet, um grundsätzliche Machbarkeit extrazellulärer Messungen vom Aktionspotential der neuronalen Zellen aufzuzeigen, da diese von großem Interesse sind im Hinblick auf verschiedene Anwendungen wie die Überwachung von elektrischer Kommunikation innerhalb der neuronalen Netzwerke, Übertragungswege der Ionenkanäle usw. Silizium-Nanodrähte sollen einen verbesserten Kontakt zwischen neuronalen Zellen und NW-Oberfläche vermitteln, der für die Signalübertragung von der Zelle auf den jeweiligen Kanal der NW von herausragender Bedeutung ist. Allerdings gibt es noch einige Herausforderungen in der Etablierung eines robusten Werkzeugs zur extrazellulären Überwachung der Aktivität von elektrisch aktiven Zellen. Einer der wichtigen Meilensteine der Forschung in diesem Bereich ist das Signal-Rausch-Verhältnis (SNR), das die Empfindlichkeit von dieser Art von Sensoren bestimmt. Die vorliegende Arbeit widmet sich daher dem Design, der Entwicklung der Technologie und der Herstellung von Si NW FET-Strukturen für die extrazelluläre Ankopplung von neuronalen Zellen und der Charakterisierung ihrer Transporteigenschaften und Zuverlässigkeit unter Verwendung leistungsfähiger Methode der Rausch-Spektroskopie. Im Verlauf dieser Arbeit wurden die Transporteigenschaften von Si NW FET Transistoren untersucht, die auf einzelnen Nanodrähten basieren, um das Verständnis der Einflussfaktoren auf das SNR der NW Biosensoren zu verbessern. Die Ergebnisse zeigen insbesondere einen Modulationseffekt des Kanalstroms durch singuläre Falle im Gate-Dielektrikum, der die extreme Empfindlichkeit zu der Ladung von NW FET Bauelementen wiederspiegelt. Auf Grund von diesen Untersuchungen wurden von uns die Si NW FET-Strukturen basierend auf Anordnungen von 50 parallelgeschalteten Nanodrähten entwickelt und hergestellt. Die hergestellten NW FET-Strukturen wurden elektrisch charakterisiert, um ein optimales Betriebsregime zu finden. Die untersuchte Front-Back-Gate-Kopplungswirkung in den NW FETs wurde zur Verbesserung des Signal-Rausch Verhältnisses um 50% genutzt. Nach unseren Messungen, erfüllen die entwickelten Si NW FET-Strukturen die Anforderungen für extrazelluläre Detektion, neuronaler Zellaktivität. Die Schnittstelle zwischen neuronalen Zellen und hergestellten NW Strukturen wurde darüber hinaus mit fokussierter Ionenstrahl (FIB) untersucht. Die Ergebnisse zeigen, dass die Zellen in direkten Kontakt mit der Oberfläche der NW Strukturen treten.

#### Acknowledgements

I would like to express my gratitude to my supervisor **PD. Dr. Svetlana Vitusevich** for guiding me through the scientific process during all my time in the Forschungszentrum Juelich. Your great positive energy makes the whole workflow effortless and encourages all the members of your team for new scientific achievements. The experience I gained from our cooperation is priceless. Thank you very much for being nearby in all the challenging moments.

I am very grateful to **Prof. Andreas Offenhäusser**, who was a great supervisor and mentored my scientific progress during my stay in PGI-8/ICS-8 Institute. Thank you very much for the warm and friendly atmosphere you created in our institute. It was my great pleasure to work under your supervision and I thank you for lots of wise advices you gave me during my work and life in Jülich.

I thank my second referee Prof. Dr. Hendrik Bluhm for reviewing my thesis.

**Dr. Mykhaylo Petrychuk**, your support and our scientific discussions were very valuable, helped to improve my skills and contributed to my research.

I highly appreciate the input from our collaborators: **Dr. S. Feste, Prof. Mantl, Prof. B. Danylchenko, Dr. S. Richter, Dr. A. Kisner and Dr. N. Clement**. Thank you very much for taking part in our experiments and scientific discussions.

I would like to thank my colleagues from the **PGI-8/ICS-8 institute** for the warm and collaborative atmosphere, nice working environment and generous attitude. I feel particularly grateful to **Dr. F. Santoro, J. Schnitker, Dr. P. Rinklin, F. Brings, Dr. V. Maybeck, A. Markov and K. Greben**. Thank you very much, it was my pleasure to learn from you.

Especially I would like to express my sincere gratitude to the teammates, with whom I have spent most of my working time in Juelich: Dr. V. Sydoruk, Dr. A. Kurakin, Dr. O. Gubin, Dr. O. Barannik, Dr. J. Li, I. Zadorozhnyi, N. Piechniakova, V. Handziuk, A. Hlukhova and Dr. V. Pyatnytsia.

I thank all the **technical stuff** of our Institute and our **cleanroom team** for the help I got from you during my work.

I highly appreciate the financial support of the DAAD and IHRS BioSoft programs.

Finally I would like to thank my **parents** and my wife **Kseniya** for great help, support and warm attitude, which makes my life better.

#### 1. Introduction

The tremendous progress in physical and biological in recent years has facilitated deeper understanding of different biological objects even down to a molecular level and thus formed a strong demand on development of highly-sensitive, selective, stable and reliable biosensors[1]-[4] for real-time analysis and monitoring of biochemical reactions in vivo and in vitro. There are numerous biosensing techniques based on different physical principles such as optical, mechanical and electrical methods for monitoring state of the biosystems[5]. Among other techniques using field-effect transistors (FETs) as biosensors stand out as a promising approach due to their ability to directly translate changes of the gate surface potential into modulation of a drain current[6] and therefore the possibility of real-time monitoring of different processes resulting in surface potential changes. In response to the need for increased sensitivity and higher spatial resolution[7], [8], a new generation of nanoscale FET sensors, based on nanowires, nanotubes[2], nanoribbons[9] and graphene sheets[10] has emerged. In particular, silicon nanowire (Si NW) FETs showed themselves as promising biosensors[11]. Their CMOS-compatibility and flexibility in terms of shapes and sizes, as well as the reproducibility offered by silicon processing technology[12], [13] define the Si NW FETs as excellent candidates for such important applications as label-free detection of biological species [14]-[17] and extracellular investigation of electrogenic cell activity[18]-[20].

Investigation of neuronal cells activity is of great interest from point of view fundamental biophysics as well as for large variety such applications as monitoring of electrical communication within neuronal networks, transmission paths of ionic channels, the use of neuronal networks as biosensor to monitor pharmaceutical agents, pollutants etc. Studying the behavior of grown in vitro neuronal networks gives an overview about functioning of much more complex systems like brain and improves understanding of cell communication at a single synaptic level[21], [22]. These kinds of studies can be strongly facilitated by novel methods of effective bi-directional communication with living cells grown in vitro. Therefore, during last decades several techniques for recording cell activity were developed: glass micropipette[23] and patch clamp electrodes[24], voltage-sensitive dyes[25], microelectrode arrays (MEAs)[26], [27], FETs [28], [29]. Among these approaches MEA and FET techniques have advantages due to improved spatial resolution and direct multiplexed detection of the signal[30]. Another important feature of these approaches is realization of the non-invasive communication with cells. MEAs are considered as prototypes of

# Chapter 1. Introduction

brain-machine interface[31]. Further improvement of MEA technique required not only development of stable electrode tolerant to chemical reactions on the electrodes, but also different methods of excitation and recording using FET technology. At the same time, FETs approach enables direct monitoring of the brain activity and hence, this technique for neuronal interfacing attracts most attention in the last decade. However, implementation of the FET based readout from neuronal cells is a challenging task especially if we are speaking about small cell densities on the chip or even single cells.

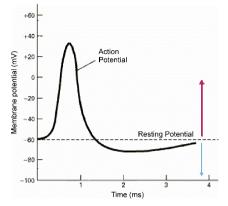

The state of a single cell or cell system can be monitored by either their metabolic products (in the case of the chemical synapse - neurotransmitter) or extracellular potential monitoring. Such a biochemical sensing of compounds released from the cell during action potential requires much effort on functionalization of the FET surface for selective detection of the substances produced by the cells. Instead, for investigation of the electrogenic cells activity (e.g. neuronal cells) one can utilize their specific features like generating of spontaneous or triggered action potentials and measure shifts of the cell membrane potential. The activity of a neuron leads to jonic- and displacement currents flowing through the cell membrane, resulting in an extracellular voltage drop along the cleft between the cell membrane and the gate insulator of the ion sensitive FET[32]. This voltage drop can be recorded as it modulates the drain current of a FET [33]. However, planar FET technique cannot entirely monitor the different complex processes taking place in the system FET - neuronal cell. The main reasons for this are low spatial resolution and the high cleft between silicon oxide surface and the neuronal cell, which can be up to 100 nm over the sensor surface [34]. Such a large distance makes the seal resistance of the cell over the sensor very small and leads to drastic reduction of useful signal[35]. Therefore, the signal can be also determined not by direct transfer of the membrane potential but due to fluxes of ions, which accompany repolarization of the cell and influence the surface potential of the gate dielectric. In order to get reasonable signal, there is a need to culture cells in a stable way onto the FETs and the interface between them and the gate dielectric should provide reasonable seal resistance. The cleft between neuronal cell and the sensor surface can be shrunk down to 4nm using silicon nanowires (NWs) as transducer. This was confirmed in first studies related to the topic on nanowires produced by bottom-up process [30], [36]. The bottom-up processed nanowires, usually fabricated by chemical vapor deposition, are cheap and easy to produce, but these wires have irreproducible sizes and exhibit problems with alignment of the nanowires and contacting them. In contrast, another method of NW fabrication is the top-down approach, which is based on lithographical patterning of the Si wafer and allows fabricating highly reproducible, stable and nanowire devices using complementary metal-oxidesemiconductor (CMOS)-compatible fabrication processes.

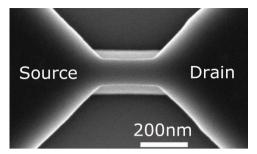

Si NW FETs designed for monitoring neuronal cell electrogenic activity should be able to register discrete events of neuronal cell action potential by extracellular changes of the gate potential in frame of real-time recording. Therefore, measurement techniques based on averaging of the signal over time are not applicable and the signal-to-noise ratio (SNR) of the raw output from the sensor should be higher than one. Implementing such strong requirements is a rather challenging task while working with extremely small signals, such as extracellular recordings from a single cell. Thus, the important milestone of the research in the area of NW-based biosensors for monitoring living cells activity is the signal-to-noise ratio (SNR)[9], [37]. Understanding of the factors influencing the SNR in Si NW FET sensors is of crucial importance for development of reliable NW biosensors with sufficient sensitivity. The SNR of a FET sensor is determined by the transconductance,  $g_m$ , of the Si NW transistor and by the intrinsic noise of the device. Therefore, the SNR can be improved both by optimization of the fabrication technology [38], [39] and by finding the optimal transport regimes to maximize the sensitivity[40]–[42]. The Si NW transistors are fabricated using wet chemical etching to improve quality of the sidewalls of the FET devices and reduce surface noise[43].

According to the above-discussed challenges, this work is devoted to the development of Si NW structures sensitive and reliable enough for effective extracellular monitoring of the neuronal cells activity in vitro. We consider both methods of improving device sensitivity: optimizing fabrication technology and operation mode of the NW FET. As a feedback for improving device characteristics we utilize noise spectroscopy – a powerful approach for investigating device performance and structure. The structures in the presented work were designed in different geometries in order to investigate influence of the channel parameters on SNR. After the fabrication of Si NW FETs, the SNR of produced devices was enhanced by finding optimal regime of the operation. We have shown significant improvement of the SNR by utilization of the front-back-gate coupling effect. Analysis of experimentally obtained data using existing models of noise behavior has shown switching of scattering mechanism under influence of back gate biasing.

# Chapter 1. Introduction

The above discussed is implemented in the objective of the presented work: fabrication of stable, reliable and sensitive Si NW FET transistors optimized for biosensor measurements of electrogenic cell activity. The objective is achieved by fulfilling following scientific tasks:

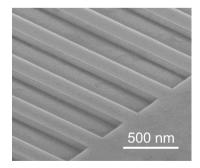

- Fabrication and design of high-quality Si NW FET structures for providing improved interface between cells and the NW surface.

- Characterization of fabricated structures using electron microscopy and electrical characterization using noise spectroscopy in order to improve understanding of the factors influencing the sensor performance.

- Investigating influence of the electrolyte gate on performance and SNR of Si NW FET devices for excluding role of the surface effects on the transport in Si NW FETs

- Identifying influence of different NW parameters, such as contact resistance, charge carrier distribution on transport properties of a NW FET by means of theoretical modelling and noise spectroscopy.

- Analysis of Si NW / neuronal cell interface using focused ion beam (FIB).

- Simulation of the fabricated devices in Sentaurus technology and computer aided design (TCAD) program for establishing directions for improving the device fabrication technology and performance.

- Investigation of the SNR of fabricated Si NW array biosensor devices by studying regimes of the operation and influence of the geometry of the NW FETs.

- Test measurements of the fabricated nanowire structures using pulse signals with characteristics similar to neuronal cell action potential.

# 2. Theoretical, experimental background and state of the art

### 2.1 Silicon nanowire based biosensors

#### 2.1.1 Introduction

Complementary metal oxide semiconductor (CMOS) field-effect transistor (FET) technology has been extensively developed since date of its invention in 1963. Success of the CMOS technology is based on constant improving of the device characteristics, fabrication technology and cost-efficiency driven by society and market demand. The dimensions of the FETs, as elementary units of the CMOS technology, are decreasing following the Moor's law[44], [45]. When the characteristic dimensions of the MOSFET have dropped down to the size of 1 micron, further miniaturization became challenging due to appearing of the short-channel effects [46], [47]. The solution for these challenges is using novel device geometries like devices with buried oxide [48], FinFETs [49], gate-all-around FETs [50] as well as NW FETs. The NW FET is the next step for miniaturization of CMOS devices.

Convenience and availability of nowadays CMOS technology makes production of CMOScompatible electronic devices extremely favorable from the point of view of cost efficiency, device reproducibility and reliability. Therefore the idea of using FET for sensing of the gate potential has evolved into idea of sensing surface potential in electrolyte using CMOS-compatible liquid-gated FET[51]. The device developed for this purpose is an ion-sensitive field effect transistor (ISFET) and is used to sense pH of different solutions[52], [53]

#### 2.1.2 Ion-sensitive field effect transistors as biosensors

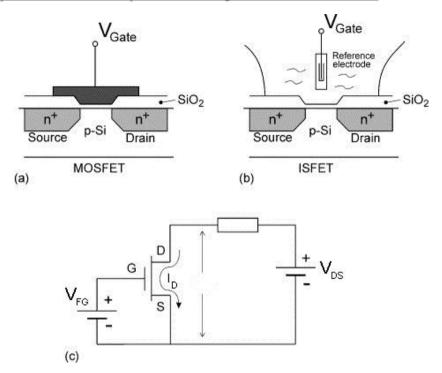

Since its invention ISFETs have been utilized not only as pH sensor but also in a variety of applications including biosensing [54]. The basic principle of ISFET lies in replacing of a metal gate of the MOSFET by electrolyte gate. Figure 2.1 shows schematic comparison of a MOSFET and an ISFET [53]. In the case of the ISFET the drain current of the FET is defined by a potential of the electrolyte, which is in its turn defined by the reference electrode.

Chapter 2. Theoretical, experimental background and state of the art

Figure 2.1 Schematic representation of (a): MOSFET, (b): ISFET and (c): electronic diagram for measurement with grounded source scheme. The figure is adapted from [53].

The drain current,  $I_D$ , in the schematic (c) of Figure 2.1 is defined in the same way for both MOSFET and ISFET in the non-saturated mode[55]:

$$I_D = C_{ox} \mu \frac{W}{L} \left[ (V_{FG} - V_{Th}) V_{DS} - \frac{1}{2} V_{DS}^2 \right],$$

(2.1)

where  $C_{ox}$  is the gate oxide capacitance per unit area,  $\mu$  is the mobility of the charge carriers in the channel of the FET, W is the width of the channel, L is the length of the channel,  $V_{FG}$  is the front gate voltage,  $V_{DS}$  is the drain-source bias,  $V_{Th}$  is the threshold voltage. According to Eq. (2.1) the drain current of the FET can be changed via changing drain-source bias or the gate voltage. The gate voltage influences charge carrier distribution and concentration in the channel. If  $V_{FG}$  is higher than  $V_{Th}$ , then transistor is considered to be in an open state. At gate voltages below the threshold a diffusion current is dominating the drift component. The threshold voltage is the term, which

contains the initial surface potential (including interface potential of Si/SiO<sub>2</sub>) needed to overcome by gate voltage to open the transistor channel. In the case of a MOSFET,  $V_{Th}$  contains difference between workfunctions of metal gate and silicon,  $\phi_M$  and  $\phi_{Si}$ , potential of the charges accumulated in the gate oxide,  $Q_{ox}$ , charges captured to the surface states,  $Q_{ss}$ , and charges of the space charge region,  $Q_{scr}$ , and difference between Fermi level and middle of the bandgap ,  $2\phi_f$  [53], [55]:

$$V_{Th} = \frac{\phi_M - \phi_{Si}}{q} + \frac{Q_{ox} + Q_{ss} + Q_{scr}}{C_{ox}} + 2\phi_f.$$

(2.2)

In the case of ISFET the threshold voltage also incorporates surface potential of the interface electrolyte/gate oxide and the metal workfunction is replaced by the potential of a reference electrode,  $E_{ref}$ , in the electrolyte:

$$V_{Th} = E_{ref} - \psi_0 + \chi_{sol} - \frac{\phi_{Si}}{q} + \frac{Q_{ox} + Q_{ss} + Q_{scr}}{C_{ox}} + 2\phi_f,$$

(2.3)

where  $\psi_0$  is the potential generated by adsorbed ions on the surface and  $\chi_{sol}$  is the surface dipole potential of a solvent. Changes of the threshold voltage leads to a shift the whole transfer curve of the transistor along the gate voltage axis. At a constant  $V_{FG}$  changing of the  $V_{Th}$  results in changes of the drain current, according to Eq. (2.1).

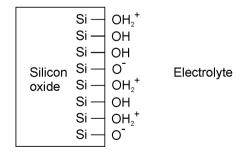

Surface potential of the ISFET in the electrolyte depends on quantity of adsorbed on the gate dielectric H<sup>+</sup> ions. Channel of an ISFET sensor is usually covered by oxides such as SiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub> and Ta<sub>2</sub>O<sub>5</sub> [52]. The surface has ion binding sites, which adsorb hydrogen ions [56].

Figure 2.2 Schematic diagram of the Silicon oxide/electrolyte interface adapted from [57] The following reactions take place at the surface of gate dielectric [58]:

$$AOH \rightleftharpoons AO^- + H_s^+, \qquad AOH_2 \rightleftarrows AOH + H_s^+,$$

$$(2.4)$$

where A – atom of silicon (aluminum or other oxide forming element),  $H_S$  – hydrogen atoms in close vicinity to the interface. After establishing equilibrium at the interface, the reactions (2.4) run at constant reaction rate in both directions. So the equilibrium dissociation constants can be defined as:

$$K_a = \frac{[AO^-][H_s^+]}{[AOH]} \text{ and } K_b = \frac{[AOH_2]}{[AOH][H_s^+]},$$

(2.5)

where square brackets are used to define concentrations of ions or compounds. After reaching the equilibrium state also an equilibrium surface potential will be established. It is determined by surface concentration of the hydrogen atoms,  $[H_s^+]$ , which in its turn is defined by the concentration of the hydrogen ions in the bulk of the electrolyte[59]:

$$[H_s^+] = [H^+]e^{-\frac{q\psi_0}{kT}},$$

(2.6)

where q – is the elementary charge,  $\psi_0$  – is the potential of the interface dielectric/electrolyte, k – is the Boltzmann constant, T – is the temperature in Kelvin. As it can be seen from Eq. (2.6), concentration of the of the hydrogen ions on the surface is related to the bulk concentration of hydrogen ions through the surface potential. Thus, taking into account the conservation of quantity of binding sites  $N_S$ :

$$N_S = [AOH] + [AO^-] + [AOH_2^+]$$

(2.7)

and the charge per unit area  $\sigma_0$ :

$$\sigma_0 = q([AOH_2^+] - [AO^-]), \tag{2.8}$$

one can obtain a relation between interface potential and pH of the solution[51]:

$$\psi_0 = \left(2.303 \frac{kT}{q}\right) \left(\frac{\beta}{\beta+1}\right) \left(pH_{pzc} - pH\right),\tag{2.9}$$

where  $pH_{pzc}$  is the pH value at which the point of zero charge is reached and  $\beta$  is a dimensionless sensitivity coefficient:

$$\beta = \frac{q^2 N_s \delta}{C_{eq} kT'},\tag{2.10}$$

where  $\delta = 2 (K_a K_b)^{\frac{1}{2}}$ ,  $C_{eq}$  is the equivalent capacitance of the interface adopted from Gouy-Chapman-Stern theory for double layer. The equation (2.9) reflects the sensitivity of the surface potential to the pH of the electrolyte solution. As we can see from Eq. (2.3)  $\psi_0$  is included to the threshold voltage of an ISFET and therefore changes of  $\psi_0$  lead to changes of the  $V_{Th}$ , which can be detected by shift of the ISFET transfer curves. Using Eq. (2.9) a maximum sensitivity of the surface potential to the pH can be estimated. It equals 59 mV/pH and is called a Nernstian limit [51]. This limitation has fundamental origin. Nevertheless, there are publications revealing supernernstian behavior of some surfaces and devices[60], [61]. However, such a behavior can be explained in a way, which does not violate the Nernstian rule.

Equations (2.6) and (2.9) demonstrate that concentration of adsorbed hydrogen ions on the surface of the gate dielectric is defined by the bulk concentration of ions and determines a surface potential of the gate dielectric. The theory of the pH sensitive ISFET considers only binding of the simplest ions to the surface of the transistor, because binding of other heavier ions is less probable then adsorption of H<sup>+</sup>. At the same time, modification of the transistor surface with specific chemistry can make the adsorption ion-specific [62], [63] and thus enable detection of various species like DNA, proteins, antibodies[54], [57]. Such a modification combined with field effect sensing makes a background for fabrication of field-effect based biosensor. However, demand of modern biology and biomedicine in sensitivity and spatial resolution requires downscaling of the transducer down to submicron sizes and even to nanometer scale[8], [64]. Increasing sensitivity of the sensors is usually achieved by increasing resolution of measuring changes of the  $\psi_0$ [41], [42], [65], because sensitivity of  $\psi_0$  to the ion concentration is limited by the nernstian rule. One of the possible ways to increase the charge sensitivity of the devices is using novel confined geometries like Si NW FETs[66].

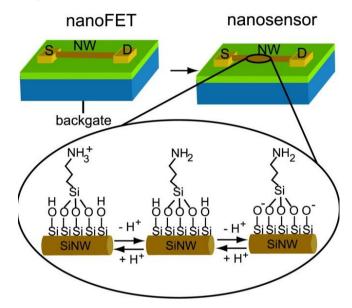

#### 2.1.3 Silicon nanowire FET biosensors.

Silicon nanowire FET biosensors have emerged as a next step of miniaturization of an ISFET[11], [67] due to enhanced sensitivity[68] and spatial resolution[69] provided by small size and high surface-to-volume ratio. The first nanowire structures were used for detection of ionic composition of the electrolyte [70], biomolecules[71] and biomarkers[15]. They show higher

charge sensitivity than bulk ISFETs. Figure 2.1 demonstrates a schematic representation of NW FET biosensor. The surface of the NW is often covered with (3-Aminopropyl)triethoxysilane (APTES) in order to provide protection of Si NW surface and possibility for further selective modification of the NW gate[70].

Figure 2.3 Schematic image of Si NW FET with the sketch of the NW pH sensing after silanization procedure. The figure is adapted from [70].

The first attempts of fabrication of Si NW FET biosensors have demonstrated proof of principle of biomolecule detection[72]. However, the nanowire biosensors were first fabricated using a "bottom-up" approach. In this case he Si NWs are usually fabricated by means of chemical vapor deposition or using wet chemistry and then they are contacted[73]. This approach has advantage of cost-efficiency and high crystalline quality of the produced NWs provided by self-organized silicon nanowire growth. On the other hand fabrication of bottom-up nanowires requires additional attention to be drawn to achieve uniformity of the size distribution[74] as well as steps for integration of the NWs with CMOS circuitry and assembling them in desired direction[75], [76]. Alternative way of fabrication is entirely based on the CMOS technology and is called "top-down" approach [73], when the NW structures are patterned on the silicon substrate using

lithographic procedures like e-beam lithography or deep UV lithography. This method is more expensive than the bottom-up production, but it provides highly reliable and reproducible devices, which are easy to integrate and scale down[77]. Effective detection of biomolecules has also been demonstrated using Si NW FETs produced by top-down approach[14], [78]. Moreover the power of CMOS downscaling and integration has been used for development of ultimate commercial device for full sequencing of 20-basepair DNA based on Si NW FETs[79].

In presented work we have chosen the top-down approach in order to have full control of the nanowire dimensions and achieve highly reproducible devices.

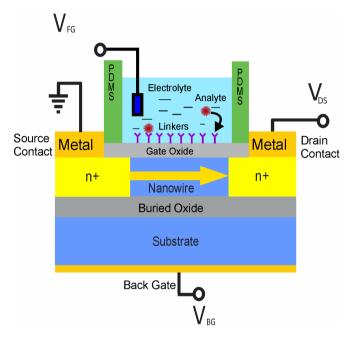

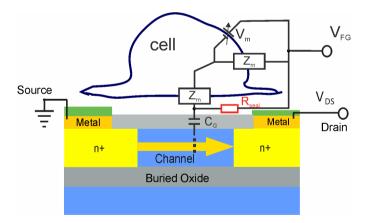

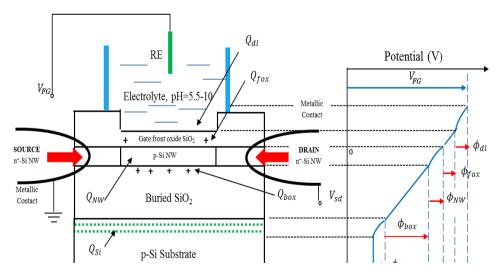

The schematic illustration of the Si NW FET fabricated using top-down approach is shown on Figure 2.4. The NW is passivated with thin oxide layer (typically from 5 to tens of nanometers) and then exposed to an electrolyte solution. Contact regions are protected from liquid using organic materials like polydimethylsiloxane (PDMS) and/or photoresists like SU8 or PI2545. In order to achieve ohmic contact between NW and metal contact pads, outer regions of the NW are heavily implanted[55].

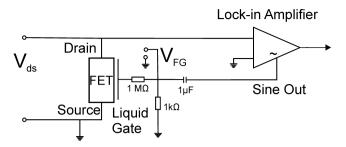

For the electric measurements NW FETs are usually connected in the grounded source configuration as it is shown in Figure 2.4. The drain voltage,  $V_{DS}$ , as well as front-gate voltage,  $V_{FG}$ , and back-gate voltage,  $V_{BG}$ , are set against the source, which is connected to the ground. Front gate voltage is applied using Ag/AgCl reference electrode. Reference electrode can be integrated directly on the chip[80] or it can be realized in form of reference FET sensor, which serves as a reference for determining all potentials in the system [81]. The back gate voltage can be used to tune the NW's threshold voltage and the operation mode[82] as well as for increasing sensitivity of the device [40]. Electrical transport characteristics of Si NW FETs can be qualitatively described in the frame of classical model of a MOSFET[55] (see Eq. (2.1)) with small amendments. If we consider a linear mode, when the transistor is operated at a relatively small  $V_{DS}$ , the Eq. (2.1)will be simplified to:

$$I_D = C_{ox} \mu \frac{W}{L} (V_{FG} - V_{Th}) V_{DS}.$$

(2.11)

Eq. (2.11) is similar to the basic definition of the drift current:

$$I_{D} = nevS = \frac{N}{WLH} e\mu E_{DS}WH = eN\mu \frac{V_{DS}}{L^{2}} = \frac{eN}{L}\mu \frac{V_{DS}}{L},$$

(2.12)

23

where n – is the carrier concentration, H – is the channel height,  $E_{DS}$  – is the drift electric field, N is the quantity of charge carriers, e – is the elementary charge. Now if we compare Eq. (2.12) and (2.11) we can see that  $C_{ox}W(V_{FG} - V_{Th})$  represents quantity of carriers in the channel per unit length attracted by the gate voltage,  $V_{DS}/L$  represents the electric field between source and drain electrodes.

Figure 2.4 Sketch of the liquid-gated Si NW FET (the side view). The image represents Si NW with contact regions implanted with As atoms. The schema illustrates electric connection of the Si NW FET in the grounded source configuration.

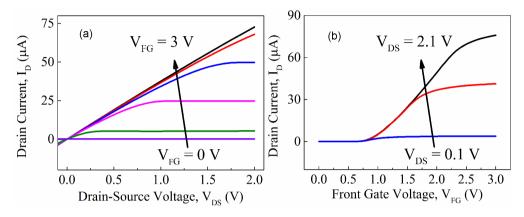

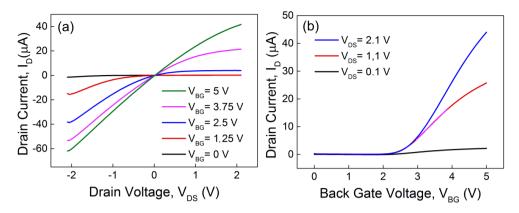

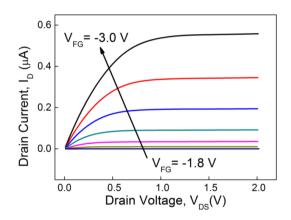

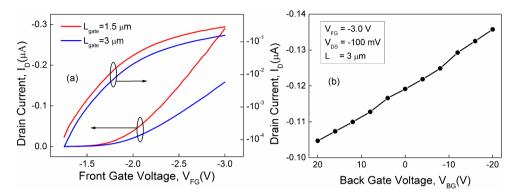

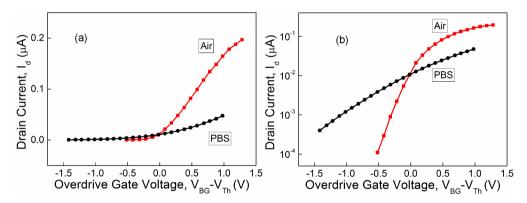

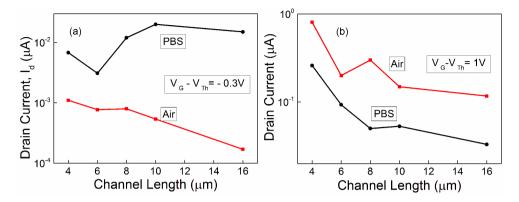

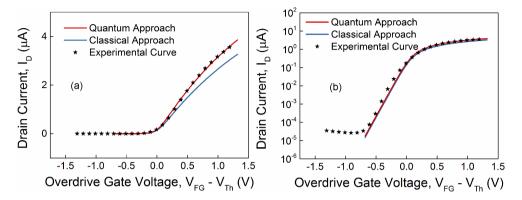

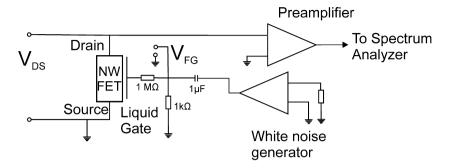

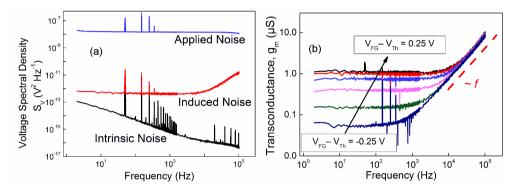

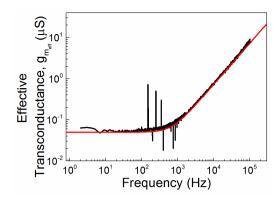

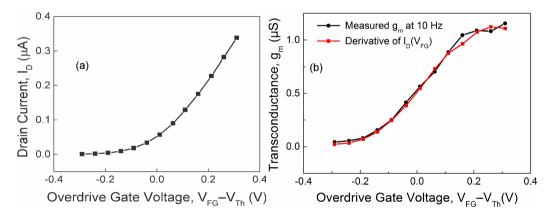

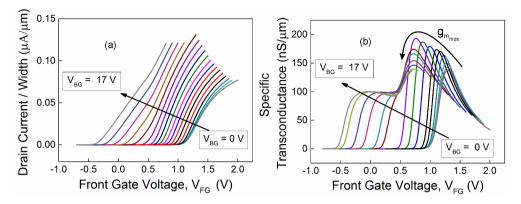

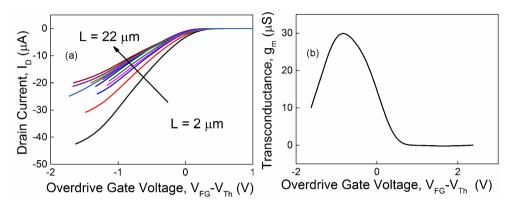

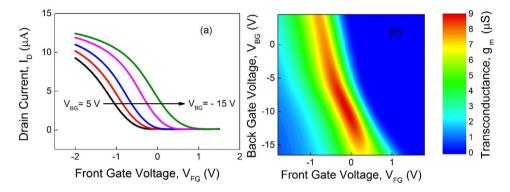

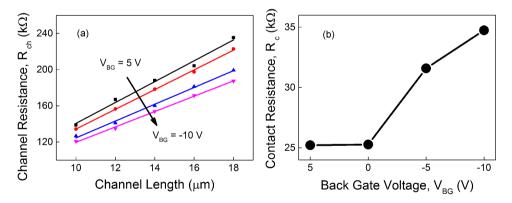

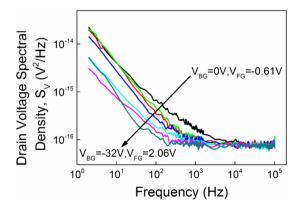

Linear mode of operation can be used to characterize the device transport properties such as channel mobility and concentration of the carriers in the channel. Figure 2.5 shows typical output and transfer characteristics of Si NW array FET, measured in a configuration from Figure 2.4. The devices characterized in Figure 2.5 were fabricated in the frame of present work and represent Si NW FETs based on array of 50 NWs connected in parallel in order to improve signal-to-noise ratio and preserve nanostructured surface. Linear mode of the transistor can be observed in Figure 2.5(A) from  $V_{DS}$ =0 V, to 0.5 V for most of the front gate voltages. Transistor channel can be treated as a

resistor in the linear mode, whereas at higher drain voltages it reaches the saturated mode, when drain current is almost independent of the drain voltage due to channel pinch-off[55]. Figure 2.5(B) demonstrates transfer characteristics of the Si NW FET. The changes of gate voltage are translated into changes of drain current. The threshold voltage of this device is calculated using Eq. (2.11) and is equal 0.88 V.

Figure 2.5 I-V characteristics of liquid-gated Si NW array FET (channel length of 6μm, width of 250 nm, device consists of 50 NWs connected in parallel) with As doped contact regions. (A): Output characteristics, (B) Transfer characteristics.

One of the main characteristics of a transistor is the transconductance,  $g_m$ , which is the measure of the gate control over the drain current.

$$g_m \equiv \frac{\partial I_D}{\partial V_{FG}}\Big|_{V_{DS}=const} = \frac{W}{L} \mu C_{ox} V_{DS}.$$

(2.13)

As we can see from Eq. (2.13) and Figure 2.5(B), the  $g_m$  is proportional to the drain voltage of the transistor. Therefore, the real sensor measurements are usually carried out in the saturation mode of the transistor at possibly higher drain biases, to get maximal level of the transconductance. However, the channel noise should be also taken into account when choosing a working point for measurements. As it has been discussed above, characterization of the transistor is usually done at low drain biases in order to simplify the data extraction and provide quasistatic conditions for carriers in the channel. For example, it is possible to estimate mobility and concentration of the carriers in the channel using Eq. (2.13) and the Eq.(2.12):

Chapter 2. Theoretical, experimental background and state of the art

$$\mu = \frac{g_m L}{W C_{ox} V_{DS}} \tag{2.14}$$

$$n = \frac{I_D C_{ox}}{q g_m H} \tag{2.15}$$

where H – is the height of the NW channel channel. It should be noted, that this FET model does not consider carrier distribution in the channel, but it is still suitable for estimations. Role of carrier distribution in the channel is considered in [83]. The classical prediction describes macroscopic characteristics of Si NW FETs until very small sizes (down to characteristic size of 20 nm in all directions). Beyond this limit a quantum behavior of the NW structures can be observed[84]–[86] even at room temperature.

One of the potential problems for estimation of the values from Eq. (2.14) and (2.15) is evaluation of the gate capacitance per unit area,  $C_{ox}$ , which in case of complicated geometries like gate-all-around transistors and low dimensional structures deviates from the well-known plain capacitor equation. The violations of the parallel-plate capacitor model can already occur at submicron scale of the transistors. The most efficient way to consider this problem is performing an experimental measurement of the gate capacitance. The measurement of gate capacitance of germanium NW FETs has been reported in [87]. However, such an approach requires sophisticated measurement technique in order to recover capacitance values far below parasitic capacitance of the cabling. Alternative to this approach may be using coupling of back and front gate of the Si NW FET in order to evaluate the front gate capacitance[88].

As we have discussed above, selectivity of the NW FETs is achieved by chemical functionalization of the NW surface[89]. The wires are covered with a layer of molecules, which will selectively adsorb analyte molecules from the solution[90]. An examples of such specific surface chemistry are single-stranded DNA[79], antibodies[12], [14] and emerging aptamers[91]. Working principle of functionalized NW FET sensors is similar to what we have shown for the case of an ISFET and different pH of the electrolyte gate solution. Adsorption of the analyte molecule onto the linker molecule results in changes of the surface potential, which can be registered in the channel by changes of the drain current or other parameters[92]. Linker molecules are usually connected to the gate dielectric of the sensor through an intermediate layer of organic

molecules, which have on one side chemical affinity to the material of the gate (silicon oxide or other oxides, silicon) and on the other side organic or inorganic radical, which simplifies binding to the linker molecules. There are several approaches of Si NW FETs functionalization: direct functionalization of silicon surface with polymer brush of alkyl-ended molecules[93]–[97]; functionalization of the gate oxide with silane containing organic compounds[98], [99]; covering the surface of the sensor with a selective membrane, which translates selective chemical adsorption into changes of the pH at the surface of the NW[100]. In the case of chemical modification of the surface of the sensor, because uncovered places of the sensor can give false contribution to the signal due to unspecific adsorption. Besides, imperfections of the polymer brush in case of alkylation of silicon surface directly lead to the gate leakage and thus sensor failure. All of the discussed approaches of Si NW functionalization have their advantages and disadvantages, which may be favorable for different applications.

Silicon nanowire field effect transistors are promising structures for monitoring the activity of living cells, particularly electrogenic cells like neurons[101], [102] and heart cells[103]. The state of a single cell or cell system can be monitored by either their metabolic products (in the case of the chemical synapse - neurotransmitter) or extracellular potential measurements. Bio chemical sensing requires much effort on functionalization of the sensor surface for selective detection of the substances produced by the cells. For investigation of the electrogenic cells activity (e.g. neuronal cells) one can utilize their specific features like generating of spontaneous or triggered action potentials and measure shifts of the cell membrane extracellular potential. The activity of a neuron leads to ionic- and displacement currents flowing through the cell membrane, resulting in an extracellular voltage drop along the cleft between the cell membrane and the gate insulator of the ion sensitive FET that modulates its drain current[33].

The detection of electrical signal from neuronal cells has been demonstrated using traditional FET technique [28]. However, planar FET technique cannot entirely monitor the different complex processes taking place in the system FET/ neuronal cell in the transistor signal. The main reason for this is low spatial resolution. In addition, the cleft between silicon oxide passivated surface and the neuronal cell is about 40 nm [34] which is 4 times larger than Debye screening length in physiological solution (about 10 nm). Distance between cell and surface of the detection spot determines the value of so called seal resistance  $R_{seal}$  (will be discussed in more later

# Chapter 2. Theoretical, experimental background and state of the art

on), which is a measure for leakage of the useful signal to the bulk electrolyte. That's why in the case of a planar FET the signal outcome from the cell may be determined not by direct transfer of the membrane potential but by the fluxes of ions, which accompany repolarization of the cell and influence the surface potential of the gate dielectric. The cells have to be cultured in a stable way onto the FETs and the interface between them and the gate dielectric should be improved. The cleft between neuronal cell and the sensor surface can be shrunk down to 4nm using Si NW FETs. This was confirmed in first studies related to the topic [30], [36] on nanowires produced using bottom-up process. However, as it was discussed above, the bottom-up processed nanowires grown by chemical vapor deposition are cheap and easy to produce, but these wires have irreproducible sizes and may experience complications with integration. The top-down produced Si NWs for neuronal cell interfacing are still under development[101]. The main challenges are signal-to-noise ratio of Si NW FETs and stability in liquid environment during at least 10 days in vitro.

#### 2.1.4 Signal-to-noise ratio in silicon NW FETs

Silicon NW FET based biosensors represent a big step forward in development of modern biomedicine and biology. However, there are still the challenges remaining to achieve highly sensitive, reliable and reproducible operation. The important milestone of the research in the area of FET sensors is the signal-to-noise ratio (SNR), which determines the detection limit of a sensor [9], [37], [104]. SNR is defined as a relation between useful signal and fluctuations of the device parameters. When we are registering changes of the Si NW FET current, than the registered change will contain component corresponding to the useful signal,  $\delta I_S$ , and as well component corresponding to the channel current fluctuations  $\delta I_{fl}$ :

$$\delta I = \delta I_S + \delta I_{fl}. \tag{2.16}$$

Then, by definition, the SNR will be:

$$SNR \equiv \frac{\delta I_S}{\delta I_{fl}}.$$

(2.17)

It is always advantageous if biosensors detect in real time discrete events, such as binding of the biological objects to the surface or action potentials of an electrogenic cell. Therefore, in a wide range of applications, Si NW FET biosensors have to provide real-time detection of the analyzed

events. In this case, averaging techniques, which usually operate with mean values and are used to suppress noise, are not applicable and the SNR of the raw output from the sensor should be higher than one. Implementing such strong requirements might be a rather challenging task because biosensors are often dealing with extremely small signals, such as monitoring tiny changes of concentration of the analyte or extracellular recordings from a single cell. Therefore, understanding the factors having an impact on the SNR is of crucial importance for developing reliable biosensors with sufficient sensitivity.

Real signals in biological environments are usually extremely small (in the range of tens of microvolts), and hence after a measurement the value of  $\delta I_S$ , generated by the analyte may be below the level of channel noise. Therefore instead of Eq. (2.17), where we compare the response of the NW channel current to the intrinsic noise of the device, it is more suitable to use a relation between input signal  $\delta V_{FG}$  and the level of equivalent input noise  $\delta V_{fl}$  (the effective fluctuation of gate voltage potential, which causes corresponding fluctuation of the channel current  $\delta I_{fl}$ ). The aforementioned can be realized by multiplying the numerator and denominator of Eq. (2.17) by  $g_m$ :

$$SNR = \frac{\delta I_S}{\delta I_{fl}} = \frac{\delta I_S g_m}{\delta I_{fl} g_m} = \frac{\delta V_{FG}}{\delta V_{fl}}.$$

(2.18)

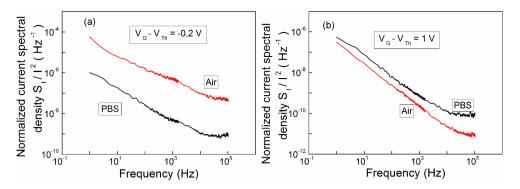

The biosensor signals are usually detected in the low frequency range of spectra. For example, extracellular measurements of action potentials from neuronal cells[28] require detection of signals with average duration about 3 ms, whose principle components are, on average, not faster than 10 kHz. Therefore the signal from sensor  $\delta I$  is often filtered to the frequency range of the input signal in order to remove unnecessary high-frequency fluctuations. In this respect it is more convenient to switch to the spectral representation of the equivalent input noise in Eq.(2.18):

$$SNR = \frac{\delta V_{FG}}{\sqrt{\int_{f_1}^{f_2} S_u df}} = \delta V_{FG} \frac{g_m}{\sqrt{\int_{f_1}^{f_2} S_I df}},$$

(2.19)

where  $S_I$  is the drain current spectral density and  $S_u$  is the equivalent input voltage spectral density. The lower is the value of  $S_u$ , the higher is the SNR.

According to Eq. (2.19) the improvement of the SNR can be realized by finding conditions with the lowest equivalent input noise. Therefore the SNR can be improved by optimization of the fabrication technology [38], [39], to obtain low-noise devices due to high quality of the device

# Chapter 2. Theoretical, experimental background and state of the art

interfaces, and by finding the appropriate transport regimes to maximize the sensitivity. However, to date there remain important challenges in establishing the optimal transistor operation modes for biosensing. Currently, two main concepts are considered for optimization of sensitivity: using the subthreshold mode[105] or above-threshold mode[41]. In the present work we will answer these questions and demonstrate that using each of the modes is advantageous in different applications[40]. Optimization of the sensor structures using chemical wet etching during NW fabrication as well as finding of the optimal regime for low-noise of the NW operation is considered.

Described challenges of the NW biosensing require comprehensive investigation of Si NW FET transport properties as well as the factors having impact on it. Analysis of the current fluctuations in liquid-gated NW FETs combined with data of their I-V characterization derives information about noise sources in the device as well as ways to optimize performance of the sensor. Such an analysis of transport is based on noise spectroscopy, a technique for characterizing the dynamic properties of the investigated structure. In the next section we are going to discuss background of noise spectroscopy in FET devices.

#### 2.2 Noise Spectroscopy

#### 2.2.1 Introduction

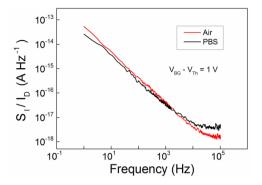

Noise spectroscopy provides analysis of the device performance and structure by studying the fluctuation phenomena. The method itself is very convenient for the extraction of information about the origin of noise in the sample. Noise spectroscopy can be used for the analysis of the device quality, transport properties and improvement of the technology, which is one of the main directions for the development of advanced NW FETs and miniaturization of the CMOS elementary base. A lot of publications are devoted to analysis of fluctuation phenomena in Si NW FETs [41], [66], [106], [107], because the major point of the biosensor performance optimization is improving signal-to-noise ratio. Historically Si NW FET biosensors evolved from regular MOSFET structures. Most of knowledge in the sphere of noise spectroscopy for submicron MOSFET structures is eligible for NW biosensors as well. For example, it has been shown that presence of the electrolyte as a front-gate of a FET biosensor (BioFET) does not influence noise properties of the structure [41]. Therefore we are going to use experience and understanding of

noise in MOSFETs, as it was accumulated over the years of existence of the CMOS technology [108]–[110]. In this section we will consider main noise sources of Si NW transistor.

#### 2.2.2 Spectral density

Drain current of a FET under stationary conditions contains a fluctuation component,  $i_n$ , which is changing in time:

$$I(t) = \bar{I} + i_n(t).$$

(2.20)

Function  $i_n(t)$  is a random value and therefore a mean value of current cannot be used for analysis of the fluctuation, because  $i_n(t)$  gives zero after averaging. The value of mean-square deviation (MSD) is usually used for analysis of the fluctuations:

$$\langle i_n^2(t) \rangle = \lim_{T \to \infty} \frac{1}{T} \int_0^T i_n^2(t) dt.$$

(2.21)

This value gives an idea about the measurement precision and the level of the fluctuations in a biosensor measurement. Practically MSD is the value, which can be used in the denominator of the signal-to-noise ratio of a FET, if we take a root square of it (root mean-square deviation (RMSD)). However, the MSD value is not enough for quantitative analysis of the fluctuation processes. For these purposes a frequency representation of MSD is used – spectral density of fluctuations.

$$\int_{-\infty}^{+\infty} |x(t)|^2 dt = \frac{1}{2\pi} \int_{-\infty}^{+\infty} |\hat{x}(\omega)|^2 d\omega, \qquad (2.22)$$

where x(t) – is some fluctuating value. Any physical quantity can accounted as x(t), it can be current, voltage, power or even a resistance of the sample. Spectral density of x(t) is denoted by  $S_x$  is calculated from time trace of x as follows:

$$S_{x}(\omega) = |\hat{x}(\omega)|^{2} = \left| \int_{-\infty}^{+\infty} x(t) e^{-i\omega t} dt \right|^{2}.$$

(2.23)

Spectral density is an additive value. If fluctuations of the sample current have different origin and do not correlate between each other, then the resulting spectral density will be a superposition of spectral densities of each type of noise. Spectral density of voltage fluctuations can be recalculated into spectral density of current fluctuations using Ohm's law:

$$S_I = \frac{S_V}{R^2},\tag{2.24}$$

where R – is the differential resistance of the sample and circuitry. Eq. (2.24) is very important in measurements of noise, because it allows recalculating desired values by only one measured value:  $S_I$  in case of current amplifier and  $S_V$  in case of voltage amplifier.

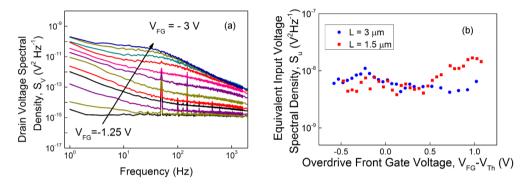

As we have already discussed, sensitivity of Si NW FET biosensors is a hot topic and there is a number of publications in this direction [38], [106], [111]. However, there are still challenges of finding optimal device geometry and operation mode. In the next subsection we will consider typical sources of noise in Si NW FETs. Many of these noise sources are discussed in literature for the case of planar MOSFET and submicron MOSFET [107], [110], [112]–[115].

#### 2.2.3 Main sources of noise in Si NW FET

One of the most important and well-known types of noise is the thermal noise or so called Johnson-Nyquist noise. Thermal noise is present in all objects, which can be characterized with some electrical resistance, which is in thermodynamic equilibrium with its environment. Depending on the schematic of the device connection (open circuit or a shortcut) the thermal noise appears as fluctuations of voltage on the ends of circuit or as fluctuations of current through the sample. Thermal noise has first been observed independently by Johnson[116] and Nyquist[117] in 1928. Using measurements of thermal noise Johnson managed to estimate Boltzmann constant with significant accuracy.

Electrons and holes in a semiconductor have thermal energy and are constantly expressing random thermal motion. The events of scattering on lattice, when carriers can either loose or gain energy due to interaction with lattice atoms, occur randomly and on average compensate each other in the state of thermodynamic equilibrium. Such random motions cause fluctuations of carrier concentration on the terminals of the sample, which result in thermal fluctuations of current or voltage in the circuit. Spectral density of thermal noise is not frequency dependent in a broad frequency range and can be calculated as follows:

$$S_{\nu} = 4kTR, \qquad (2.25)$$

where k – is the Boltzmann constant, R – sample resistance, T – temperature of the sample. Resistance of the sample, as well as temperature can be precisely measured using measurement of level of the thermal noise. It should be noted, that spectral density of the current will be inverse proportional to the resistance according to Eq. (2.24).

$$S_I = \frac{4kT}{R}.$$

(2.26)

According to Eq. (2.25) and (2.26) we can conclude that high-ohmic samples should be measured using current amplifier, whereas measurements of noise in the low-resistance samples is more efficient with voltage amplifier.

As it has been mentioned in subsection 2.1.4, in the case of signal from a biosensor, we are mostly interested in the low-frequency range of spectra (up to 10 kHz). In this frequency region thermal noise is more often dominated by other types of noise like generation-recombination or flicker noise. However if the FET is in the subthreshold mode, which might be considered as optimal in some kinds of experiments [105], the thermal noise can be the major factor, defining voltage spectral density of the investigated sample.

Another type of frequency independent noise is the shot noise [118]. First this noise was described by Schottky in 1918 [119], when he registered this type of noise in the valve diodes. The shot noise appears in the samples, in which the charge carriers should overcome some potential barrier in order to contribute to electric current. The classical examples of such devices are a p-n junction and a Schottky barrier (contact metal-semiconductor). These fluctuations originate from the discreteness of the charge carriers in the current. Discrete charge carriers are randomly passing the potential barrier. As the result current in the sample can be written as a sum of short pulses, where each pulse represents single carrier passing a potential barrier:

$$i(t) = -q \sum_{k=1}^{K} \delta(t - t_k), \qquad (2.27)$$

where q – is the elementary charge,  $t_k$  – moment of crossing a barrier by a k-th carrier, and K – number of all pulses. Spectral density of this noise is proportional to the current value:

$$S_I = |2qI|. \tag{2.28}$$

# Chapter 2. Theoretical, experimental background and state of the art

As we can see, this type of noise is "white" as the thermal noise. The situation when shot noise is observed in a MOSFET happens not quite often at room temperatures. Usually it is dominated by thermal noise as well as by other components. Shot noise may appear in a FET structure as a sign of non-ohmic contacts of the device or gate leakage current. Also FETs demonstrate shot noise in a subthreshold mode[120]. In the above threshold mode of the FET sensor, where most of the biosensing experiments take place, white noise is usually dominated by low-frequency excess noise components such as generation-recombination or flicker noise (1/f) components.

Generation-recombination (GR) noise is introduced and named after corresponding dynamic processes in a semiconductor. The main origins of this type of noise are generation and recombination of charge carriers. The GR noise can be caused by following processes in the channel of the NW FET:

- Band-to-band generation and recombination

- Exchange of the carriers with shallow levels in the bandgap

- Generation-recombination of the carriers through deep levels

- Exchange processes with traps in the gate dielectric

Characteristics of GR noise contain information about the process, which caused this noise: characteristic time, depth of the level, capture cross-section [121]. Therefore, investigation of the GR component plays an important role in localizing and charactering the defects in semiconductor structures. Spectral density of the GR noise has a lorentzian shape with time constant, which corresponds to the relaxation time of the GR process:

$$S_{I}(\omega) = \frac{S_{I}(0)}{1 + \omega^{2}\tau^{2'}}$$

(2.29)

where  $S_I(0)$  – is the value of a plateau of the Lorentzian.  $S_I(0)$  is usually related to concentration of the carriers and recombination centers, which take part in the GR process [121], [122],  $\tau$  – is the time constant of a process. GR noise in MOSFETs as well as in NW FETs is investigated in a number of publications and books, because it can have different nature and contains information about intrinsic device structure [121], [123]–[125]. Another type of the low-frequency noise is the well-known flicker noise or 1/f noise. The most general definition of this type of noise introduces the flicker noise as a fluctuation of the material conductance with spectral density close to the inverse proportion to the frequency[126]:

$$S_I \sim \frac{I^{\beta}}{f^{\gamma}},\tag{2.30}$$

where f – is the frequency,  $\gamma$  – index close to 1, and  $\beta$  – is the index close to 2. The reason for such a general definition comes from a complex nature of the flicker noise. Flicker noise exists in many different systems and its origin still causes debates in scientific society. A lot of work has been devoted to the nature of flicker noise in MOSFETs [38], [108], [125], [127], [128]. Nowadays the three main models for flicker noise in semiconductors are considered: mobility fluctuations model[129], number fluctuation model[127] and the number and correlated mobility fluctuation model[130], which includes both approaches. We will not speak here about more fundamental mechanisms of flicker noise like dielectric polarization noise [131] or quantum 1/f noise [132], because in FET structures these components are usually hidden by more powerful mechanisms like mentioned above. However, it should be noted that it is possible to register dielectric polarization noise of the gate dielectric in 0D ISFET structures [133].

One of the first explanations of the flicker noise is the mobility fluctuations model. In 1969 Hooge proposed an empirical equation for description of the 1/f noise in homogenous samples[134]:

$$\frac{S_I}{I^2} = \frac{1}{N} \frac{\alpha_H}{f},\tag{2.31}$$

where I – is the current through the sample, N – is the quantity of charge carriers in the sample, f – frequency,  $\alpha_{H}$  – empirical constant, which is nowadays named after Hooge and is usually about 2x10<sup>-3</sup>. However it has been shown later, that the value of  $\alpha_{H}$  can vary[108] from 10<sup>-4</sup>-10<sup>-6</sup> for high-quality samples without defects to much higher than 2x10<sup>-3</sup> for the samples with higher concentration of the defects. Hooge's model explains empirical equation (2.31) as a result of the mobility fluctuations of charge carriers. Hooge's constant is dimensionless value, which allows comparing levels of noise in different devices and materials, regardless from nature of the objects.

An alternative model is interpreting of flicker noise as a superposition of number generation-recombination processes with time constant distributed by some rule. In 1955

McWhorter[135] considered a model, which describes many traps with spatial and energy distribution inside the semiconductor contributing to overall noise by their GR processes. Further, the McWhorter model was adopted for the case of MOSFETs [108], [136], [137] including the fact that most of the exchange processes take place between charge carriers of the channel and traps in the gate dielectric. The model assumes that the traps are spatially and energetically equally distributed in the gate dielectric. The spatial and energy distribution of the traps results in distribution of the probabilities for the carriers being captured onto the traps. Overall sum of the contributions from all of the traps gives the 1/f behavior of the spectral density. The concentration of the traps defines the level of the flicker noise [138]:

$$S_{VFB} = \frac{q^2 k T \lambda N_t}{W L C_{ox}^2 f'}$$

(2.32)

where  $N_t$  – is the concentration of the traps distributed by the energy in [cm<sup>-3</sup>eV<sup>-1</sup>],  $\lambda$  – is the inverse tunneling depth (about 0.1 nm) of the carrier into the gate dielectric:

$$\lambda = \frac{\hbar}{\sqrt{2m^*\phi_b}},\tag{2.33}$$

where  $\hbar$  – is the Planck's constant,  $m^*$  – is the effective mass of the carrier,  $\phi_b$  – is the height of the potential barrier between semiconductor and the gate dielectric. In the case of McWhorter model the spectral density of fluctuation of the flat band voltage is equal to the equivalent input noise [114]:

$$S_{V_{FB}} \approx S_U = \frac{S_I}{g_m^2} \tag{2.34}$$

where  $g_m$  – is the transconductance of the transistor (Eq. (2.13)),  $S_U$  – is the equivalent input noise of the transistor,  $V_{FB}$ .

Both McWhorter and Hooge models are combined in the model of number and correlated mobility fluctuations  $(\Delta N - \Delta \mu)$  [130], where both fluctuations of the mobility and the quantity of channel carriers are considered. Fluctuations of the drain current can be written in a form of exact differential[114]:

$$\delta I_d = \frac{\partial I_d}{\partial V_{FB}}\Big|_{\mu=const} \delta V_{FB} + \frac{\partial I_d}{\partial \mu}\Big|_{V_{FB}=const} \delta \mu, \qquad (2.35)$$

$$\delta I_d = g_m \delta V_{FB} \mp \alpha I_d \mu \delta Q_{ss}, \qquad (2.36)$$

where  $\delta Q_{ss}$  – is the fluctuation of the surface state charges,  $\alpha$  – is the parameter, which reflects sensitivity of the mobility to the surface state charges[139]. Eq. (2.36) contains relation between fluctuations of the flat band voltage fluctuations and current fluctuations. If we switch to the frequency representation:

$$\frac{S_I}{I^2} = \left(1 \pm \alpha \mu C_{ox} \frac{I_d}{g_m}\right)^2 \frac{g_m^2}{I^2} S_{VFB}.$$

(2.37)

Dividing of the Eq. (2.37) by square transconductance allows switching to the value of equivalent input noise, which can be measured experimentally:

$$S_U = \left(1 \pm \alpha \mu C_{ox} \frac{I_d}{g_m}\right)^2 S_{v_{FB}}.$$

(2.38)

Depending on the quality of the structures and the conductance type the parameter  $\alpha$  can be close to 0 as well as significantly large (up to 10<sup>4</sup> V s/C [139]). Its value determines role of the mobility fluctuations in the overall 1/f noise.

Usually under the conditions of real experiment, the flicker noise component of the spectra is measured as a function of different parameters like  $V_{FG}$ ,  $V_{BG}$ ,  $V_{DS}$ . Often there is a question in interpretation of the flicker noise origin, finding a proper model for its description in case of particular experiment. The information about the most appropriate description of 1/f noise may be extracted from dependence of the flicker noise on the carrier concentration in the channel, front and back gate voltages[127]. In case of the volume noise (Hooge model) equivalent input noise is changing in the proportionally to the gate voltage, whereas in the case of McWhorter model  $S_u$  is independence of the normalized current spectral density,  $\frac{S_I}{I^2}$ , as a function of  $\frac{g_m^2}{I^2}$ . If the dependence reflects proportionality, then according to (2.37) the model is applicable. However, with downscaling of the NW devices the flicker noise characteristics may deviate from the predicted nature due to discrete nature of the traps in the gate dielectric.

# Chapter 2. Theoretical, experimental background and state of the art

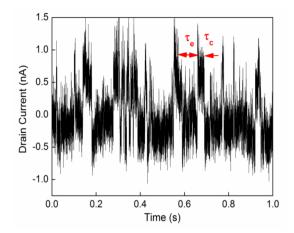

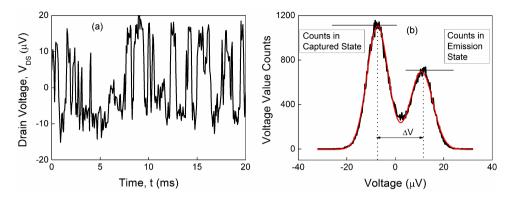

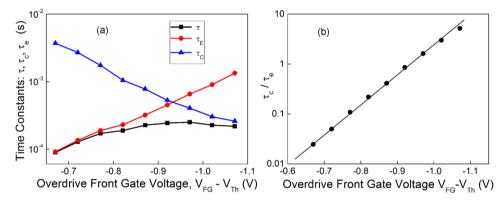

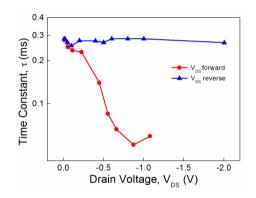

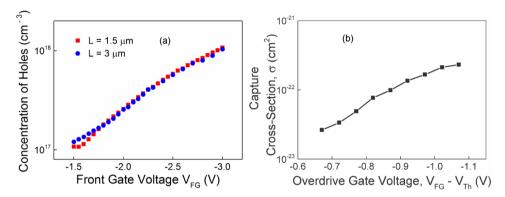

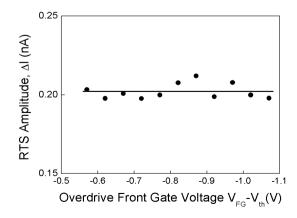

Miniaturization of the silicon devices, particularly NWs, leads to decreasing the effective gate surface area. For the case of the flicker noise generated by processes of carrier exchange with the gate dielectric, the decreasing the gate area leads to decreasing the amount of traps, which take part in the exchange processes. As it is shown in [140], miniaturization of the FET devices results in the breakdown of the 1/f dependence into superposition of lorentzian-shaped components. Further device miniaturization (down to the channel of submicron dimensions) may lead to a critical area of the gate, when only a single trap in the gate dielectric or channel influences the channel current. In such a case, we may observe switching of the current between two discrete levels, corresponding to the state with the occupied and unoccupied trap. Such type of noise is called random telegraph signal (RTS) noise, because it has two-level fluctuation of the device current (for example see Figure 2.6). Probability of the carriers being captured and released from a single trap is characterized by average capture and emission times,  $<\tau_c>$  and  $<\tau_e>$  (Figure 2.6). The probability of a carrier capture is  $1/\tau_c$  and the probability of carrier emission is  $1/\tau_e$ . A behavior of the capture and emission times in the case of a single trap is generally described by Shockley-Read-Hall (SRH) dynamics[140]. In this respect capture and emission times can be represented as:

$$\tau_c = \frac{1}{\sigma n v_{th}} \text{ and } \tau_e = \frac{1}{\sigma n_1 v_{th}}, \qquad (2.39)$$

where  $\sigma$  – is the capture cross section of the trap, n – is the carrier concentration,  $v_{th}$  - is the thermal velocity of the carriers,  $n_1$  – is the Shockley-Read-Hall factor of the trap occupancy, which equals concentration of the free carriers in the channel, when Fermi level coincides with the level of the trap. In fact the trap can be situated anywhere in the channel or in the gate dielectric. In the case of the gate dielectric the concentration of the carriers, n, should be considered taking into account tunneling of the carriers to the trap[141]. The tunneling drastically decreases the concentration of the carriers in close vicinity of the trap. According to (2.39) increasing of the capture time and thus decreasing of the capture probability. In addition, there are effects related to the fact that a trap may change its energy and capture cross-section after capturing a charge carrier. These effects are described in frame of the Coulomb blockade energy concept[142]–[144]. If the trap is located near the drain of the NW it may considerably modulate the channel conductivity [145].

Figure 2.6 Example of a drain current time trace containing RTS fluctuations. Red arrows indicate capture and emission time of the process.

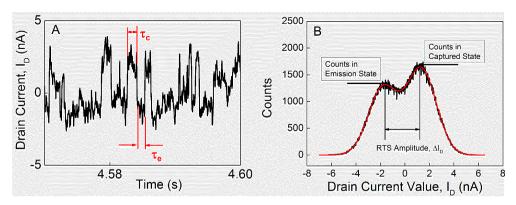

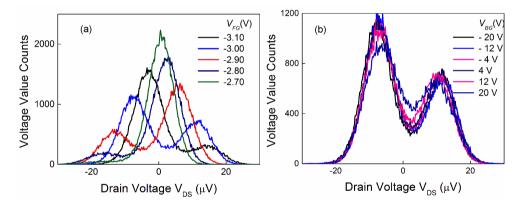

The RTS noise is generally an unwanted effect because it introduces a two- or more levels of the current, between which the drain current is randomly switching. Such a noise may hinder the useful signal in case of real-time biomolecules detection or in the case of extracellular investigation of neuronal cells. However, the useful signal can be distinguished from the RTS noise by the histogram of the time trace. RTS noise is a non-Gaussian process because of switching between two or more levels of current, but the value of current at each of the levels is distributed normally. Therefore, RTS histogram usually represents two or more Gaussian peaks corresponding to each of the current levels (see Figure 2.7). In real measurements, the useful signal is usually not a random process and thus its histogram should not have distinct separation of two Gaussian peaks like in Figure 2.7(B). Such a difference can be used as a verification procedure to distinguish if the measured signal is valid or not.

Figure 2.7 Time trace (A) of the drain current and its corresponding histogram (B) for the liquid-gated Si NW sample with length of 500 nm and the width of 100nm at  $V_{DS}$  = - 0.1 V, V<sub>G</sub> = - 0.9V and pH of the gating solution pH = 7.5. The image is adapted from [92].

The capture time is dependent on the concentration of the carriers (Eq. (2.39)) and thus on the gate voltage. In the case of strongly confined geometries like silicon-on-insulator (SOI) based devices, Si NWs and gate-all-around FETs the dependence of the capture time on the concentration of the carriers may deviate from the SRH behavior and can be much stronger function of *n* than Eq. (2.39) [146], [147]. We have used the capture time as a sensitive value for detection of surface potential of liquid-gated Si NW FET. Monitoring of the  $\tau_c$  instead of the drain current resulted in the increase sensitivity of Si NW FET device to the surface potential by a factor of 400%, because of a strong dependence of behavior of  $\tau_c$  on carrier concentration [92].

The spectral density of the RTS noise is represented by a Lorentzian-shaped component [148]. The time constant of a process is defined by capture and emission times:

$$\tau = \frac{\tau_c \tau_e}{\tau_c + \tau_e}.$$

(2.40)

The the plateau of the Lorentzian is defined by the RTS amplitude and the capture and emission times:

$$S_I(0) = 4 \frac{(\Delta I)^2 \tau^2}{\tau_c + \tau_e},$$

(2.41)

where  $\Delta I$  – is the RTS amplitude, which can be determined from Figure 2.7(B). 40

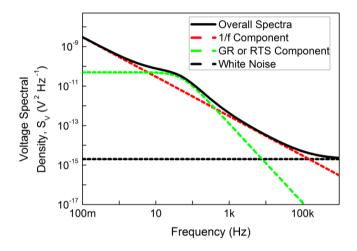

As it was mentioned in subsection 2.2.2, the spectral density of the signal fluctuations is an additive value, if the noise sources are not correlated between each other. Therefore an observed spectra are represented by a combination of all mentioned types of noise. In the Figure 2.8 an example of superposition of three types of noise is presented.

Figure 2.8 Spectral density of the drain-source voltage fluctuations (solid line) and its components (dashed lines).

Different noise mechanisms in the sample are often investigated separately. Therefore, corresponding noise spectra component should be discriminated from the overall spectra by means of fitting or by finding of the FET mode where other noise mechanisms are suppressed and the component under is most pronounced. For simplified fitting of the noise spectra, we have developed a special software, which will be described later.

The overall noise is important when the real measurements are performed, because in this case the useful signal is compared to the whole noise of the measurement system. The knowledge about the noise components and their behavior allows improving fabrication technology and finding operation modes in such a way that the overall noise of the device is reduced and signal-to-noise ratio is optimal. It should be noted that for obtaining optimized signal-to-noise ratio of the FET biosensor we should be aware of the signal level, which we are going to detect. Therefore, in the next subsection we will discuss the main principles of electrogenic cell functioning and the main properties of the cell/FET interface.

## 2.3 Electrogenic cells on FETs

## 2.3.1 Introduction

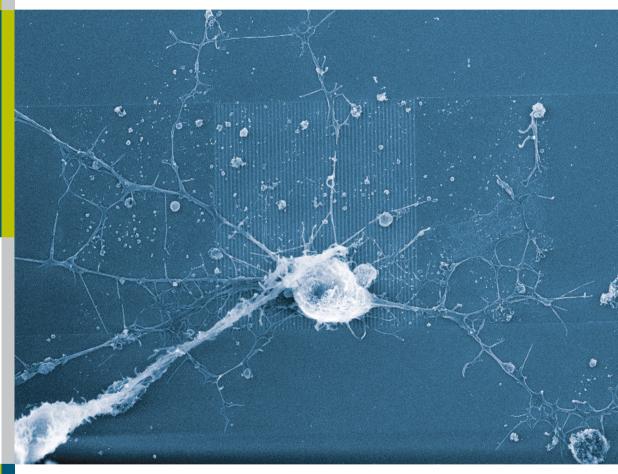

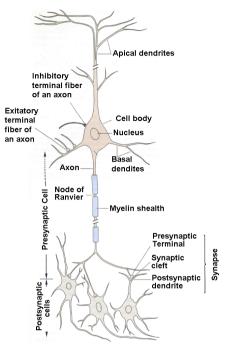

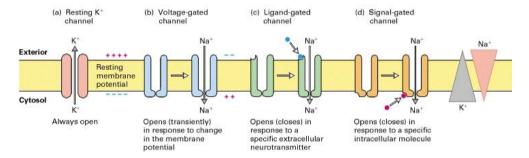

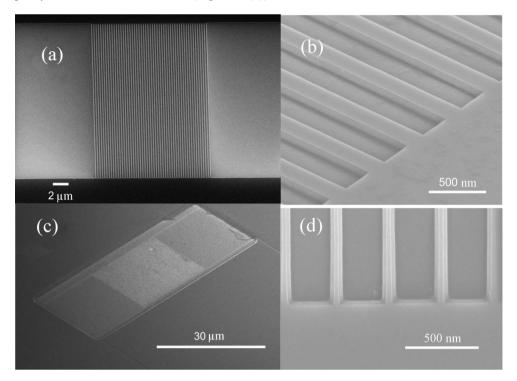

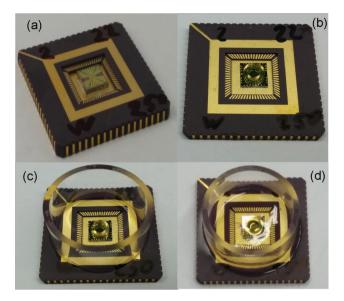

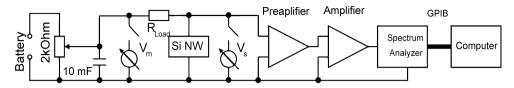

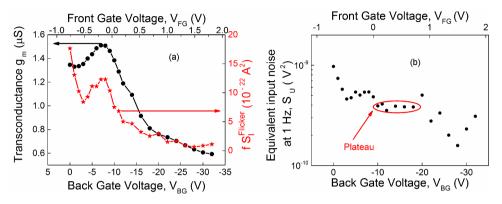

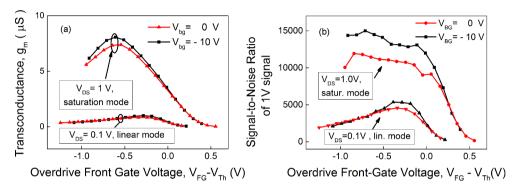

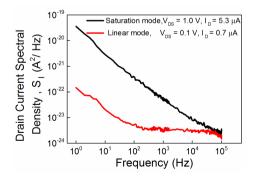

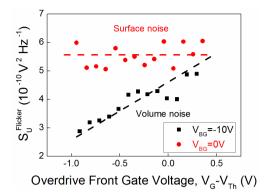

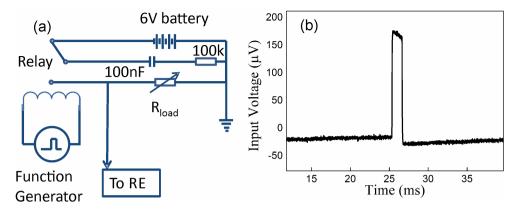

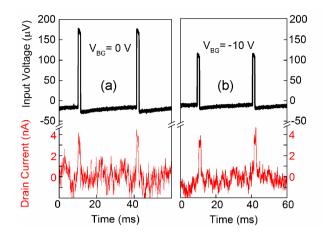

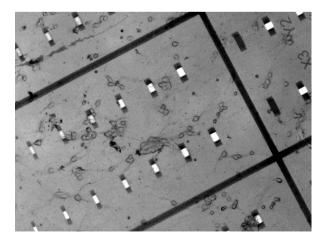

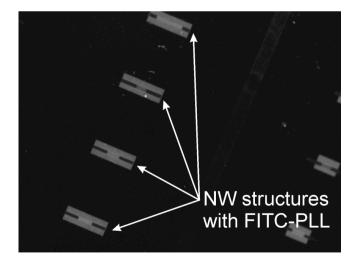

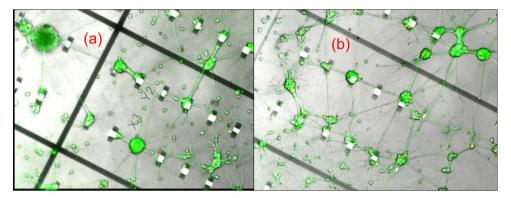

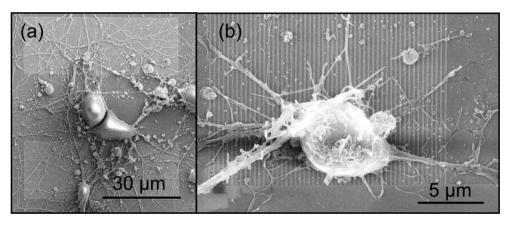

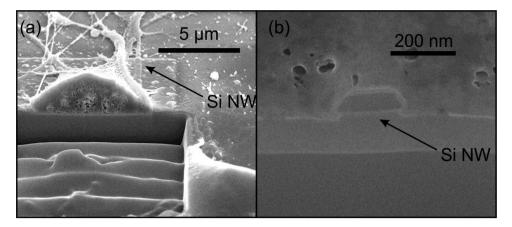

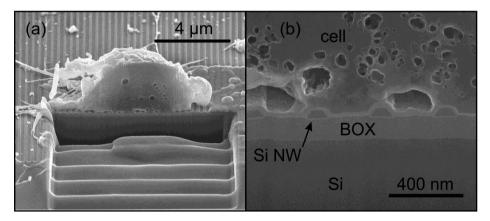

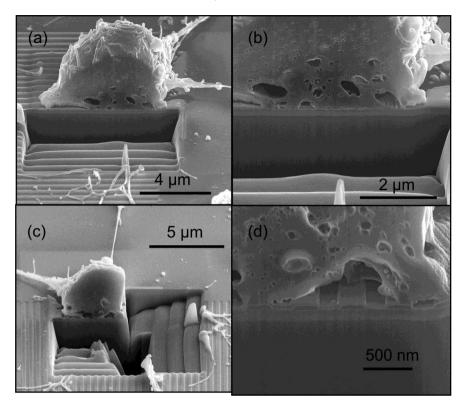

The building block of the biological systems are cells. They are diverse in their functionality and are often organized into functional modules which are repeated within the organism[149]. The most complex biological system in the organism is the nervous system and its elementary unit is the neuronal cell. A tremendous progress of the neuroscience in the last decades was achieved due to investigation of the neuronal cell activity and pathways in vivo as well as in vitro using novel ultimate methods including nanotechnology[150]. One of the most demanded methods of the neuronal cell investigation – is the extracellular monitoring of the cell activity, because it is not harmful and allows characterizing cellular system without any influence on it. Therefore, extracellular investigation of neuronal cells activity is of great interest from point of view fundamental biophysics as well as large variety of applications such as monitoring of electrical communication within neuronal networks, transmission paths of ionic channels, the use as biosensor to monitor pharmaceutical agents, pollutants, etc.